## RESEARCHSPACE@AUCKLAND

### http://researchspace.auckland.ac.nz

#### ResearchSpace@Auckland

#### **Copyright Statement**

The digital copy of this thesis is protected by the Copyright Act 1994 (New Zealand).

This thesis may be consulted by you, provided you comply with the provisions of the Act and the following conditions of use:

- Any use you make of these documents or images must be for research or private study purposes only, and you may not make them available to any other person.

- Authors control the copyright of their thesis. You will recognise the author's right to be identified as the author of this thesis, and due acknowledgement will be made to the author where appropriate.

- You will obtain the author's permission before publishing any material from their thesis.

To request permissions please use the Feedback form on our webpage. <a href="http://researchspace.auckland.ac.nz/feedback">http://researchspace.auckland.ac.nz/feedback</a>

#### General copyright and disclaimer

In addition to the above conditions, authors give their consent for the digital copy of their work to be used subject to the conditions specified on the <u>Library Thesis Consent Form</u> and <u>Deposit Licence</u>.

#### **Note: Masters Theses**

The digital copy of a masters thesis is as submitted for examination and contains no corrections. The print copy, usually available in the University Library, may contain corrections made by hand, which have been requested by the supervisor.

# Towards Efficient Execution of a GALS MoC Based System Level Language

### Muhammad Nadeem

Supervisors: Dr. Morteza Biglari-Abhari Prof. Zoran Salcic

A thesis submitted in partial fulfilment of the requirements for the degree of

Doctor of Philosophy in Electrical and Electronic Engineering,

The University of Auckland

## **Abstract**

Embedded systems include a broad range of electronic systems, from household appliances to safety critical systems such as medical systems, automotive electronics and avionics. Due to growing complexity of the applications, these systems consist of a number of computational intensive units running concurrently. They also interact with each other and with environment, repeatedly reading inputs, doing computations and responding appropriately. These computational units may have different response times; hence, they may need to run concurrently at different speeds. These systems may be considered as GALS (Globally Asynchronous Locally Synchronous), which typically consist of a collection of components that execute concurrently and communicate using possibly slow or unreliable channels. SystemJ is a system level programming language based on GALS model of computation allowing the asynchronous coupling of synchronous reactive modules at the top level, which execute at different speeds. It extends Java with Esterel-like constructs for the synchronous concurrency and reactivity, and CSP-like constructs for the asynchronous concurrency. SystemJ targets a large range of heterogeneous embedded systems that combine data-intensive and control-dominated computations (heterogeneous) in addition to synchronous and asynchronous concurrency.

Although, the problem of modeling complex systems has largely been solved by raising level of abstraction, there is still need for efficient execution platforms to realize such applications. While, there have been efforts towards supporting heterogeneous applications, they primarily focused on the reactive part of applications. In summary, developing architectural support for heterogeneous embedded applications has been the main focus of this research.

This thesis proposes improvements to some existing architectures as well as developing new architectures that make use of the formal underlying structure of the language to achieve higher execution efficiency in the GALS paradigm. These architectures execute control and data-driven operations along with asynchronous and synchronous concurrent processes in an efficient way. Our novel solutions range from extensions to a single CPU architecture to multiprocessor architectures, all while considering computational demands and resource constraints. We started with the deployment of Java Optimized Processor (JOP) to execute SystemJ programs compiled to Java and improved it by extending its architecture to include the reactive features. We suggested novel architectures which efficiently execute the SystemJ programs compiled by sep-

arating control and data-operations on a single core by embedding control operations inside the data-operation represented in Java by translating them to custom bytecodes. We refined this approach by providing two separate modes of execution for control and data-oriented operations. This approach is further extended to multiprocessor architecture to speed up the execution and meet the computational demands required by high-end embedded systems. We experimentally evaluated all proposed architectures to validate their effectiveness. Better performance, lower code density and resources usage have been achieved compared to previous approaches for SystemJ execution, thus proving its suitability for heterogeneous embedded applications.

To my parents and family

# Acknowledgements

First and foremost I offer my sincerest gratitude to my supervisors, Dr. Morteza Biglari-Abhari and Prof. Zoran Salcic, who have supported me thoughout my thesis. Their time, expertise, support and guidance have been invaluable and appreciated. I attribute the level of my Doctor of Philosphy degree to their encouragement and effort and without them this thesis, too, would not have been completed or written. The joy and enthusiasm they had for the research was contagious and motivational for me, even during tough times.

My time at University of Auckland was made enjoyable in large part due to the many friends and groups that became a part of my life. I am grateful for time spent with roommates, friends, and many other people.

Last but not least, my deepest thanks to my parents and family for their continuous support throughout these years. Their understanding and support ecouraged me to do my best in Ph.D research.

# **Contents**

| 1 | Intr | oductio | n                                                      | 1  |

|---|------|---------|--------------------------------------------------------|----|

|   | 1.1  | Charac  | eteristics of Modern Embedded Systems                  | 2  |

|   |      | 1.1.1   | Computation Power                                      | 2  |

|   |      | 1.1.2   | Interaction with the Environment                       | 3  |

|   |      | 1.1.3   | Real-time Processing                                   | 4  |

|   |      | 1.1.4   | Distributed Nature                                     | 4  |

|   |      | 1.1.5   | Globally Asynchronous Locally Synchronous Systems      | 5  |

|   | 1.2  | Model   | ling GALS System                                       | 6  |

|   |      | 1.2.1   | Modelling with Traditional Languages                   | 6  |

|   |      | 1.2.2   | Modelling with System Level Design Languages           | 7  |

|   |      | 1.2.3   | Modelling with Synchronous Languages                   | 7  |

|   |      | 1.2.4   | Modelling with Asynchronous Languages                  | 8  |

|   |      | 1.2.5   | Modelling with SystemJ: A System Level Design Language | 8  |

|   | 1.3  | Motiva  | ation                                                  | 9  |

|   | 1.4  | Resear  | rch Contributions                                      | 11 |

|   | 1.5  | Thesis  | Organization                                           | 13 |

| 2 | Syst | emJ Ov  | verview                                                | 17 |

|   | 2.1  | The Sy  | ystemJ MoC                                             | 17 |

|   | 2.2  | The Sy  | ystemJ Entities                                        | 18 |

|   |      | 2.2.1   | System                                                 | 18 |

|   |      | 2.2.2   | Clock-domains                                          | 18 |

|   |      | 2.2.3   | Reactions                                              | 19 |

xvi CONTENTS

|   | 2.3  | Systen | nJ Objects                                                          | 19 |

|---|------|--------|---------------------------------------------------------------------|----|

|   |      | 2.3.1  | Signals                                                             | 19 |

|   |      | 2.3.2  | Channels                                                            | 20 |

|   |      | 2.3.3  | Java Objects                                                        | 21 |

|   | 2.4  | The Sy | ystemJ Kernel Statements                                            | 21 |

|   |      | 2.4.1  | Synchronous Kernel Statements Descriptions                          | 21 |

|   |      | 2.4.2  | Asynchronous Kernel Statements Descriptions                         | 24 |

|   | 2.5  | Systen | nJ Example Program                                                  | 26 |

|   | 2.6  | The Sy | ystemJ Compilation Approaches                                       | 27 |

|   |      | 2.6.1  | Library Based Compilation                                           | 27 |

|   |      | 2.6.2  | AGRC Approach                                                       | 28 |

|   |      | 2.6.3  | Standard Java Code                                                  | 29 |

|   |      | 2.6.4  | Separation of Control and Data-computations                         | 30 |

|   | 2.7  | The Sy | ystemJ Execution Platforms                                          | 35 |

|   |      | 2.7.1  | Execution Platforms for Standard Java Approach                      | 36 |

|   |      | 2.7.2  | Execution Platforms for Separation of Control and Data-computations | 27 |

|   | 2.0  | G      | Approach                                                            | 37 |

|   | 2.8  | Summ   | ary                                                                 | 42 |

| 3 | Java | and Sy | ystemJ Execution                                                    | 43 |

|   | 3.1  | Java V | 'irtual Machine                                                     | 43 |

|   |      | 3.1.1  | JVM Instruction Set                                                 | 44 |

|   |      | 3.1.2  | Class File Format                                                   | 46 |

|   |      | 3.1.3  | JVM Run-time Data Areas                                             | 47 |

|   | 3.2  | JVM I  | mplementations                                                      | 50 |

|   |      | 3.2.1  | Interpreter                                                         | 50 |

|   |      | 3.2.2  | Just-In-Time Compilation                                            | 50 |

|   |      | 3.2.3  | Batch Compilation                                                   | 51 |

|   |      | 3.2.4  | Hardware Implementation                                             | 51 |

|   | 3.3  | Java P | rocessors                                                           | 51 |

CONTENTS xvii

|   | 3.4  | Java O  | ptimized Processor-JOP                | 56 |

|---|------|---------|---------------------------------------|----|

|   |      | 3.4.1   | JOP Overview                          | 57 |

|   |      | 3.4.2   | Instruction Set                       | 57 |

|   |      | 3.4.3   | Translation of Bytecodes to Microcode | 59 |

|   |      | 3.4.4   | Memory Organization                   | 60 |

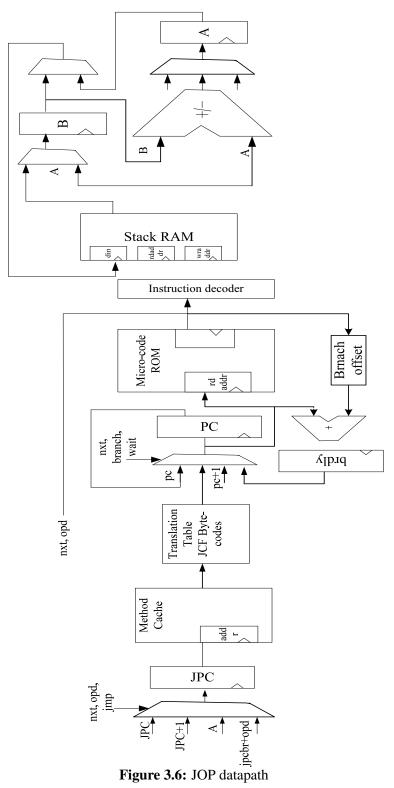

|   |      | 3.4.5   | JOP Datapath                          | 61 |

|   |      | 3.4.6   | Boot Up                               | 62 |

|   |      | 3.4.7   | Extending JOP                         | 64 |

|   | 3.5  | JOP as  | SystemJ Execution Platforms           | 64 |

|   | 3.6  | JOP Pe  | erformance Evaluation for SystemJ     | 66 |

|   |      | 3.6.1   | Benchmarks                            | 66 |

|   |      | 3.6.2   | Hardware Platform                     | 66 |

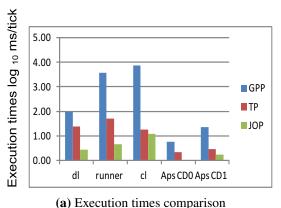

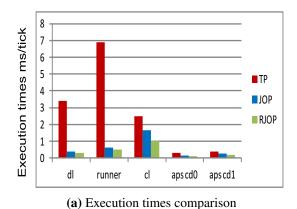

|   |      | 3.6.3   | Execution Time Comparison             | 67 |

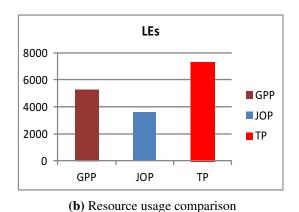

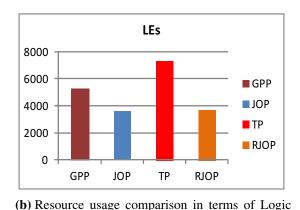

|   |      | 3.6.4   | Resource Usage Comparison             | 68 |

|   | 3.7  | Limita  | tions of SystemJ Execution on JOP     | 68 |

|   | 3.8  | Reactiv | ve-JOP - RJOP                         | 70 |

|   |      | 3.8.1   | Related Work                          | 70 |

|   |      | 3.8.2   | Reactivity and RJOP                   | 70 |

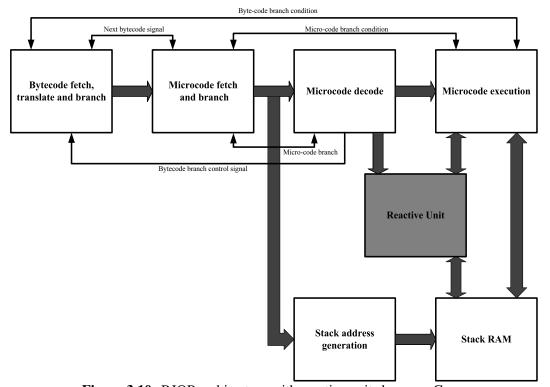

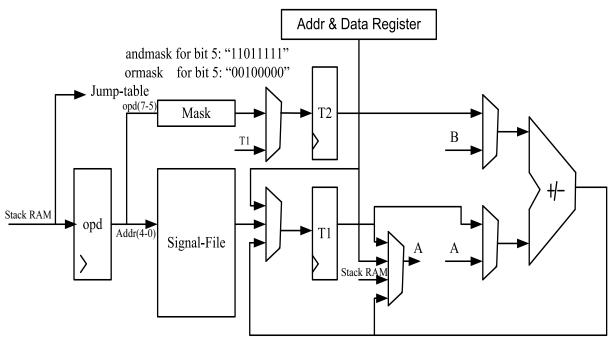

|   |      | 3.8.3   | RJOP Architecture                     | 71 |

|   |      | 3.8.4   | Compiler Modifications                | 73 |

|   |      | 3.8.5   | Reactive Unit                         | 75 |

|   | 3.9  | Perfori | mance Evaluation                      | 75 |

|   | 3.10 | Summa   | ary                                   | 77 |

| 4 | CAI  | LS-JOF  |                                       | 79 |

| 4 |      | _       |                                       |    |

|   | 4.1  |         | action                                | 80 |

|   | 4.2  |         | encies in the Existing Approaches     | 80 |

|   | 4.3  |         | P                                     | 81 |

|   |      | 4.3.1   | TP-JOP Design flow                    | 81 |

|   |      | 432     | TP-IOP Architecture                   | 82 |

xviii CONTENTS

|   |      | 4.3.3  | Compiler Modification                                 |

|---|------|--------|-------------------------------------------------------|

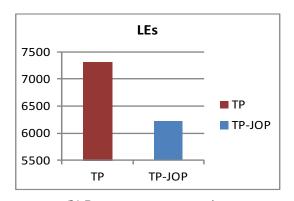

|   |      | 4.3.4  | TP-JOP Performance Evaluation                         |

|   | 4.4  | Limita | tions of TP-JOP                                       |

|   | 4.5  | GALS-  | -JOP                                                  |

|   | 4.6  | GALS-  | -JOP Compilation and Execution Strategy               |

|   |      | 4.6.1  | AJT-Assembly to Java Translator                       |

|   |      | 4.6.2  | GALS-JOP Example Code                                 |

|   |      | 4.6.3  | JTG - Jump-Table Generator                            |

|   | 4.7  | GALS-  | -JOP Architecture                                     |

|   |      | 4.7.1  | Memory Organization                                   |

|   |      | 4.7.2  | GALS-JOP Instruction Set                              |

|   |      | 4.7.3  | Bytecode Extension                                    |

|   |      | 4.7.4  | Microcode Extension                                   |

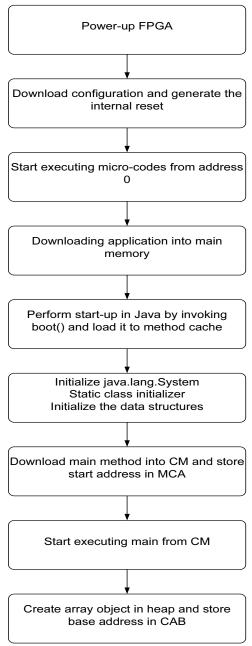

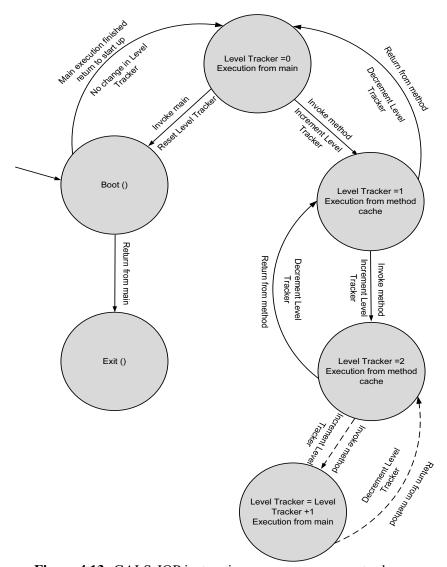

|   |      | 4.7.5  | GALS-JOP Start-up and Program Flow                    |

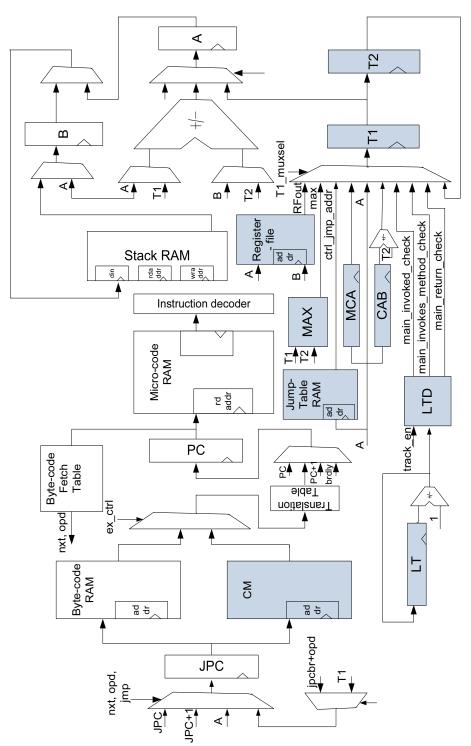

|   |      | 4.7.6  | GALS-JOP Data-path                                    |

|   | 4.8  | Experi | mental Results                                        |

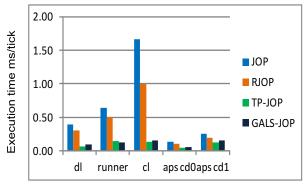

|   | 4.9  | GALS-  | -JOP Performance Evaluation                           |

|   | 4.10 | Summa  | ary                                                   |

| 5 | JOP  | -Plus  | 111                                                   |

|   | 5.1  | CRCF   | Instruction Set Architecture                          |

|   | 5.2  | Improv | ring GALS-JOP Approach                                |

|   | 5.3  | JOP-Pl | us - A Refined Approach                               |

|   | 5.4  | Compi  | lation and Execution Strategy                         |

|   | 5.5  | JOP-Pl | us Significant Features                               |

|   |      | 5.5.1  | CRCF Memory Concept                                   |

|   |      | 5.5.2  | Preserving SystemJ Compiler                           |

|   |      | 5.5.3  | Two Virtual Processors on a Single Physical Processor |

|   |      | 5.5.4  | Efficient Implementation of Data-computations         |

|   |      | 5.5.5  | No Jump-table                                         |

CONTENTS xix

|      | 5.5.6   | Efficient implementation of CRCF Data Structure |

|------|---------|-------------------------------------------------|

|      | 5.5.7   | Efficient Invoking of JCF                       |

|      | 5.5.8   | Resource Sharing                                |

| 5.6  | System  | nJ Code Example                                 |

| 5.7  | Memor   | ry Organization                                 |

|      | 5.7.1   | Main Memory                                     |

|      | 5.7.2   | CRCF Program Memory                             |

|      | 5.7.3   | Register-file                                   |

|      | 5.7.4   | CRCF Data Memory                                |

|      | 5.7.5   | Registers                                       |

| 5.8  | Start-u | p and Control Flow                              |

|      | 5.8.1   | CRCF Program Memory Initialization              |

|      | 5.8.2   | Instruction Fetch                               |

|      | 5.8.3   | Invoking JCF                                    |

|      | 5.8.4   | Return to CRCF                                  |

| 5.9  | Transla | ation-table Extension                           |

| 5.10 | JOP-Pl  | lus Architecture                                |

|      | 5.10.1  | CRCF Instruction Set Support                    |

|      | 5.10.2  | Bytecode Extension Summary                      |

|      | 5.10.3  | Extended Microcode Summary                      |

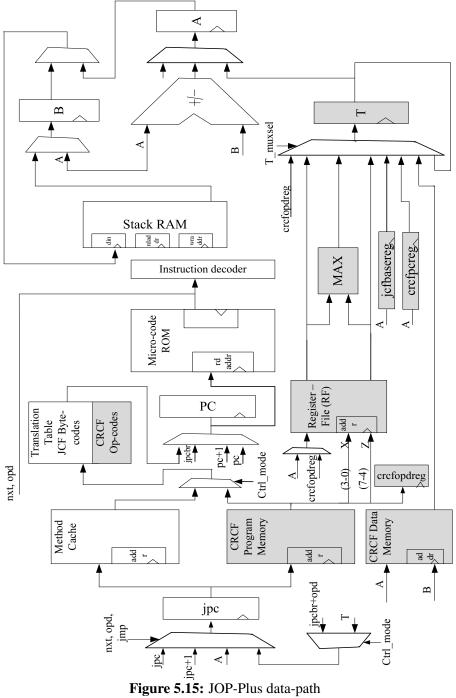

|      | 5.10.4  | JOP-Plus Data-path                              |

|      | 5.10.5  | Instruction Execution Overview                  |

|      | 5.10.6  | CRCF Instruction Set Execution                  |

|      | 5.10.7  | Communication with the Environment              |

| 5.11 | Experi  | mental Results                                  |

|      | 5.11.1  | Benchmarks                                      |

|      | 5.11.2  | Experimental Set up                             |

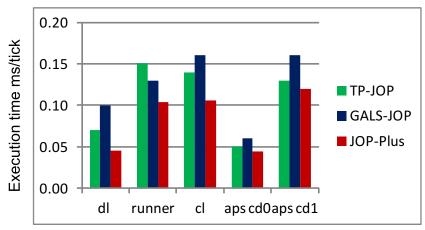

|      | 5.11.3  | Performance Comparison                          |

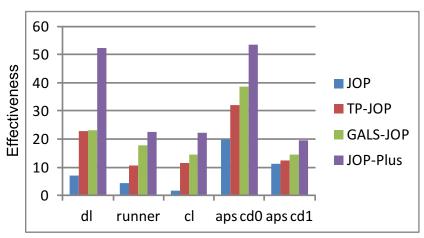

|      | 5.11.4  | Effectiveness                                   |

| 5.12 | Summa   | ary                                             |

XX CONTENTS

| 6 | GAI | LS-CM  | P                                     | 149 |

|---|-----|--------|---------------------------------------|-----|

|   | 6.1 | Unipro | ocessor system shortcomings           | 150 |

|   | 6.2 | Harnes | ssing the performance                 | 151 |

|   | 6.3 | Embed  | lded Multiprocessors                  | 152 |

|   |     | 6.3.1  | Heterogeneous Multiprocessors         | 152 |

|   |     | 6.3.2  | Homogeneous Multiprocessors           | 153 |

|   | 6.4 | GALS   | -CMP                                  | 154 |

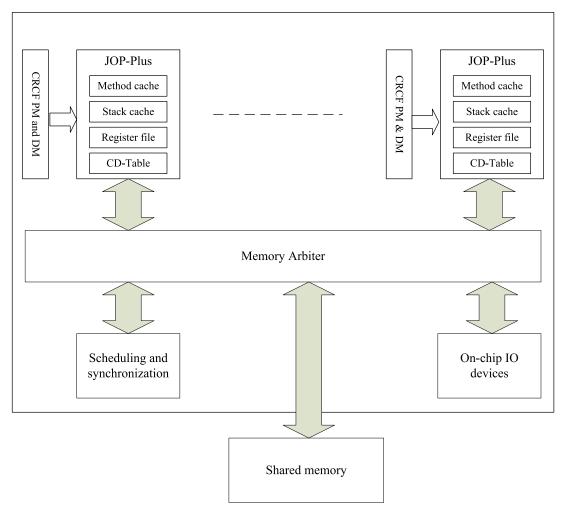

|   | 6.5 | GALS   | -CMP System                           | 155 |

|   |     | 6.5.1  | Interconnect Fabric                   | 157 |

|   |     | 6.5.2  | Arbitration                           | 157 |

|   |     | 6.5.3  | Distribution of Processing            | 158 |

|   |     | 6.5.4  | Inter Clock-domain Communication      | 158 |

|   |     | 6.5.5  | Accessing Shared Channel Objects      | 158 |

|   | 6.6 | GALS   | -CMP Architecture                     | 159 |

|   |     | 6.6.1  | Memory Organization                   | 159 |

|   |     | 6.6.2  | JOP-Plus Core                         | 160 |

|   |     | 6.6.3  | CD-table                              | 161 |

|   | 6.7 | GALS   | -CMP Compilation and Execution flow   | 162 |

|   |     | 6.7.1  | SystemJ Example                       | 162 |

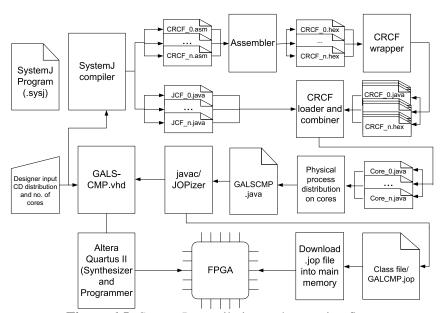

|   |     | 6.7.2  | Compilation Flow                      | 164 |

|   |     | 6.7.3  | Boot Sequence                         | 167 |

|   |     | 6.7.4  | Instruction Fetch                     | 167 |

|   |     | 6.7.5  | Transfer of Control to/from JCF       | 168 |

|   | 6.8 | Perfor | mance Evaluation                      | 168 |

|   |     | 6.8.1  | Experimental Setup                    | 168 |

|   |     | 6.8.2  | Benchmarks                            | 169 |

|   |     | 6.8.3  | Performance Parameters Definitions    | 169 |

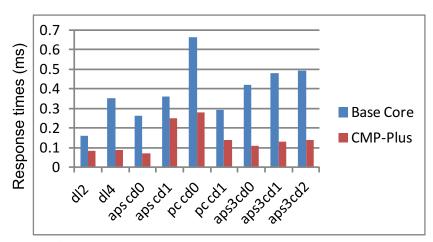

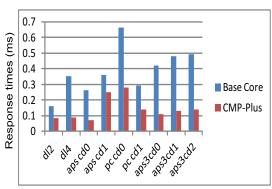

|   |     | 6.8.4  | Reponse Time Comparison               | 170 |

|   |     | 6.8.5  | Application Execution Time Comparison | 171 |

|   | 6.9 | Summ   | ary                                   | 171 |

| 7 Conclusion and Future Work 17          | 13         |

|------------------------------------------|------------|

| 7.1 Overview                             | 13         |

| 7.2 Results Discussion                   | <b>'</b> 4 |

| 7.3 Main Contributions                   | 7          |

| 7.4 Recommendations for Further Research | 19         |

| References 18                            | 23         |

XXII CONTENTS

# **List of Figures**

| 1.1  | ASIC prototypes and verification on applications destined for the embedded systems market vs the traditional PC market | 2  |

|------|------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Exampe of GALS application: track controlling                                                                          | 6  |

| 1.3  | Thesis structure                                                                                                       | 14 |

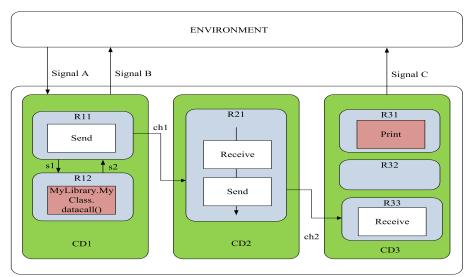

| 2.1  | A graphical equivalent of SystemJ example program                                                                      | 21 |

| 2.2  | SystemJ example program                                                                                                | 27 |

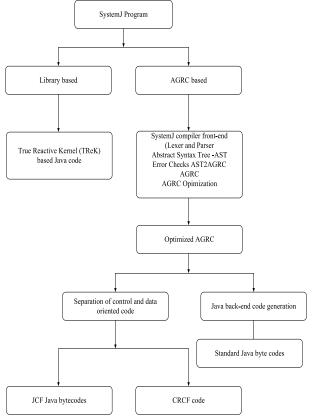

| 2.3  | Compilation strategies for SystemJ programs                                                                            | 28 |

| 2.4  | Simple SystemJ code showing syntax                                                                                     | 29 |

| 2.5  | The single threaded pure Java code generated by the AGRC based SystemJ compiler for SystemJ example given in 2.2       | 31 |

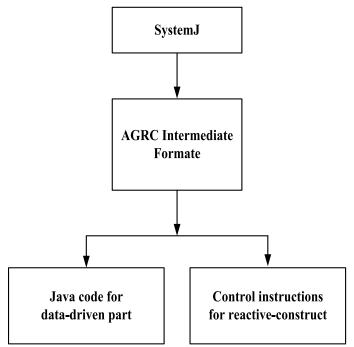

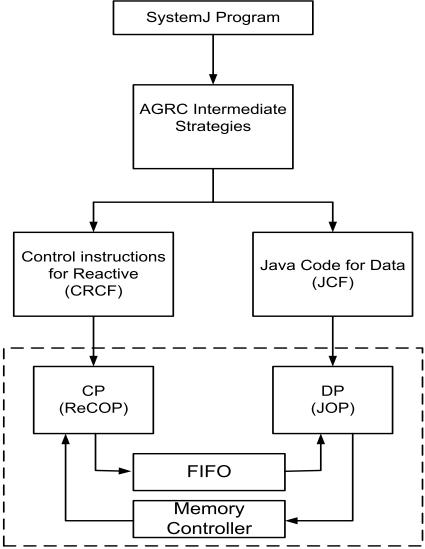

| 2.6  | A SystemJ compilation approach separating control from data-computations                                               | 32 |

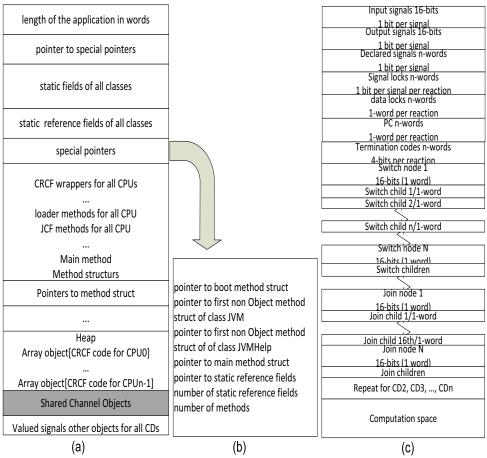

| 2.7  | CVM data structure                                                                                                     | 33 |

| 2.8  | SystemJ compilation to mixture of Java and assembly                                                                    | 35 |

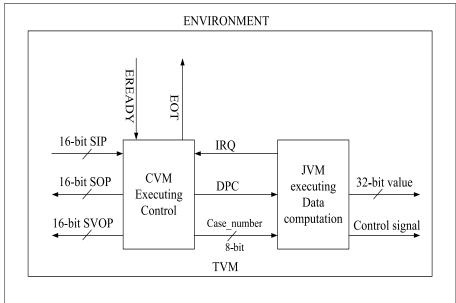

| 2.9  | TVM execution platform with communication interface between virtual machine and with the environment                   | 38 |

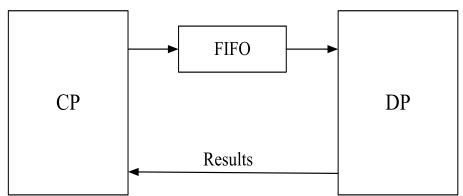

| 2.10 | TP execution platform with FIFO as communication interface between control and data processor                          | 40 |

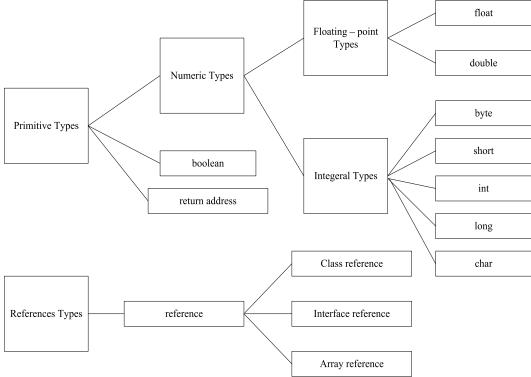

| 3.1  | Java Data types                                                                                                        | 45 |

| 3.2  | Class file format showing all components in orderly fashion                                                            | 47 |

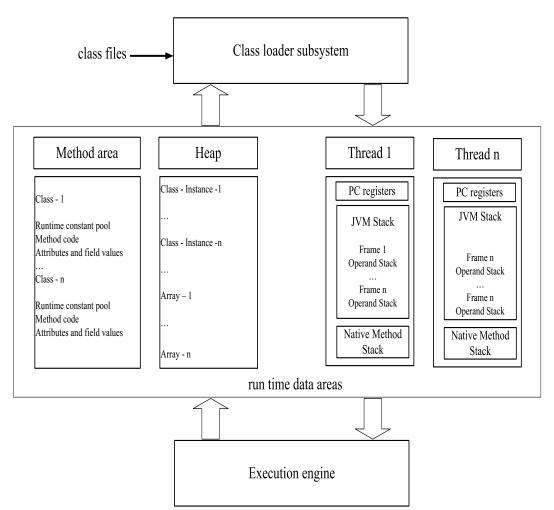

| 3.3  | The internal architecture of the JVM                                                                                   | 48 |

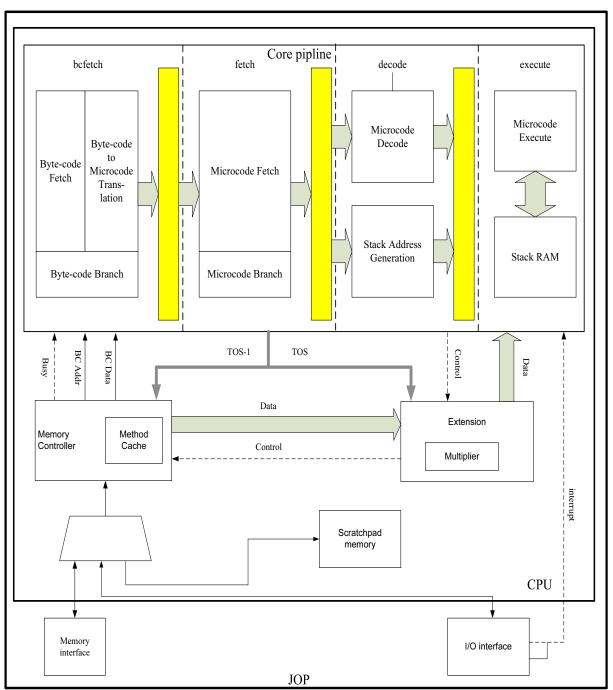

| 3.4  | JOP architecture                                                                                                       | 58 |

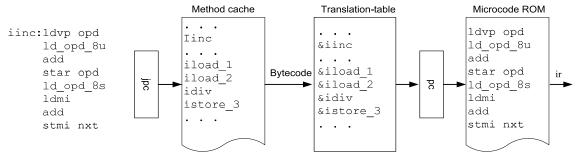

| 3.5  | Bytecode to microcode mapping example and microcode fetching mechanism                                                 | 60 |

xxiv LIST OF FIGURES

| 3.6 | JOP datapath                                                                                                                           | 63  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------|-----|

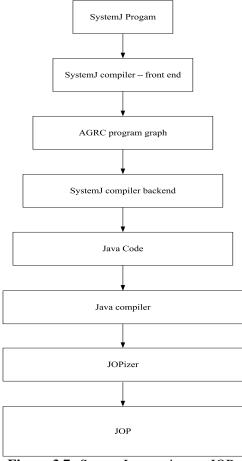

| 3.7 | SystemJ execution on JOP                                                                                                               | 65  |

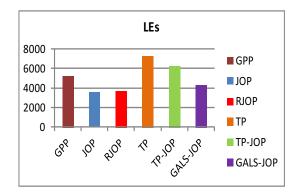

| 3.8 | JOP performance comparison                                                                                                             | 68  |

| 3.9 | Mapping of <i>emit</i> bytecode to microcode                                                                                           | 72  |

| 3.1 | 0 RJOP architecture with reactive unit shown as Grey                                                                                   | 73  |

| 3.1 | 1 SystemJ program compiled targeting JOP and RJOP                                                                                      | 74  |

| 3.1 | 2 Detailed architecture of the reactive unit of RJOP                                                                                   | 76  |

| 3.1 | 3 JOP performance comparison                                                                                                           | 77  |

| 4.1 | Abstract view of TP-JOP design flow and communication                                                                                  | 82  |

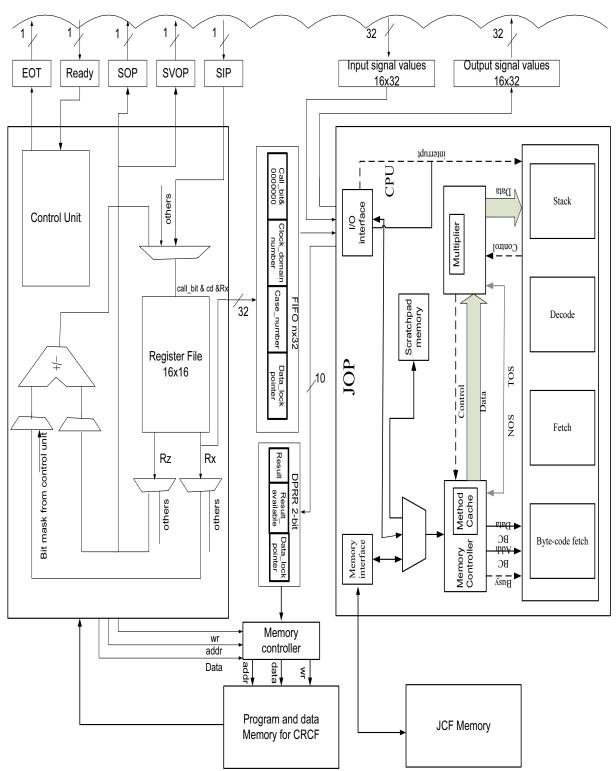

| 4.2 | TP-JOP architecture consisting of ReCOP and JOP, communication interface components FIFO and DPRR, memories and CRCF memory controller | 84  |

| 4.3 | TP-JOP example code in Java representing data-computation                                                                              | 85  |

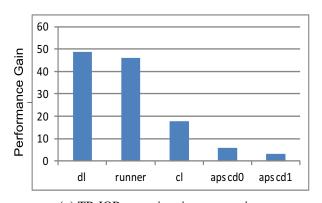

| 4.4 | TP-JOP performance evaluation                                                                                                          | 86  |

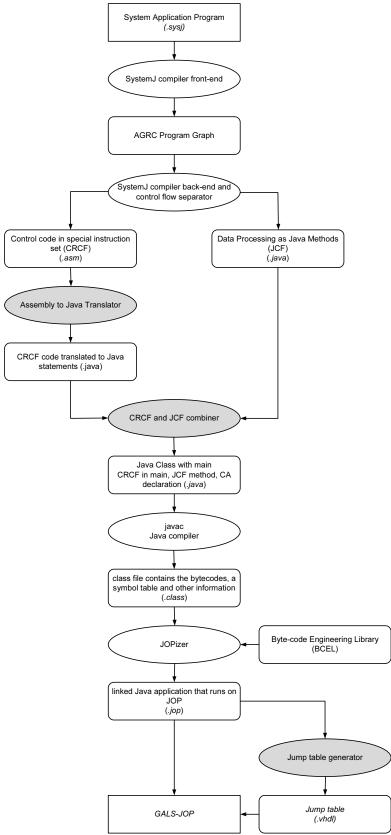

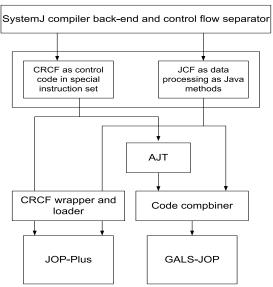

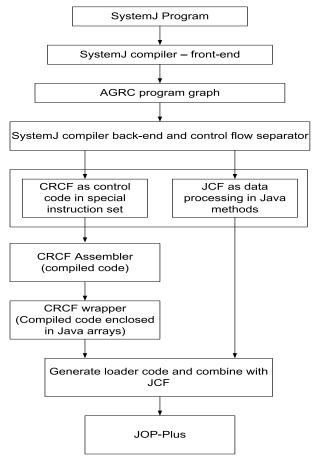

| 4.5 | GALS-JOP design flow                                                                                                                   | 91  |

| 4.6 | SystemJ example code                                                                                                                   | 94  |

| 4.7 | SystemJ program compiled by separating the CRCF and JCF represented as assembly instructions and Java methods, respectively            | 94  |

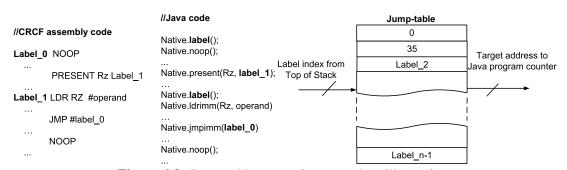

| 4.8 | Example code ready for execution on GALS-JOP generated by AJT tool translating the CRCF instructions to Java                           | 95  |

| 4.9 | Jump-table generation procedure illustration                                                                                           | 96  |

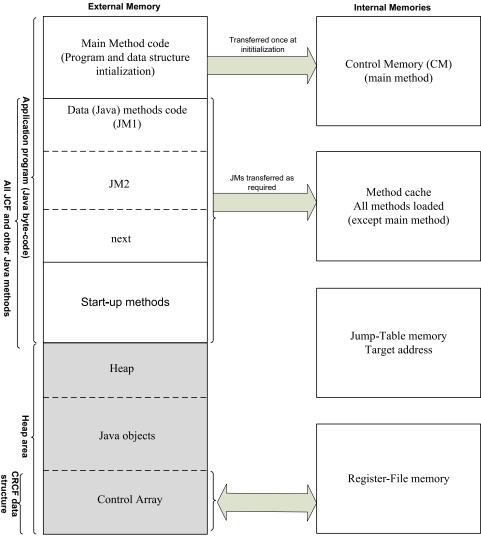

| 4.1 | 0 GALS-JOP memory organization                                                                                                         | 97  |

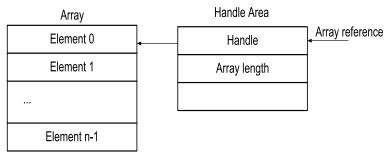

| 4.1 | 1 Accessing array elements from the heap                                                                                               | 100 |

| 4.1 | 2 GALS-JOP start-up and execution flow                                                                                                 | 103 |

| 4.1 | 3 GALS-JOP instruction source management scheme                                                                                        | 105 |

| 4.1 | 4 GALS-JOP data-path                                                                                                                   | 107 |

| 4.1 | 5 GALS-JOP performance results                                                                                                         | 108 |

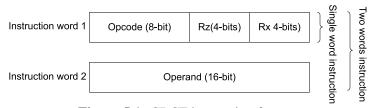

| 5.1 | CRCF instruction format                                                                                                                | 112 |

| 5.2 | JOP-Plus design flow                                                                                                                   | 113 |

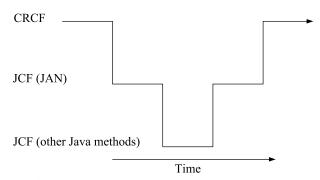

| 5.3 | Control flow of SystemJ program                                                                                                        | 116 |

LIST OF FIGURES XXV

| 5.4  | JOP-Plus compilation and execution strategy                                                                                                     | 117 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.5  | SystemJ compilation example separating CRCF from JCF with data-computations decomposed into methods targeting JOP-Plus                          |     |

| 5.6  | Java array object initialized with CRCF compiled code                                                                                           | 122 |

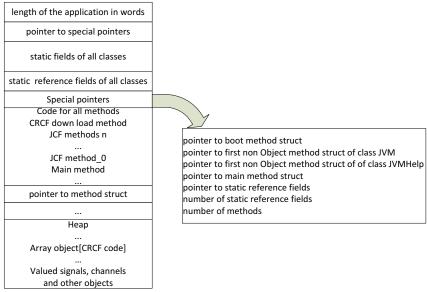

| 5.7  | JOP-Plus memory organization                                                                                                                    | 123 |

| 5.8  | Main memory organization                                                                                                                        | 124 |

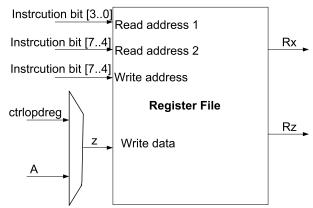

| 5.9  | CRCF Register-File with data input mux                                                                                                          | 125 |

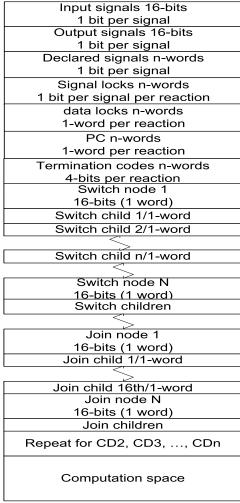

| 5.10 | CRCF data memory                                                                                                                                | 126 |

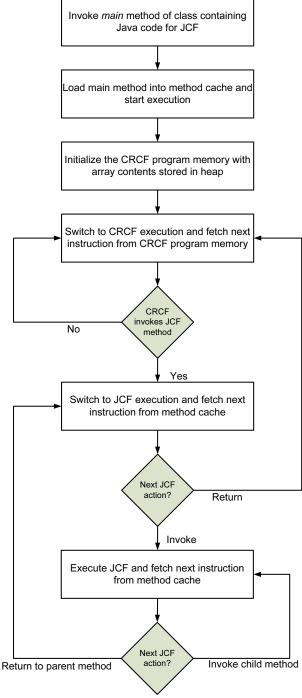

| 5.11 | Start up and program execution flow                                                                                                             | 129 |

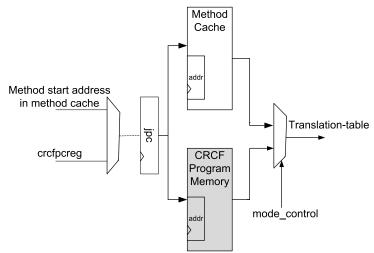

| 5.12 | Switching between CRCF and JCF                                                                                                                  | 131 |

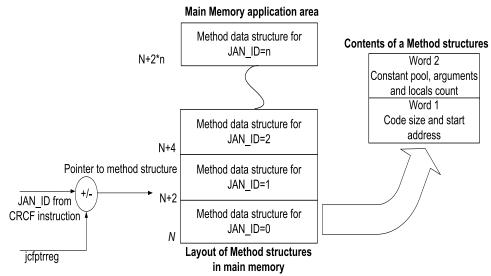

| 5.13 | JAN organization in main memory                                                                                                                 | 132 |

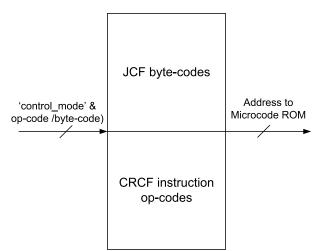

| 5.14 | Translation-table extension                                                                                                                     | 134 |

| 5.15 | JOP-Plus data-path                                                                                                                              | 139 |

| 5.16 | JOP-Plus comparison with other implementations                                                                                                  | 144 |

| 5.17 | Comparison of effectiveness                                                                                                                     | 146 |

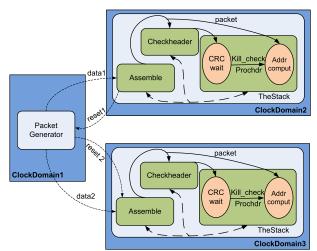

| 6.1  | GALS-CMP architecture                                                                                                                           | 156 |

| 6.2  | GALS-CMP memory organization (a) main meory layout (b) is a snapshot of                                                                         |     |

|      | special pointer area of main memory (c) layout of CRCF data memory                                                                              | 160 |

| 6.3  | Pictorial representation of SystemJ example                                                                                                     | 162 |

| 6.4  | SystemJ code for Asynchronous Protocol Stack                                                                                                    | 163 |

| 6.5  | SystemJ compilation and execution flow                                                                                                          | 164 |

| 6.6  | SystemJ code compiled by separating data-computation and control in the form of JCF Java code and CRCF assembly code                            | 165 |

| 6.7  | CRCF machine code encapsulated in arrays                                                                                                        | 165 |

| 6.8  | Java code to be executed on a core comprising of code for downloading CRCF machine code into CRCF program memory and JCF code representing Java |     |

|      | action nodes                                                                                                                                    | 166 |

| 6.9  | Allocation of clock-domains to cores in main method of the class                                                                                |     |

| 6.10 | Comparison of clock-domain response time                                                                                                        | 170 |

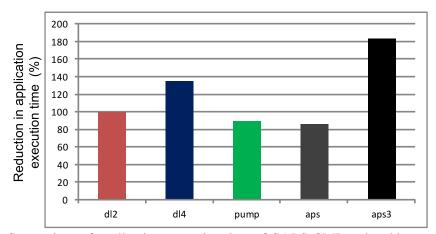

| 6.11 | Comparison of application execution time of GALS-CMP and and base core JOP-Plus                                                                 | 171 |

xxvi LIST OF FIGURES

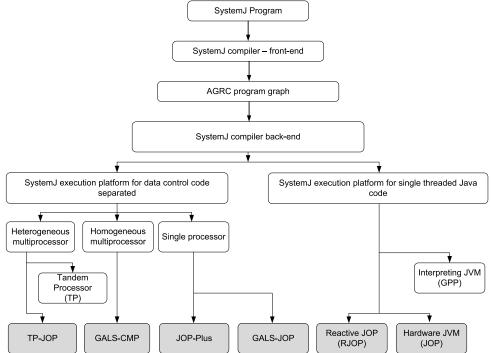

| 7.1 | SystemJ program compilation and execution approaches. The shaded areas rep- |     |

|-----|-----------------------------------------------------------------------------|-----|

|     | resent the approaches suggested in this thesis                              | 174 |

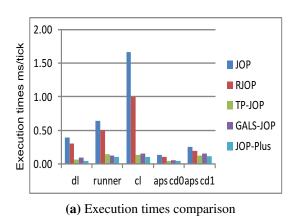

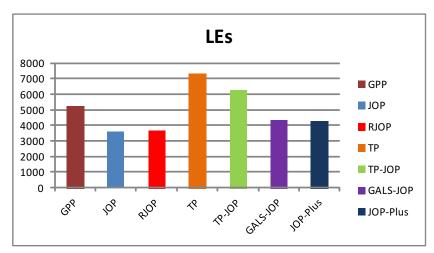

| 7.2 | Performance comparison                                                      | 175 |

| 7.3 | Resource usage comparison for all execution approaches                      | 177 |

# **List of Tables**

| 2.1 | Control processor instructions and their description                                            | 41  |

|-----|-------------------------------------------------------------------------------------------------|-----|

| 3.1 | Features of experiment set                                                                      | 67  |

| 3.2 | Signal manipulation methods in single threaded Java code                                        | 69  |

| 3.3 | List of extended bytecodes specific to RJOP                                                     | 71  |

| 3.4 | Register transfer description of RJOP specific microcodes                                       | 72  |

| 3.5 | Translation of SystemJ reactive constructs into Java statements                                 | 74  |

| 4.1 | Translation of CP instructions to Java methods representing user specific bytecodes             | 92  |

| 4.2 | List of bytecodes introduced to support CRCF                                                    | 101 |

| 4.3 | Description of extended microcodes incorporated to implement the functionality of new bytecodes | 102 |

| 5.1 | CRCF assembly instruction translated to Java and compiled to bytecodes                          | 114 |

| 5.2 | Mapping multiple assembly instruction to a single bytecode                                      | 114 |

| 5.3 | Summary of branch instructions                                                                  | 119 |

| 5.4 | CRCF execution specific registers                                                               | 128 |

| 5.5 | CRCF instructions categorized based on their functionality                                      | 136 |

| 5.6 | Extended bytecodes                                                                              | 137 |

| 5.7 | Extended microcodes summary                                                                     | 138 |

XXVIII LIST OF TABLES

# List of Abbreviations and Acronyms

AGRC Asynchronous Graph Code

AJT Assembly to Java Translator

ASIC Application Specific Integrated Circuit

ATT Average Tick Time

APS Asynchronous Protocol Stack

BCL Bytecode Engineering Library

CA Control Array

CAB Control Array Base

CD Clock-domain

CISC Complex Instruction Set Computer

cl combinational lock

CM Control Memory

CMP Chip Multiprocessor

CP Control Processor

CRCF Concurrency and Reactive Control Flow CSP Communicating Sequential Processes

CVM Control Virtual Machine

dl demoloop

DM Data Memory

DP Data Processor

DSP Digital Signal Processing

EOT End of Tick

ER Environment Ready FIFO First In First Out

FPGA Field Programmable Gate Array

GALS Globally Asynchronous Locally Synchronous

GPP General Purpose Processor

JAN Java Action Node

XXX LIST OF TABLES

JCF Java Control Flow

JOP Java Optimized Processor

JPC Java Program Counter

JTG Jump Table Generator

JVM Java Virtual Machine

J2ME Java 2 Platform, Micro Edition

LE Logic Element

LT Level Tracker

LTD Level Tracker Decoder

MCA Main Continuous Address

MoC Model of Computation

PC Program Counter

PM Program Memory

RAM Random Access Memory

ReCOP Reacive CO-Processor

RISC Reduced Instruction Set Computer

ROM Read Only Memory

RF Register File

RJOP Reactive Java Optimized Processor

SOC System-on-Chip

TOS Top Of Stack

TP Tandem Processor

TVM Tandem Virtual Machine

VLIW Very Large Instruction Word

WCET Worst Case Execution Time

WCRT Worst Case Reaction Time

# **Chapter 1**

## Introduction

We are living in a world which is evolving at a faster pace than ever before. This is for a large part, happening since we stepped into the digital revolution marking the beginning of the information age changing the analog mechanical and electronic technology into digital technology. Central to this never-ending era is the mass production of the digital logic circuits which is at the heart of the computer. Almost every modern home and workplace contains many computers. Some of these computers are immediately recognizable as laptops and desktop PCs, but many are hidden within intelligent devices that use software to implement functionality. These computers are embedded systems.

An embedded system is a combination of computer hardware and/or software, and perhaps additional mechanical or other parts, designed to perform a dedicated function [1]. The cellular smart phones and tablets are couple of recent examples which have widespread use and significant impact on our daily lives. There are almost no areas of modern technology which could do without embedded systems. They appear in all areas of industrial applications and process control, in cars, in home appliances, entertainment electronics, cellular phones, video and photo cameras, and many more places. Embedded systems are becoming increasingly prevalent in everyday life. The growth rate in embedded systems is more than 10% per annum and it is forecast that by 2020 there will be over 40 billion devices (5 to 10 embedded devices per person on earth) worldwide. Today 20% of the value of each car is attributed to embedded electronics and this will increase to an average of 35-50% by 2020. The market for embedded computer systems, which already generates more than US\$1 trillion in revenue annually, will double in size over the next four years, according to a report released by research company IDC [2].

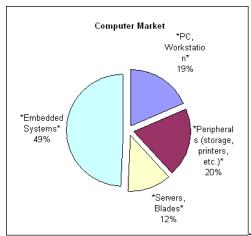

The data in Figure 1.1 shows that the embedded computers dominate the computer market and have already surpassed traditional PC market share in terms of number of units.

2 Introduction

**Figure 1.1:** ASIC prototypes and verification on applications destined for the embedded systems market vs the traditional PC market

## 1.1 Characteristics of Modern Embedded Systems

The embedded systems are deployed to execute a wide range of ever changing applications. The nature of application is a ever changing phenomenon and new applications keep on emerging, including many that have not yet been envisioned, with features which were never the characteristics of the traditional embedded system. Recently, application complexity has increased significantly and traditional design approaches are unable to cope with these demands.

## 1.1.1 Computation Power

The semiconductor technology has grown rapidly resulting in larger die sizes and shrinking feature sizes largely surfing on Moore's law [3]. This enormous rise in computation power has enabled the designer to realize the computational intensive applications on the embedded systems that were not possible a few years ago. Compute-intensive is a term that applies to any computer application that demands a lot of computation. Previously, embedded systems were limited in computational capability, memory size, and power consumption, the focus of the research was to make the best use of the limited system resources. The system performance issues, such as execution time, were traded off with system resources. Modern embedded devices are usually equipped with significant computation capabilities. With more available computational capability in embedded system devices, and more complicated requirements demanding more intensive computation, the most critical design concerns are changing in some important application domains. Now, it is possible to produce chips with much more logic tremendously increasing the computational power available in the appliances. But to realize this performance, we need to apply smarter methods to improve system execution time.

#### 1.1.2 Interaction with the Environment

Modern embedded systems interact with the environment more than ever making them reactive in nature, which are different from transformational and interactive systems.

#### **Transformational Systems**

The transformational systems, on providing the input, compute the output and then stop. These systems acquire some data as input at the beginning of execution and produces some data as a result, on termination. A compiler is a typical example of transformational system.

### **Interactive Systems**

The interactive systems communicate with the environment at their own speed. They get the input from the environment and compute the results. The environment has to wait for the result before entering the input. An operating system is a typical example of interactive system.

#### **Reactive Systems**

The reactive systems [4] are also interactive but slightly differ in the sense that they have to respond at a speed dictated by the environment and cannot make it wait. The system reads the inputs and performs the computation and makes the result available before the next set of inputs is available. The examples of such systems are lift controller and vehicles automation systems. The reactive systems can be divided into two categories: data-dominated and control-dominated. The reaction time is less important for the data dominated systems, which contains intense data computations, operating on samples arriving in regular intervals from the environment. On the other hand, the control-dominated systems do not perform intensive data computation. The systems which have mix of control and data are termed as heterogeneous systems. Criticality, parallelism and determinism are some of the most essential features of a reactive system [5]. The reactive systems are usually modeled using synchronous languages which express reactive control flow patterns in a concise manner, with a clear semantics that imposes deterministic program behavior under all circumstances.

The examples of typical target areas for such systems are: automotive (e.g. engine controllers, anti-lock brake controllers); consumer electronics (e.g. microwave ovens, digital cameras, compact disc players); plant control (e.g. robots, plant monitors, airplane control systems, missile guidance systems) and telecommunications (e.g. telephone switches, cellular phones).

4 Introduction

### 1.1.3 Real-time Processing

Real-time systems are those systems in which the correctness of the system depends not only on the logical results of computation but also the time at which the results are produced [6]. A real-time embedded system that must meet at least one hard deadline is called a hard realtime embedded system or a safety-critical real-time embedded system. Safety-critical systems are those systems whose failure could result in loss of life, significant property damage, or damage to the environment. Missing a hard deadline means a total system failure. If no hard deadline exists, then the system is called a soft real-time embedded system. The design of a hard real-time system is fundamentally different from the design of a soft real-time system. While a hard real-time computer system must sustain a guaranteed temporal behavior under all specified load and fault conditions, it is permissible for a soft real-time embedded system to miss a deadline occasionally. Timing correctness requirements in a real-time system arise because of the physical impact of the controlling system's activities upon its environment. The most common timing constraints for tasks are periodic, aperiodic, and sporadic. A task is an execution path through address space. A periodic task is one that is activated every T units. The deadline for each activated instance may be less than, equal to, or greater than the period T. An aperiodic task is activated at unpredictable times. A sporadic task is an aperiodic task with the additional constraint that there is a minimum interarrival time between task activations. Realtime systems need a time-predictable execution platform so that the Worst Case Execution Time (WCET) can be estimated statically. Predictable system is one in which timing requirements can be guaranteed a priori. WCET of a computational task is the maximum length of time the task could take to execute on a specific hardware platform. Knowing worst-case execution times is of prime importance for the schedulability analysis of hard real-time systems. The distributed nature of the system makes it easier to design but wiriting applications for such systems becomes harder.

#### 1.1.4 Distributed Nature

New application areas of embedded systems such as networked computing are composed of several computing units thus making them distributed systems in nature. There are various reasons to distribute embedded systems for example: the high performance enabled by the use of several computation units for a better response time, sometimes the geographical delocalization of the system elements or the replication of systems for fault tolerance. A distributed system consists of a collection of autonomous components, connected through a network and distribution middleware, which enables them to coordinate their activities and to share the resources of the system, so that users perceive the system as a single, integrated computing facility. The software part may run as concurrent processes on different processors which may have multiple

points of failure and control. The systems can also be decomposed into smaller specific units carrying out a particular task efficiently and run concurrently offering different services at the same time. They may run at the same or different clock speed in which case they are termed as multi-clock systems. Applications modeling for such distributed systems is hard but they are easy to test and maintain.

## 1.1.5 Globally Asynchronous Locally Synchronous Systems

A wide range of embedded systems today consist of a number of computational intensive units running concurrently. They also tend to interact with each other and with the environment making them reactive by repeatedly reading inputs, doing computations and generating outputs. These computational units have different response times; hence, they may need to run concurrently at different speeds avoiding the higher operating frequencies which result in reduced power consumption. These systems are called GALS (Globally Asynchronous Locally Synchronous) systems [7] and typically consist of a collection of sequential, deterministic components that execute concurrently and communicate using slow or unreliable channels. Hence, a GALS system consists of two or more processes (or processors) running concurrently and asynchronously, i.e., they run at unrelated clock speeds, at the top-level. Each of these asynchronous processes can themselves consist of one or more processes all running concurrently but synchronously, i.e., in lockstep with the parent process clock speed. GALS paradigm is used both in software and hardware. In software GALS systems, different processes run concurrently whereas in hardware GALS systems different physical processing modules run concurrently. The GALS paradigm unites the advantage of synchronous designs (for determinism) and asynchronous designs (for flexibility) to obtain more efficient and powerful system descriptions and implementations. Examples of GALS applications are distributed control applications, industrial process controllers, aircraft and automobile controllers, ATM networks and multi-agent robotics etc.

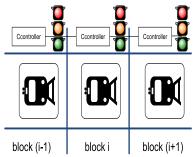

Let us consider the example of a track controller controlling the tranportation of multiple trains onto the track divided into multiple blocks as shown in Figure 1.2. The trains can enter and exit these blocks. The trains cannot enter any block without permission and cannot exit any block without indication. The safety requirements demand that no two trains can be present in the same block at any time. The trains can move from one block to another. The problem is to design appropriate controllers for each block. The solution of such a problem is a GALS system having distributed network of controllers with one controller per block. Each controller is locally reactive and can sense entry/exit of trains and exchanges signals with the train on the block. The adjacent controllers can talk to each other for controlling entry/exit of trains.

6 Introduction

Figure 1.2: Exampe of GALS application: track controlling

## 1.2 Modelling GALS System

Modelling GALS applications typically requires the use of non-standard control flow constructs, concurrency and exception handling. The technological advancements certainly opens up vast possibilities for innovation, but only provided that the attendant complexity can be managed. It should be kept in mind that if product complexity is measured on a linear scale, Moore's law. In order to avoid exponentially increasing development costs, it is suggested that overall productivity of designed functions must itself improve exponentially on the time axis. Given the importance of embedded systems, it is important to overcome bottlenecks represented by current development practices in the face of increasing complexity [3].

## 1.2.1 Modelling with Traditional Languages

Among the programming languages, C, C++ and Java are the most commonly used in embedded systems and are familiar to designers. Java's expressive power is comparable to C++; it is a much simpler language, which reduces the difficulty of program analysis and optimization. It has the edge over C due to standard language and library support for concurrency. Its treatment of arrays permits better static and dynamic error checking than is conveniently feasible in C and C++. Using Java's widespread adoption by the science and engineering community promises a large base of support in the form of compilers, debuggers, development environments, and class libraries. Java's higher level of abstraction allows for increased programmer productivity. It is relatively secure and has support for dynamic loading of new classes, component integration and reuse, which provides platforms to support application portability as well as distributed applications. But, these traditional languages lack high level parallelism and use of asynchronous parallelism typically leads to non-deterministic program behavior with respect to time and functionality [8]. It is hard to certify the correctness of the programs modelled in such languages which is a must for safety critical systems. The lack of statements for modelling reactive control structures and frequent occurrence of context switching to support concurrency reduces their efficiency.

### 1.2.2 Modelling with System Level Design Languages

Modelling GALS applications using traditional languages is complex, time consuming and expensive thus leading to large designer productivity gap. Thus, we need to move to higher level of abstraction in order to manage the ever increasing complexity and heterogeneity in the embedded systems. The new design challenges can be tackled by moving to the higher level of abstraction, called system level. The designer specifies a model at the highest available level of abstraction which can be translated to a lower level subsequently. The lower levels such as behavior, register-transfer, circuit and physical (in descending order) differ from each other by their execution semantics often referred to as a model of computation (MoC) and the modeling details [9]. For example, the MoC for the logic level may be thought as including Boolean equations to describe the data-path and Finite State Machines (FSMs) to describe the control. The MoC of the RTL may be a combination of FSMs with data-path [10] or as a micro-program to describe the register transfer level operations. The semantics of the behavioral level has often been that of discrete event systems [9]. The system level distinguish itself from the lower levels of abstractions by providing separation of computation from communication, mix of a range of semantics or models of computation, behavioral hierarchy, support for exceptions and exception handling, mix of data-dominated and control-dominated processing and support for formal verification. The system level approach provides an abstract way to capture many important features such as modularity, hierarchy and concurrency, which can be, both behavioral and structural, external communication between the modeled system and its environment and, finally, communication between concurrent processes within the designed system. The use of system level design languages is vital as it enables us to specify the model at an abstract, system level, and reduce productivity gap and time-to-market pressure.

SystemC [11], SystemVerilog [12], SpecC [13] are examples of system level design languages which provide an abstract way to model embedded systems. These languages use a well-known syntax with powerful constructs, enabling the modelling and simulation of complex systems. But, they are informal languages as they are not based on formal mathematical model of computation and do not follow formal semantic rules. It is hard to prove the correctness of designs modelled using these languages which is an essential property of the embedded systems thus making them less suited to model such systems. Although a subset of these languages can be formally described but they are unable to describe complex heterogeneous systems [8].

## 1.2.3 Modelling with Synchronous Languages

The synchronous languages [14] such as Esterel [15], lustre [16], signal [17], statecharts [18], sml [19] synccharts [20], argos [21] and SR [5] are system level design languages with synchronous semantics. Esterel is imperative, while *lustre* and *signal* are declarative in style; *state*-

8 Introduction

charts and argos are graphical languages that allow one to program by constructing hierarchical automata. They support control flow constructs and express it in a user friendly manner. They have simple formal model and are based on synchrony hypothesis, which states in essence that a system responds in zero time to environmental requests [15]. The key advantage of synchronous languages is that the synchronous approach has a rigorous mathematical semantics which allows the programmers to develop critical software faster and easier. But, synchronous languages show poorly when performing data computation and communicating asynchronously.

### 1.2.4 Modelling with Asynchronous Languages

The asynchronous languages (also called multi-clock languages) such as CSP [22], OCCAM [23] and ADA [24] are capable of handling concurrency as well as asynchronous communication but they suffer from same drawback of poor data handling. Communicating Sequential Processes (CSP) is a formal language for describing patterns of interaction in concurrent systems. It is a member of the family of mathematical theories of concurrency known as process algebras, or process calculi. OCCAM [23] is built on CSP [22] and shares many of its features. ADA is an extension of PASCAL and other languages. It is capable of handling data computation unlike other asynchronous language but is an informal language.

Due to inability of system level design languages to model multi-clock heterogeneous systems, the productivity gap remains there which requires a way to model such complex systems with ease and quickly. An ideal programming language should have the capability of efficiently handling intensive data computation, concurrency and asynchronous communication.

## 1.2.5 Modelling with SystemJ: A System Level Design Language

SystemJ [25, 26] is a system level programming language based on the Globally Asynchronous Locally Synchronous (GALS) model of computation and allows the asynchronous coupling of synchronous reactive modules at the top level, which execute at different speeds. It extends Java with Esterel-like [15] constructs for the synchronous concurrency and reactivity, and CSP-like [22] constructs for the asynchronous concurrency. The Java has been used in the past for writing reactive programs such as PureSR [27], Java-Time [28], Jester [29] and Junior [30] which are the reactive extensions of Java. SystemJ goes one step further and we view SystemJ as an ideal environment for specifying, modelling, implementing and formally verifying GALS based embedded systems.

SystemJ targets a large range of heterogeneous embedded systems that combine data-intensive and control-dominated computations in addition to synchronous and asynchronous concurrency. SystemJ is based on the synchrony hypothesis which makes the assumption that the computer is

1.3 Motivation 9

infinitely fast, each reaction is instantaneous and atomic, dividing time into a sequence of discrete instants, different reactions cannot interfere with one another, and a system's reaction to an input appears at the same instant as the input. The synchrony hypothesis is a generalization of the synchronous model used for digital circuits where each reaction must be finished during one clock *tick*. The perfect synchrony paradigm of synchronous languages considers the computation of reactions to be infinitely fast, so that the reaction appears at the same point of time when the action requests for it. This is achieved by an idealized view where the execution of most statements does not require time. Consumption of time must be explicitly programmed: every atomic statement consumes either none or exactly one unit of a logical time. Hence, by the semantics of these languages, all threads run synchronously to each other, since they automatically synchronize at the next time consuming statement.

Our work focuses on the SystemJ language, which combines the data-computation with control and asynchronous communication to model the complex and heterogeneous multi-clock embedded systems.

### 1.3 Motivation

SystemJ is a system level design language which models applications targetting Globally Asynchronous Locally Synchronous (GALS) heterogeneous systems. SystemJ models the control computations using a combination of both the synchronous and the asynchronous model of computations. SystemJ consists of asynchronous processes running concurrently at individual speeds at the top level, similar to CSP, while each of these asynchronous processes may consist of one or more synchronous processes running in lock step, similar to Esterel. SystemJ uses Java to describe data computations because of its powerful constructs for traditional sequential programming. A system described using SystemJ language communicates with the environments through the signals. GALS MoC implements both synchronous and asynchronous concurrency and also has the built in feature of signal broadcasting and rendezvous.

The languages based on GALS MoC can be implemented as software programs to run on traditional general purpose processors to achieve the desired behavior. This kind of implementation may provide better data handling but, these traditional processors and classical programming languages do not have similar structures or statements (instructions) to handle the corresponding synchronous and asynchronous features. Hence, implementation on commercial off-the-shelf (COTS) processors is problematic since it must be simulated. Therefore, a general purpose processor based software solution can hardly enhance the application performance or reduce resource usage. Furthermore, the compilation techniques targeting such processor or languages suffers from the drawbacks such as large generated code size [31] and reduced runtime performance.

10 Introduction

Since traditional processors have difficulties to handle synchronous and asynchronous features of GALS MoC, it gives rise to a natural question whether reactive processors can be deployed as alternative. Reactive processors [32–36] and the Esterel Virtual Machine (EVM) [31] are a few examples of execution platforms which provide support for reactivity and concurrency. While all these approaches provide efficient execution of reactive control parts and modest support for concurrency, they provide very poor support or have practically no support for complex data-driven operations. There have been efforts towards supporting heterogeneous applications [37], but they primarily focus on reactive part of applications. Therefore, the architectural support for heterogeneous embedded applications based on GALS MoC is lacking and demands a serious attention.

Furthermore, embedded systems are different from traditional desktop computers in the sense that they are constrained by the size, weight, power, cost and response time. Most embedded systems execute in response to external events, both periodic and aperiodic. The correctness of operation often depends on the response time staying within a given time limit. Also, the suitability of the target platform depends upon the nature of the applications. For example, data-dominated embedded systems such as video games often require high computation performance and large program memories. The mid-end embedded systems may be for example engine control systems typically demand a medium level of computing performance and memory. Low-end embedded systems are typically low cost and high volume consumer devices. They have low computing requirements and a program memory of some kilobytes. The growth in complexity may have a significant impact on implementation constraints such as cost, size, performance as well as power. Cost is, with few exceptions, an important issue in embedded systems. Many embedded systems are produced in large quantities; the need to reduce costs is a major concern. Embedded systems often have significant energy constraints, and many are battery-powered. As a result of these constraints, embedded systems use a slow processor and small memory size to minimize costs and energy consumption thus making it hard to deploy in embedded system with stringent response time requirement. Therefore, embedded-computing applications involve unique challenges, as they must be performed in real time in the face of resource constraints.

In summary, we need a target platform which could efficiently handle GALS MoC and at the same time should be very competitive with other implementations in terms of performance and resource usage. Thus motivation of this thesis is to explore and develop an efficient execution platform for SystemJ based applications. The architecture should be capable of efficient execution of control and data-computations as the embedded applications are heterogeneous in nature and consist of a mix of control and data parts. The solution should minimize logic resources so that it is economical enough cost wise. Furthermore, the capability of being time-predictable is essential in real-time systems. With a lot of functionality being added, the need for high performance in embedded systems has become inevitable. The architecture must be scalable towards

1.4 Research Contributions 11

multiprocessors so that it is able to support increasingly complex applications, since it is not possible to rely on single core frequency improvement.

### 1.4 Research Contributions

The focus of this thesis is the development of an efficient architecture for the execution of GALS programs. The project was driven by the desire to achieve predictable, competitive execution speeds at minimal resource usage, in terms of processor size. This work has resulted in proposing several novel processor architectures that improve the performance and efficiency while consuming less resources and guaranteeing the time predictability offered by the base processor architecture.

In summary, the contributions of this research are:

- Accelerated and Time Predictable Execution of GALS Programs: We demonstrate the effectiveness of a new predictable execution of GALS program on GALS programs described in SystemJ on a Java processor, called Java Optimized Processor (JOP). Previously, the SystemJ programs were translated to Java which are further compiled for execution on the targeted general purpose processor. This approach was slow due to interpreting nature of Java Virtual Machine and require large memories. However, the use of JOP eliminates the overheads of the interpreter as it is done natively by the processor itself. This intermediate step in the design process with SystemJ enables us to prototype and to verify the specifications on a predictable architecture.

- A Reactive Java Processor for the Execution of GALS Programs: We also propose a novel, high performance and low cost execution architecture for SystemJ. The new core, which is called RJOP (Reactive JOP), facilitates efficient execution of both data dominated and control dominated embedded applications described in SystemJ. It extends JOP to efficiently handle reactivity and signal manipulation. It also maintains the time-predictable execution of the applications intended for real-time embedded systems and calculation of Worst Case Reaction Time (WCRT) as provided by the original core.

- A Heterogeneous Tandem Processor Architecture for GALS Programs Execution: We propose a high performance solution in the form of a tandem processor with JOP, or TP-JOP, in which control processor (CP) and JOP work together to implement control flow and data operations, separated during compilation of GALS programs, respectively. TP-JOP is built on TVM/TP approach [38, 39] which are based on the idea of tandem execution of two processors, one that controls the flow of SystemJ program (CP, control processor) and one that executes operations that are within our GALS MoC (which are

12 Introduction

considered instantaneous and expressed in standard Java). The data oriented part of the code which is in Java was executed on a general purpose processor with JVM in previous implementation of the TP. We demonstrate the effectiveness of the architecture through experimental evaluation against a range of suitable benchmark.

- Efficient Merging of Control and Data-computations: Multiple heterogeneous cores have their own design complexity issues. Special purpose cores have significant impact on the memory hierarchy of the system, and require specially designed communication protocols for fast data exchange among them. A major challenge is the design of a suitable high-performance and flexible communication interface between them. We propose a novel GALS-JOP processor where JOP and the CP functionalities are merged into a single processor by enriching JOP with some key constructs and abstractions for efficient implementation of SystemJ GALS Programs. The concurrency and reactivity control flow presented as special instructions is translated to Java statements which are mapped to custom bytecodes. This core has acceptable performance considering that it is more economical in terms of resource usage compared to the previous implementations.

- Execution of Control and Data computations with Distinct Modes of Executions: The focus of the research has been the trade-off between performance and complexity of the microarchitecture. Devoting precious silicon area to special purpose execution hardware or processor does not lead to an optimal solution. We have developed a solution which extracts the desired functionality and execution speed without consuming precious resources. We have presented an approach to efficiently mix Java with asynchronous and synchronous concurrency and execute it on a specialized Java processor extended with capabilities for concurrency and reactivity. A new processor, which uses JOP (Java Optimized Processor) as its base, executes concurrent programs that comply with GALS formal model of computation by clearly distinguishing between concurrency and reactivity control flow and Java control flow. The new processor, called JOP-Plus, can be used for embedded and even real-time applications in which the majority of application code is written in Java and the overall programs specified and structured in SystemJ systemlevel concurrent programming language. We have implemented a processor core where two virtual processors share one data-path. The virtual processors operate independently although not in parallel.

- A Homogeneous Multiprocessor Architecture for Concurrent Execution of GALS Programs: A new, scalable, multiple processor architecture is proposed for execution of SystemJ programs based on GALS model of computation. The proposed architecture GALS-CMP, based on JOP-Plus, is suitable for implementation of embedded systems that contain reactive or control dominated parts that interact with external environment. It allows concurrent execution of clock-domains improving the response time.

- *Compiler Modifications:* We have made several modifications to the SystemJ compiler back-end to produce compatible Java codes for the new target platforms. We also proposed several optimizations to produce more efficient code in future.

- Experimental evaluation: We evaluate the different architectures and validate their effectiveness by running benchmarks on them. Better performance, code density and resources usage has been found and compared to previous approaches for SystemJ execution, thus proving its suitability for heterogeneous embedded applications.

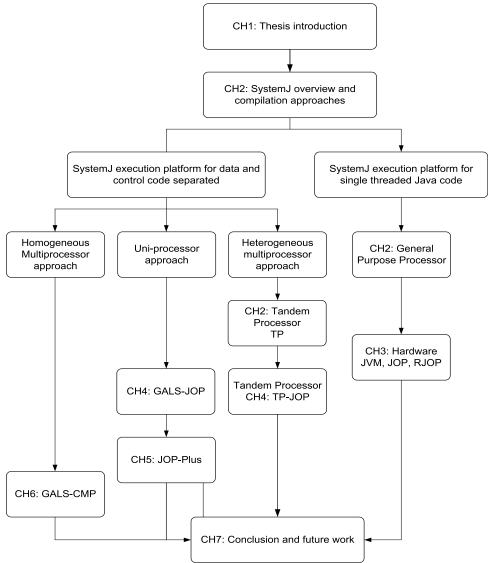

### 1.5 Thesis Organization

The remainder of this thesis is organized as shown in Figure 1.3. Chapter 2 gives an overview of the SystemJ language. The chapter starts with the arguments on the need of such a language and introduces its syntax and structure through an example program. Next, the compilation strategies used for target platforms are discussed in detail. Finally, the execution of code produced by the SystemJ compiler on existing platforms is discussed.

Chapter 3 presents a detailed description of Java Virtual Machine (JVM) specifications and its structure. Then, we discuss different hardware solutions from both academia and industry for accelerating Java in embedded systems. The details of a Java processor, called Java Optimized Processor (JOP), and its architecture are also presented. JOP, which is the basic tool of this research, is introduced as the execution platform for GALS programs and its effectiveness is demonstrated through experimental results. This chapter also describes Reactive-JOP, an enhanced version of JOP which incorporates reactive features. This chapter ends with short description in the form of summary.

Chapters 4 presents two different execution platforms for the efficient execution of SystemJ compiled in a way that separates control from data-computations. The heterogeneous multiprocessor architecture TP-JOP is an improved version of existing TP and uses two specialized processors for native execution of both control and data-computations. The novel uniprocessor approach, called GALS-JOP, executes both control and data-computations by translating the programing model of control into the program model of the data-computations processor. This chapter contains a detailed architecture description of both processors and their implementations. The experimental results are provided to evaluate the performance of the proposed architectures.

14 Introduction

Figure 1.3: Thesis structure

Chapter 5 also uses a single processor for the execution of control and data computations similar to GALS-JOP. The proposed processor, called JOP-Plus, has two distinct execution modes for executing control and data parts. This chapter describes the background for the proposed approach, related work and their shortcomings. Next, it gives a description of the strategy to remove these shortcomings. JOP-Plus design flow, memory organization and implementation details are presented next. Finally, the evaluation of JOP-Plus's performance through experimental set up is discussed.

Chapter 6 presents a homogeneous multiprocessor system in order to meet the processing power requirement and response time constraints imposed by the modern applications. This chapter starts with the discussion on performance limits of uniprocessor approach and dwells on the ways to boost performance or processing power beyond the uniprocessor limits. Then we describe GALS-CMP architecture and its compilation and execution flow with the help of an

example. The experimental results and related discussion are presented towards the end of chapter.

Finally, Chapter 7 gives a short discussion on the implementation platforms developed during the course of this research and their performance comparison is carried out. In the end, concluding remarks and possible future directions for the research are presented.

16 Introduction

# Chapter 2

# **SystemJ Overview**

The main goal of SystemJ is to provide a specification mechanism, a language, that allows a system designer to use well-known programming constructs. SystemJ covers all the important criteria of a system level design language. SystemJ is based on formal semantics, which may allow partial automated formal verification of a SystemJ program. The SystemJ is expressive enough to incorporate both data and control flow information and includes a well known programming language Java that is easy to use. This chapter gives an overview of the SystemJ language. It introduces the SystemJ Model of Computation (MoC), syntax, synchronous and asynchronous kernel statements. It also presents a SystemJ program example, different approaches to compile it and existing execution platforms.

### 2.1 The SystemJ MoC

The system-level programming language SystemJ [25, 26] extends Java with synchronous and asynchronous concurrency and reactivity, making it suitable for designing complex embedded programs. The language allows use of full Java and discourages the use of Java concurrency (threading library). Instead, SystemJ provides its own concurrency model based on the formal Globally Asynchronous Locally Synchronous (GALS) model of computation (MoC).

A SystemJ program consists of multiple asynchronous processes, called *clock-domains* (CD), which are described at the top design level. The clock-domains are composed together with the asynchronous parallel operator (><). Each clock-domain consists of a number of synchronous concurrent processes, called *reactions*, which execute in lock-step, driven by a logical clock, called *tick*. Transitions in Esterel are also based on the same logical and discrete lock event. A synchronous program reacts to its environment in a sequence of ticks, and computations within a tick are assumed to be instantaneous, i.e., as if the processor executing them was infinitely fast. The reactions communicate within a clock-domain, as well as with the external

environment (*input/output*) through *signals*, which are broadcast and present within the current tick and comply with synchronous reactive MoC [15, 40–42]. The reactions are represented as concurrent processes within a clock-domain using the synchronous parallel operator (||). Communication between reactions in different clock-domains, which are asynchronous each to the other, is carried out through the exchange of messages over *channels*, which are semantically the same as channels used in CSP MoC [8, 22]. Besides operations on signals and channels, SystemJ allows free use of Java data objects and statements in its reactions, and those statements are considered instantaneous in terms of logical time (i.e. they do not consume logical time or ticks). Control flow of a SystemJ program incorporates scheduling of all reactions and clock-domains, as well as communication between reactions, and communication with the external environment. The data-driven computations and transformations are performed in Java. The SystemJ is amenable to verification as it is based on mathematical semantics and can be deployed in mission critical systems.

### 2.2 The SystemJ Entities

The SystemJ has three types of high-level design entities called system, clock-domain and reaction.

### **2.2.1** System

The *system* is the top level entity through which a SystemJ program sees its environment and vice verse. In the declarative part of the system entity, the interface with the environment (which are input/output signals) and channels are declared. The clock-domains are declared inside the body of the system. The channels serve as the communication medium between the clock-domains. Multiple clock-domains, which are asynchronous processes, are also declared in the body of this entity. Within a system, each clock-domain executes at its own tick, and any two clock-domain ticks are unrelated.

#### 2.2.2 Clock-domains

A SystemJ program consists of a set of clock-domains executing at unrelated logical clock ticks. Each clock-domain consists of a number of synchronous concurrent processes called reactions. The clock-domain can be given some name or can be unnamed. The clock-domains can communicate with each other and with the environment using their own set of channels and signals, respectively. Two clock-domains synchronizing with each other using CSP style communication are called partner clock-domains. The data structures cannot be shared among the reactions

2.3 SystemJ Objects

and among the clock-domains using mutual exclusion as it will provide another source of communication which is not safe. This prohibition allows communication only through the signals and channels, which is safer and easier to validate.

#### 2.2.3 Reactions