## http://researchspace.auckland.ac.nz

## ResearchSpace@Auckland

## **Copyright Statement**

The digital copy of this thesis is protected by the Copyright Act 1994 (New Zealand).

This thesis may be consulted by you, provided you comply with the provisions of the Act and the following conditions of use:

- Any use you make of these documents or images must be for research or private study purposes only, and you may not make them available to any other person.

- Authors control the copyright of their thesis. You will recognise the author's right to be identified as the author of this thesis, and due acknowledgement will be made to the author where appropriate.

- You will obtain the author's permission before publishing any material from their thesis.

To request permissions please use the Feedback form on our webpage. <u>http://researchspace.auckland.ac.nz/feedback</u>

### General copyright and disclaimer

In addition to the above conditions, authors give their consent for the digital copy of their work to be used subject to the conditions specified on the <u>Library Thesis Consent Form</u> and <u>Deposit Licence</u>.

### **Note : Masters Theses**

The digital copy of a masters thesis is as submitted for examination and contains no corrections. The print copy, usually available in the University Library, may contain corrections made by hand, which have been requested by the supervisor.

# Control of Linear and Nonlinear Systems Using Bit-Streams

CLAUDIO ARMANDO CAMASCA RAMIREZ

A THESIS SUBMITTED IN FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN ELECTRICAL AND ELECTRONIC ENGINEERING THE UNIVERSITY OF AUCKLAND, OCTOBER 2012

SUPERVISORS: DR. AKSHYA SWAIN DR. NITISH PATEL

## ABSTRACT

The implementation of controllers has evolved from its traditional analogue form into a more flexible digital form during past several decades due to the availability of low-cost high-performance digital platforms such as microprocessors and microcontrollers. The conventional approach of digital controller implementation in hardware is based on the assumption that analogue signals are converted into equivalent multi-bit digital format by multi-bit A/D converters. However, the multi-bit processing of signals requires larger processing circuits and routing areas and numerous Input/Output (I/O) pins for connection to external interfaces and therefore increases the complexity of the overall controller implementation. This dissertation investigates the feasibility of an alternate method of controller implementation based on 1-bit signal processing which may overcome the limitations of multi-bit processing. In 1-bit processing, the analogue or multi-bit signals are converted into a simple 1-bit stream by Delta-Sigma modulation at very high sampling frequencies. This can be implemented easily into FPGAs with bit-serial architectures and typically requires  $(1/n^{th})$  of the hardware required for the equivalent n-bit parallel design.

The focus of this research is on the implementation of controllers using bit-streams on a FPGA platform. Initially, the behaviour and performance of various functional elements such as analogue to bit-stream converter, bit-stream to analogue converter, bit-stream adder and scalar are studied using typical test signals and verified using both simulations and physical measurements. These functional elements are central to the successful implementation of controllers in bit-stream environment.

The effectiveness and feasibility of bit-streams in real time control is investigated by considering the design of Generalised Predictive Controller (GPC) for various types of linear and nonlinear systems. GPC belongs to the group of long range predictive controllers and inherits the advantages of adaptive control for its applicability in stochastic systems. The performance of bit-stream controller is verified using two distinctly different simulation engines, Matlab<sup>TM</sup>and Very High Speed Integrated Circuits Hardware Description Language (VHDL), where the former serves as an ideal implementation platform. Firstly, bit-stream based GPC is designed for linear systems considering examples of a D.C. servo-mechanism and linear thermal system with time delay. Discrete parametric models are fitted to both these systems using the standard procedure of system identification and these are used to design the GPC. The optimum values of various parameters of the GPC such as control and prediction horizon, and control-weighting sequence are obtained using a genetic algorithm. The performance of bit-stream based GPC is compared with those obtained from an GPC implemented using Matlab<sup>TM</sup>/Simulink<sup>TM</sup>.

The feasibility of implementing controllers using bit-stream for unstable system is investigated considering the example of an unstable magnetic levitation system. The performance of various controllers such as feedback linearising controller, state space based model predictive controller, generalised predictive controller and lag-lead compensator are studied via simulations using Mentor Graphics' ModelSim<sup>TM</sup> and compared to the results from an ideal MPC implemented using Matlab<sup>TM</sup>/Simulink<sup>TM</sup>. Finally, the GPC and lag-lead controller are implemented in bit-stream on an experimental prototype and their performance are compared to the ideal implementation and is found to be satisfactory.

A new method of designing Generalised Predictive Controller (GPC) for a wide class of nonlinear systems, which are represented by polynomial Nonlinear Auto Regressive Moving Average with eXogenous inputs (NARMAX) model, is proposed. At first, the NARMAX model is identified using a novel method of structure selection or which terms to include into the model, based on Evolutionary Programming. The proposed structure selection algorithm introduces an Internal Term Penalty (ITP) function to reject spurious terms and adopts a pruning strategy to remove insignificant terms from the model by assigning it a time-to-live parameter.

The design of GPC for nonlinear system is based on the output predictions from an extended model which consists of a linear controllable model (called the reference model) and a disturbance model. The disturbance model is represented by a polynomial NARMAX model and is estimated using evolutionary computation. Optimum values of some of the tuning parameters of the GPC such as control and prediction horizons are obtained using evolutionary programming. The nonlinear GPC is implemented in bit-streams and their performance is compared with the ideal implementation considering several simulated examples.

My thesis is dedicated to the unforgettable memories of my grandfather. Mi tesis esta dedicada a los inolvidables recuerdos de mi abuelo.

## Armando Ramirez Aquije

From the inception of the simplest mathematical concept to the writing of these final words, it is inconceivable to imagine the completion of this thesis without the assistance of some truly inspiring individuals. I, therefore, would like to acknowledge the people that helped and inspired me during my long journey towards the completion of my doctorate.

I wish to express my foremost gratitude to Dr. Akshya Swain and Dr. Nitish Patel. Their trust, support and encouragement has forever shaped the way I approached my research. Thanks to them, I have learnt so much over the years and across the many aspects of control system theory and implementation. They have pushed me past further than I ever thought possible and until the very last day. I am truly thankful for everything they have done for me.

I am grateful also to have met my fellow research colleagues, Ravikesh Chandra, Nasser Giacaman, Wei-Tsun Sun, Shaun Dowler, Salim Namik, Hazim Namik, Ramin Vali and Andrew Austin. Their ability to engage in eloquent and entertaining conversations added enjoyment to being a researcher.

During the toughest of times I could always count on my dearest of friends. I would like to acknowledge the friendships of Simon Lee, Rajesh Bhana, Anthony Yung, Jeetesh Deva, Iain Lonie, Saurabh Rajvanshi and Jeremy Tam. Thank you for showing me life outside of engineering.

I am grateful for my sister Cynthia. Her company, support and love has always been nothing short of amazing. I am extremely proud to be her brother.

I would like to express my extreme and deepest gratitude my parents, Ada and Alberto Camasca. From the moment they taught me how to speak and count, I have been nothing but in debt to them. Their love, support and advice throughout the many years of my studies, have kept me focus during the most arduous and treacherous of roads. I can never repay what they have done for me and I will always remember their sacrifice whenever I read these words.

And to my Creator, thank you.

Claudio A. Camasca Ramirez October 2012

# CONTENTS

| 1 | Intro | oduction                                                      | 1  |

|---|-------|---------------------------------------------------------------|----|

|   | 1.1   | Motivation and Rational                                       | 1  |

|   | 1.2   | Objectives of the Thesis                                      | 5  |

|   | 1.3   | Outline of the Thesis                                         | 5  |

| 2 | Bit-  | Streams - An Introduction                                     | 7  |

|   | 2.1   | Analogue and Digital Conversion in Bit-stream                 | 7  |

|   |       | 2.1.1 Signal Encoding                                         | 8  |

|   | 2.2   | The Concept of Bit-streams                                    | 9  |

|   |       | 2.2.1 Quanta                                                  | 10 |

|   |       | 2.2.2 A Zero Magnitude Bit-Stream                             | 10 |

|   |       | 2.2.3 Non-Zero Magnitude Bit-Streams                          | 12 |

|   |       | 2.2.4 Multi-Bit Binary Word                                   | 12 |

|   |       | 2.2.5 Instantaneous Value                                     | 14 |

|   |       | 2.2.6 Magnitude and Range                                     | 14 |

|   | 2.3   | Bit-Stream Functional Elements                                | 16 |

|   |       | 2.3.1 Synchronisation                                         | 16 |

|   |       | 2.3.2 Analogue to Bit-Stream Conversion Theory                | 17 |

|   |       | 2.3.3 Adder                                                   | 18 |

|   |       |                                                               | 30 |

|   |       | 5                                                             | 33 |

|   |       |                                                               | 43 |

|   |       | 2.3.7 Tapped Delay                                            | 44 |

|   | 2.4   | Bit-stream Simulation of Linear and Nonlinear Systems         | 46 |

|   |       | 2.4.1 Guidelines for Bit-Stream Implementation                | 46 |

|   |       | 2.4.2 Examples                                                | 48 |

|   | 2.5   | Conclusions                                                   | 52 |

| 3 | Bits  | tream based Generalised Predictive Control for Linear Systems | 53 |

|   | 3.1   |                                                               | 53 |

|   | 3.2   | Generalised Predictive Control                                | 54 |

|   | 3.3   | Investigation Procedure                                       | 57 |

|   | 3.4   | Case Study 1: Design of GPC for Speed Control of a D.C. Motor | 57 |

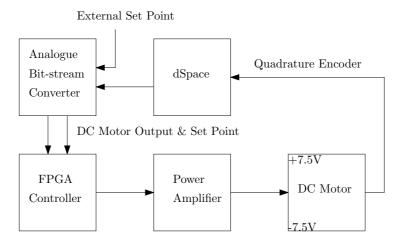

|   |       | 3.4.1 Bit-stream Based GPC for D.C. Motor: Experimental Setup | 60 |

|   |       | 3.4.2 Step 1: Discrete Parametric Modelling of D.C. Motor     | 64 |

|   |       | 3.4.3   | Step 2: Optimisation of Gains for Generalised Predictive Controller for D.C. |      |

|---|-------|---------|------------------------------------------------------------------------------|------|

|   |       |         | Motor                                                                        | 67   |

|   |       | 3.4.4   | Step 3: Experimental Results                                                 | 69   |

|   | 3.5   | Case S  | Study 2: Design of GPC for Temperature Control of a Thermal System           | 72   |

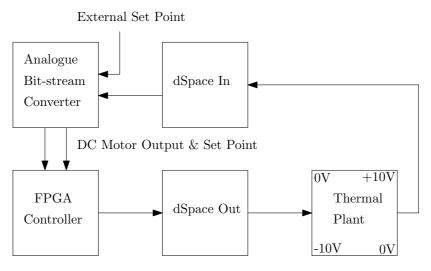

|   |       | 3.5.1   | Bit-Stream Based GPC for Thermal System: Experimental Setup                  | 73   |

|   |       | 3.5.2   | Step 1: Discrete Parametric Modelling of Thermal System                      | 73   |

|   |       | 3.5.3   | Step 2: Optimisation of Gains for Generalised Predictive Controller for a    |      |

|   |       |         | Thermal System                                                               | 79   |

|   |       | 3.5.4   | Step 3: Experimental Results                                                 | 79   |

|   | 3.6   | Conclu  | usions                                                                       | 80   |

| 4 | Bit-s | stream  | based Controller for an Unstable Magnetic Levitation System                  | 83   |

|   | 4.1   | Introdu |                                                                              | 83   |

|   | 4.2   | Mathe   | matical Model of Magnetic Levitation System                                  | 84   |

|   | 4.3   | Desigr  | n of Feedback Linearising Controller                                         | 87   |

|   |       | 4.3.1   | Simulation Results of Feedback Linearising Controller: Multi-bit Implemen-   |      |

|   |       |         | tation                                                                       | 90   |

|   |       | 4.3.2   | Simulation Results of Feedback Linearising Controller: Bit-stream Imple-     |      |

|   |       |         | mentation                                                                    | 92   |

|   | 4.4   | Linear  | ised Model of Magnetic Levitation System                                     | 93   |

|   |       | 4.4.1   | State Space Based Model Predictive Control                                   | 94   |

|   |       | 4.4.2   | Simulation Results of State Space Model Predictive Control                   | 96   |

|   | 4.5   | Gener   | alised Predictive Controller for Magnetic Levitation System                  | 100  |

|   | 4.6   | Conclu  | usions                                                                       | 103  |

| 5 | Stru  | cture S | Selection of Polynomial Nonlinear Systems                                    | 105  |

|   | 5.1   | Introdu | uction                                                                       | 105  |

|   | 5.2   | Repre   | sentation of Nonlinear Systems Using NARMAX model                            | 106  |

|   |       | 5.2.1   | Polynomial Models                                                            | 107  |

|   |       | 5.2.2   | Output-affine Difference Equation Models                                     | 108  |

|   |       | 5.2.3   | Rational Difference Equation Models                                          | 108  |

|   | 5.3   | Syster  | n Identification Using Polynomial NARMAX Models                              | 109  |

|   |       | 5.3.1   | Tests for Nonlinearity                                                       | 110  |

|   |       | 5.3.2   | Structure Detection and Parameter Estimation                                 | 111  |

|   | 5.4   | Model   | Validity Test                                                                | 111  |

|   |       | 5.4.1   | Cross Validation                                                             | 111  |

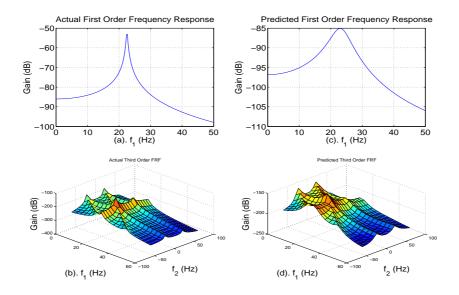

|   |       | 5.4.2   | Correlation Tests                                                            | 112  |

|   |       | 5.4.3   | Generalised Frequency Response Function                                      | 113  |

|   | 5.5   | Struct  | ure Selection of Polynomial NARMAX Model using Evolutionary Programming      | g114 |

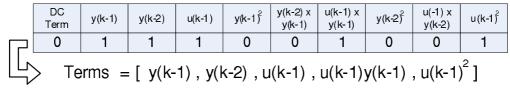

|   |       | 5.5.1   | Initialisation: Representation of Model Terms                                | 114  |

|   |     | 5.5.2    | Variation                                           | 115 |

|---|-----|----------|-----------------------------------------------------|-----|

|   |     | 5.5.3    | Evaluation                                          | 115 |

|   |     | 5.5.4    | Selection                                           | 116 |

|   | 5.6 | Simulat  | ion Results                                         | 116 |

|   |     | 5.6.1    | Example 1: Van der Pol Oscillator                   | 116 |

|   |     | 5.6.2    | Example 2: Modelling of Small Scale Wave force Data | 118 |

|   |     | 5.6.3    | Example 3: Duffing's Oscillator                     | 122 |

|   | 5.7 | Conclus  | sions                                               | 124 |

| 6 | Gen | eralised | Predictive Control for Nonlinear Systems            | 127 |

|   | 6.1 | Introduc | ction                                               | 127 |

|   | 6.2 | The GP   | PC Algorithm - Classical Approach                   | 128 |

|   | 6.3 | Nonline  | ar Predictive Controller Using NARMAX Model         | 129 |

|   |     | 6.3.1    | Controller Formulation                              | 129 |

|   |     | 6.3.2    | Tracking of Asymptotically Constant References      | 132 |

|   |     | 6.3.3    | Intelligent Tuning by Evolutionary Programming      | 132 |

|   | 6.4 | Simulat  | ion Results                                         | 132 |

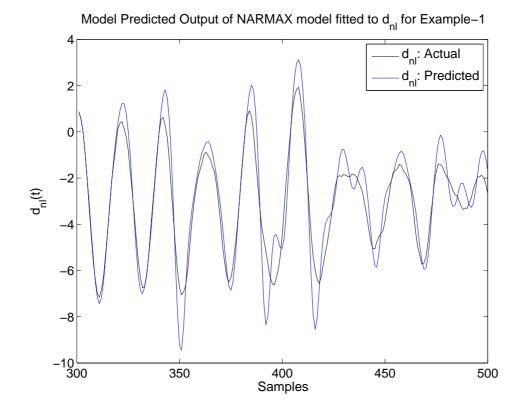

|   |     | 6.4.1    | Example 1: Nonlinear GPC for Duffing's Oscillator   | 133 |

|   |     | 6.4.2    | Example 2: Nonlinear GPC for Nonlinear Resonator    | 136 |

|   | 6.5 | Conclus  | sions                                               | 140 |

| 7 | Con | clusion  |                                                     | 143 |

|   | 7.1 | Future   | Work                                                | 146 |

# FIGURES

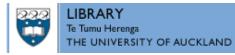

| 2.1  | A continuous signal (A) and a discrete signal (B)                                                             | 8  |

|------|---------------------------------------------------------------------------------------------------------------|----|

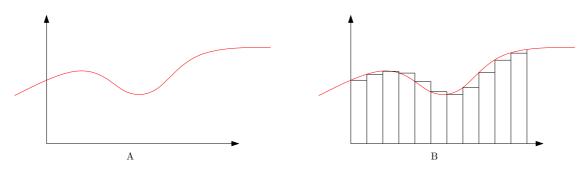

| 2.2  | Canonical control system using multi-bit encoding: $A_d$ is an n-bit digital signal                           |    |

|      | converted to analogue, and $A_i$ is the analogue plant output to be digitised                                 | 9  |

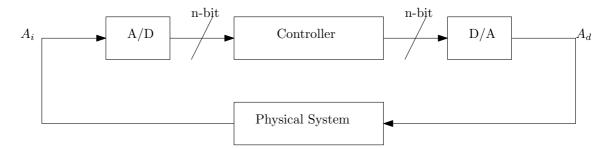

| 2.3  | Bit-stream encoding for control system: $A_i$ is the analogue plant output to be                              |    |

|      | digitised and PDM is the control action.                                                                      | 10 |

| 2.4  | A typical bit-stream signal.                                                                                  | 11 |

| 2.5  | A zero magnitude bit-stream signal                                                                            | 11 |

| 2.6  | Positive magnitude bit-stream signals $\mathcal{S}_1$ and and $\mathcal{S}_2$ synchronised with signal $z.$ . | 12 |

| 2.7  | Negative magnitude bit-stream signals $S_1$ and and $S_2$ synchronised with signal $z$                        | 13 |

| 2.8  | An 8-bit frame encompassing a bit-stream signal                                                               | 13 |

| 2.9  | Instantaneous value of a bit-stream signal: Blue frame shows frame at $k$ , red                               |    |

|      | frame shows frame at $k + 1$                                                                                  | 14 |

| 2.10 | Synchronised decoding for a bit-stream magnitude. Zero signal $z$ is used to de-                              |    |

|      | code bit-stream $S$ to obtain incident quanta $h$ or ejected quanta $l$                                       | 15 |

| 2.11 | The Altera DE2 development and education board                                                                | 17 |

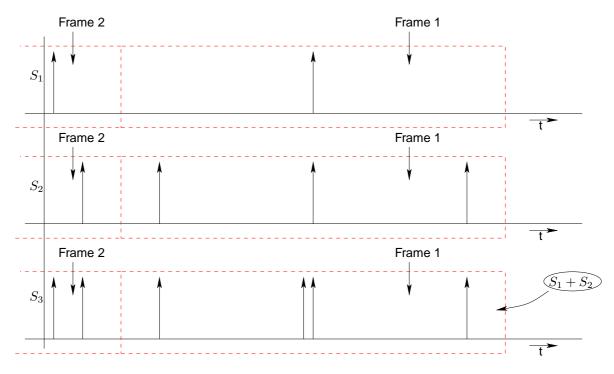

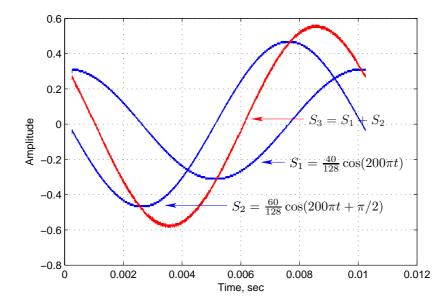

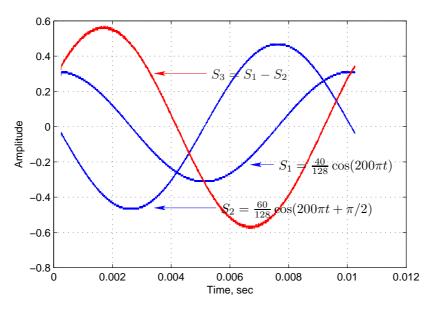

| 2.12 | Conceptual bit-stream summation. $S_1 + S_2 = S_3$                                                            | 19 |

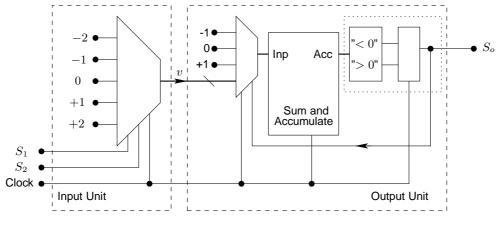

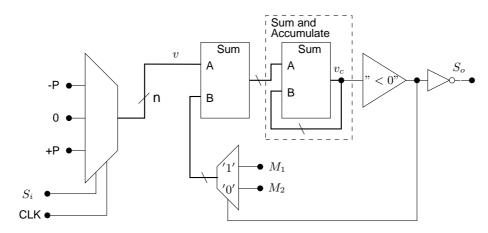

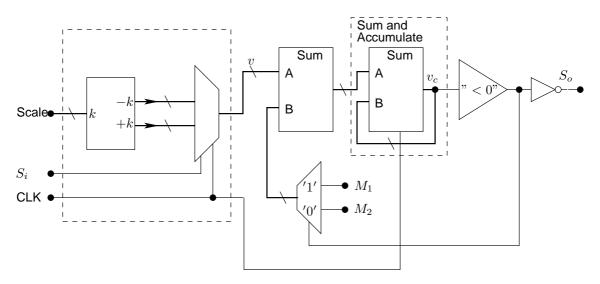

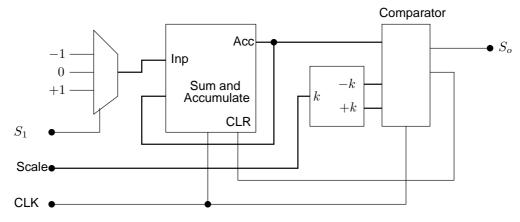

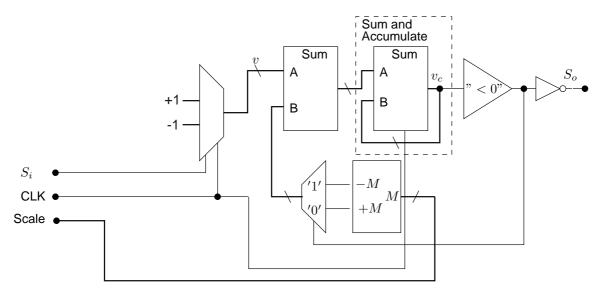

| 2.13 | Type 1 bit-stream adder                                                                                       | 22 |

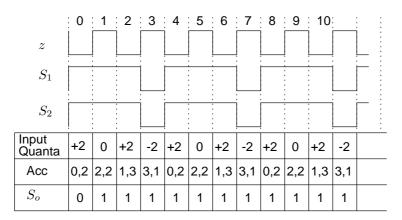

| 2.14 | Simulated bit-stream summation of two sinusoids.                                                              | 23 |

| 2.15 | Limiting value accumulated in a Sum-and-Accumulate component.                                                 | 23 |

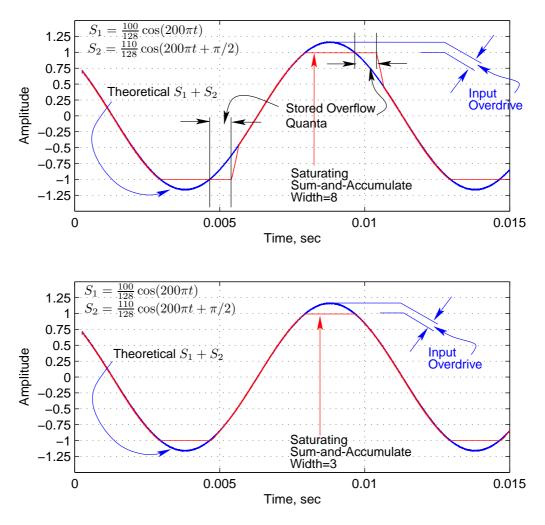

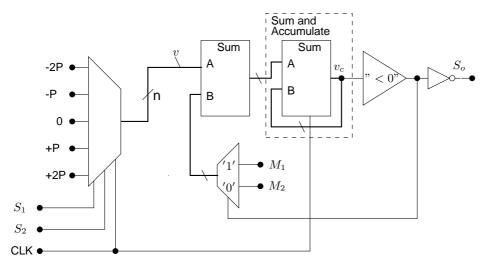

| 2.16 | Saturation effects of two different bit-stream adders                                                         | 24 |

| 2.17 | Bit-Stream to bit-stream modulator generator                                                                  | 25 |

| 2.18 | Output of Sum-and-Accumulate without feedback.                                                                | 26 |

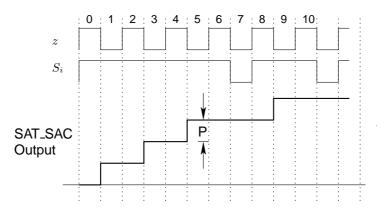

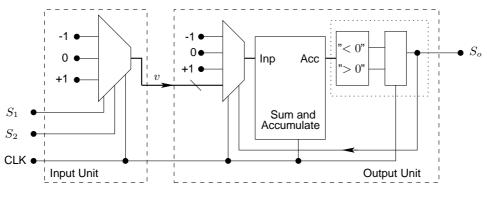

| 2.19 | Type 2 bit-stream adder.                                                                                      | 27 |

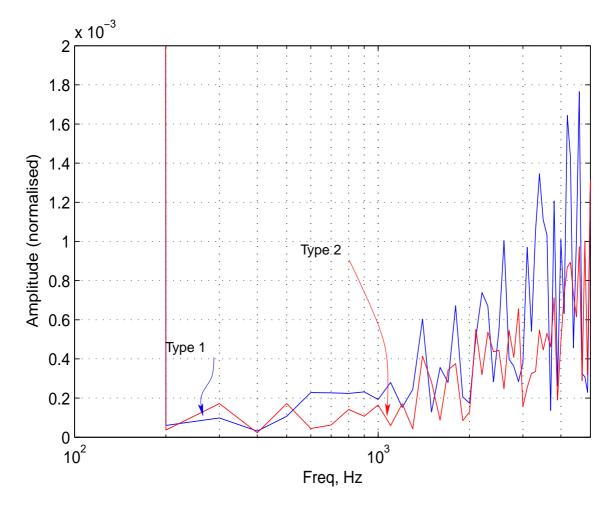

| 2.20 | Normalised spectra of type 1 and Type 2 bit-stream adder outputs                                              | 29 |

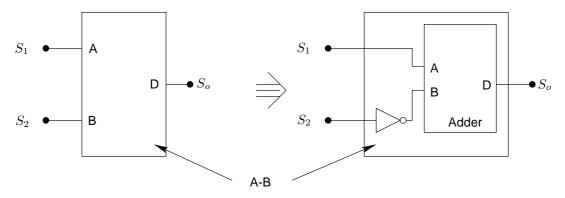

| 2.21 | Bit-Stream subtraction.                                                                                       | 30 |

| 2.22 | Type 1 bit-stream subtractor.                                                                                 | 31 |

| 2.23 | Bit-stream subtraction of two sinusoids                                                                       | 32 |

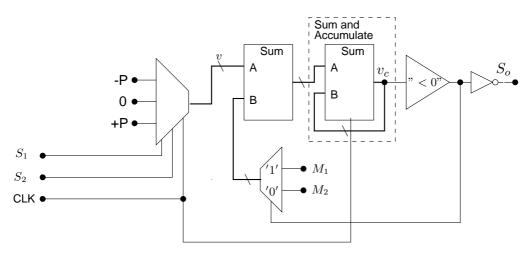

| 2.24 | Type 2 bit-stream subtraction.                                                                                | 33 |

| 2.25 | Normalised spectra of Type 1 and Type 2 bit-stream subtractors outputs                                        | 34 |

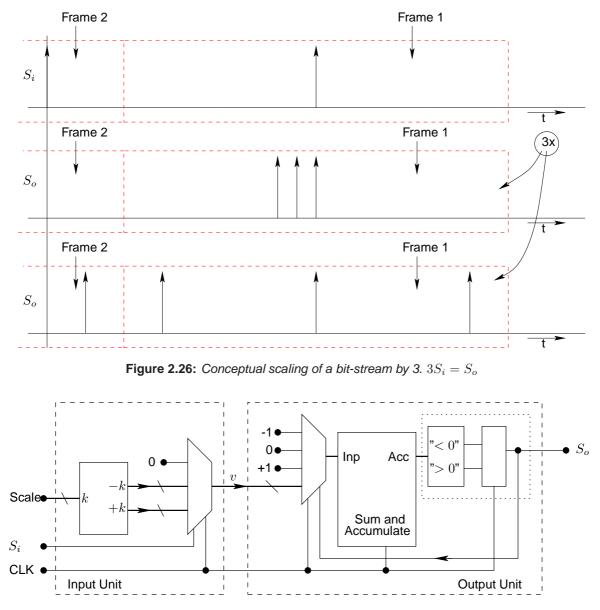

| 2.26 | Conceptual scaling of a bit-stream by 3. $3S_i = S_o$                                                         | 36 |

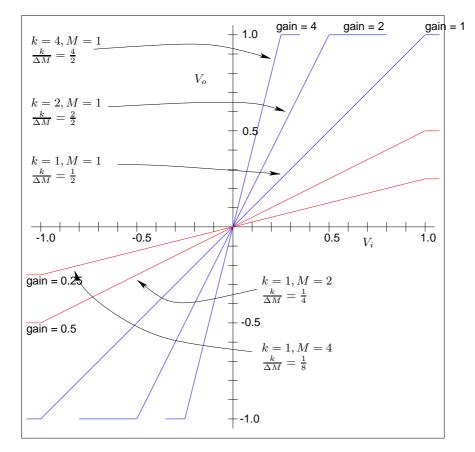

| 2.27 | Type 1 Scale Up for bit-streams.                                                                              | 36 |

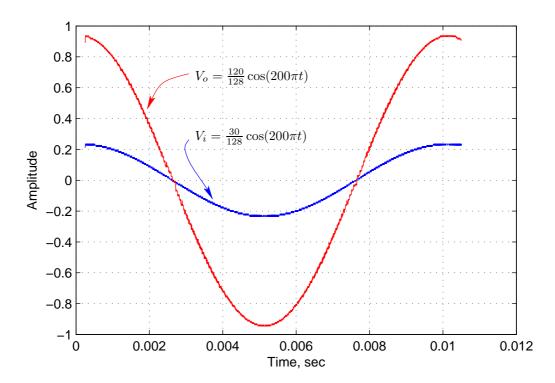

| 2.28 | Simulation of Type 1 Scale Up element.                                                                        | 37 |

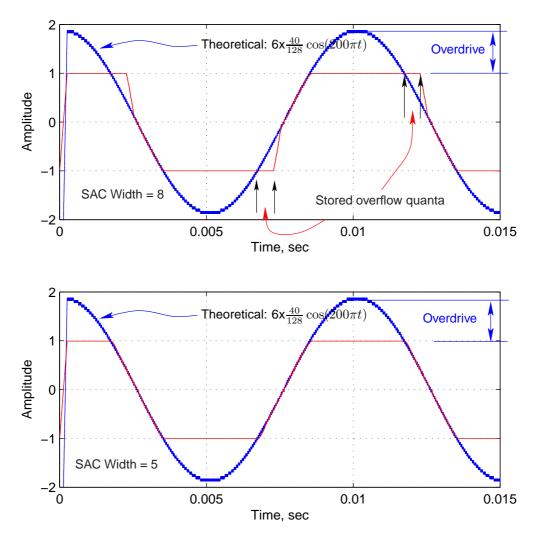

| 2.29 | Impact of SAC width on overdriven Type 1 Scale Up element                                                                                                                                   | 38 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.30 | Type 2 Scale Up for bit-streams.                                                                                                                                                            | 39 |

| 2.31 | Type 1 Scale Down element for bit-streams                                                                                                                                                   | 41 |

| 2.32 | Type 2 Scale Down element for bit-streams                                                                                                                                                   | 41 |

| 2.33 | Transfer function of Type 2 Scaling element.                                                                                                                                                | 42 |

| 2.34 | Extended scaling element.                                                                                                                                                                   | 42 |

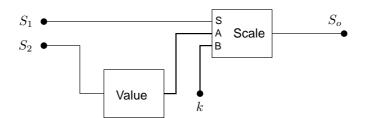

| 2.35 | A bit-stream multiplier.                                                                                                                                                                    | 43 |

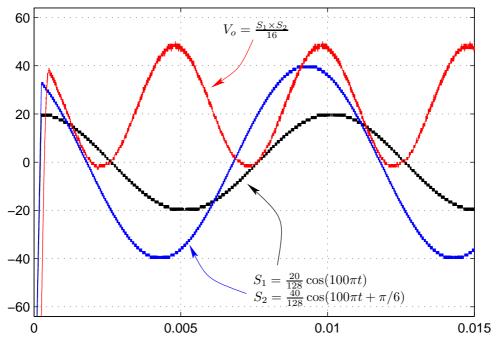

| 2.36 | Response of bit-stream multiplier                                                                                                                                                           | 44 |

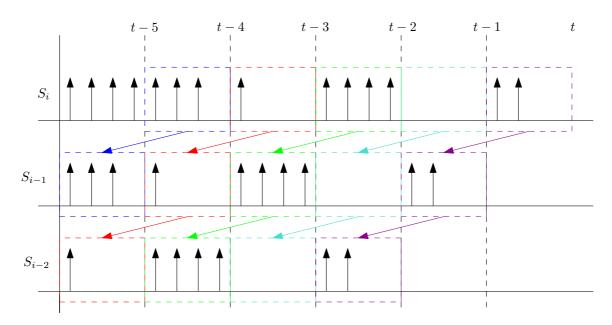

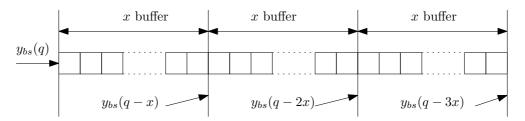

| 2.37 | Conceptual description of a Tapped Delay block for 1 and 2 sample delays                                                                                                                    | 45 |

| 2.38 | Description of the buffer for a Tapped Delay block.                                                                                                                                         | 45 |

| 2.39 | Bit-stream Tapped Delay for $t_s = 0.001 sec$                                                                                                                                               | 46 |

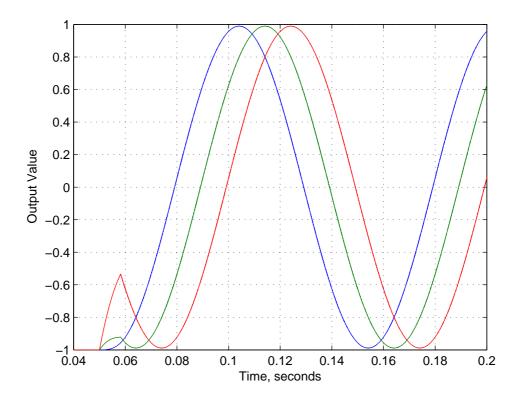

| 2.40 | Bit-stream Tapped Delay for $t_s = 0.01 sec$ and sinusoidal input.                                                                                                                          | 47 |

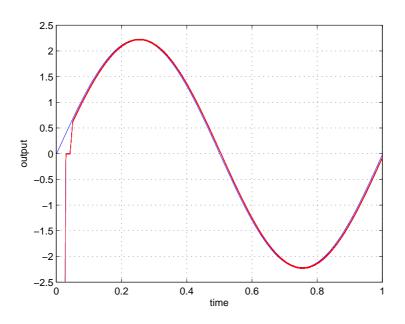

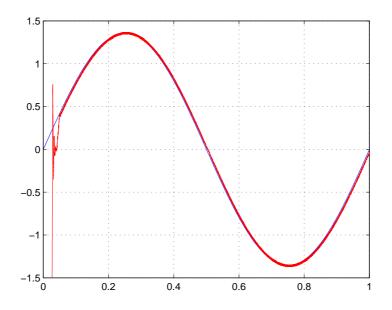

| 2.41 | Output response of a linear system implemented using multi-bit and bit-stream for a 1Hz sinusoidal input: Blue trace corresponds to multi-bit and the red trace                             |    |

|      | corresponds to bit-streams.                                                                                                                                                                 | 48 |

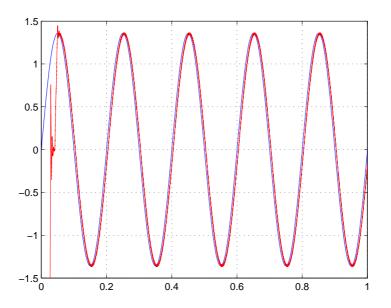

| 2.42 | Output response of a linear system implemented using multi-bit and bit-stream for a 5Hz sinusoidal input: Blue trace corresponds to multi-bit and the red trace corresponds to bit-streams. | 49 |

| 2.43 | Output response of a second order linear system implemented using multi-bit and bit-stream for a 1Hz sinusoidal input: Blue trace corresponds to multi-bit and the                          |    |

|      | red trace corresponds to bit-streams.                                                                                                                                                       | 50 |

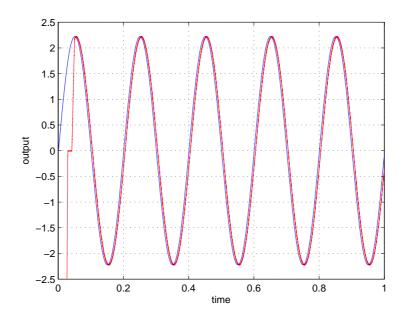

| 2 44 | Output response of a second order linear system implemented using multi-bit and                                                                                                             | 00 |

|      | bit-stream for a 5Hz sinusoidal input: Blue trace corresponds to multi-bit and the                                                                                                          |    |

|      | red trace corresponds to bit-streams.                                                                                                                                                       | 50 |

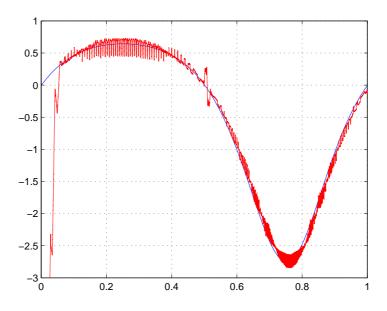

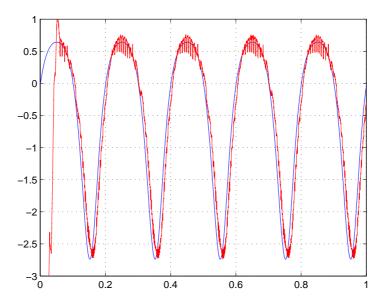

| 2.45 | Output response of a polynomial NARX system implemented using multi-bit and bit-stream for a 1Hz sinusoidal input: Blue trace corresponds to multi-bit and the                              |    |

|      | red trace corresponds to bit-streams.                                                                                                                                                       | 51 |

| 2.46 | Output response of a polynomial NARX system implemented using multi-bit and                                                                                                                 |    |

|      | bit-stream for a 5Hz sinusoidal input: Blue trace corresponds to multi-bit and the red trace corresponds to bit-streams.                                                                    | 51 |

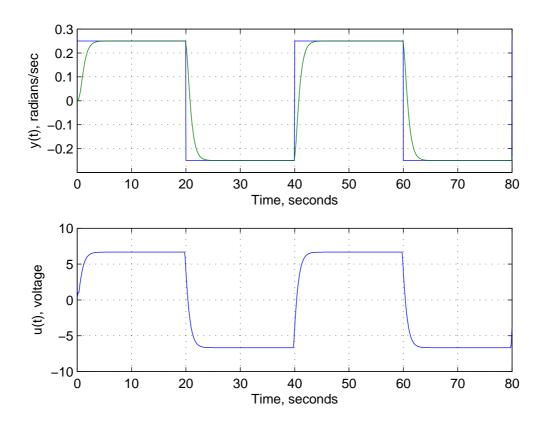

| 3.1  | Speed control of a D.C. servo mechanism using multi-bit GPC: Upper plot shows                                                                                                               |    |

|      | the output speed and the lower plot shows the control signal                                                                                                                                | 59 |

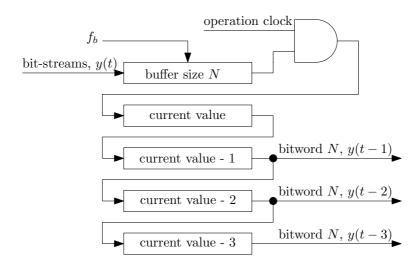

| 3.2  | Implementation of tapped delay block                                                                                                                                                        | 60 |

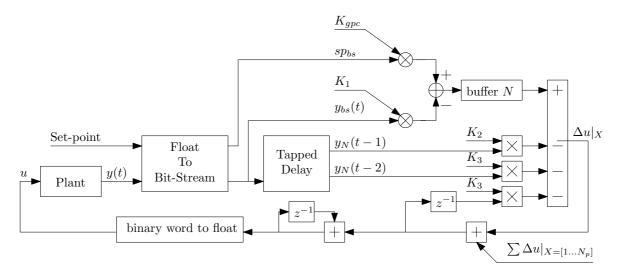

| 3.3  | Layout of bit-stream based GPC implementation using ModelSim <sup>TM</sup>                                                                                                                  | 61 |

| 3.4  | Speed control of a D.C. motor using bit-stream based GPC: Upper plot shows the                                                                                                              |    |

|      | output speed and the lower plot shows the control signal                                                                                                                                    | 61 |

| 3.5  | Schematic diagram for D.C. servo mechanism experiment                                                                                                                                       | 62 |

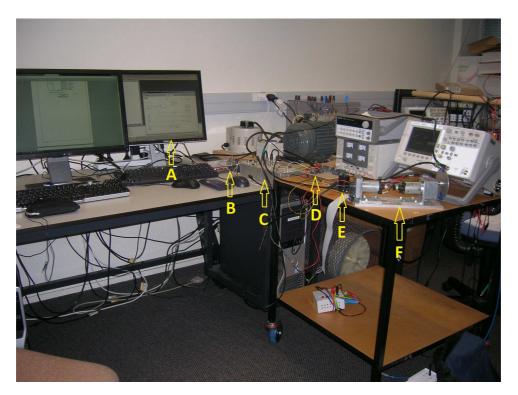

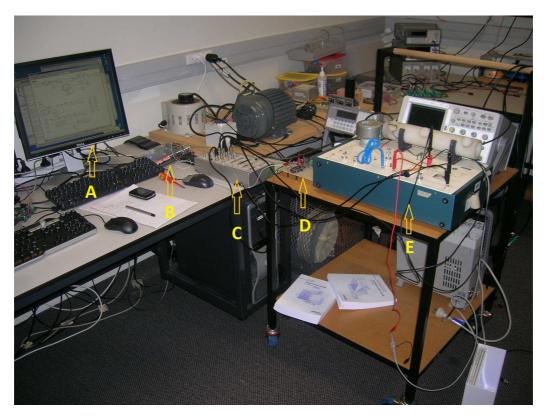

| 3.6  | Prototype of D.C. servo mechanism: (A) Computer interface with Simulink <sup>TM</sup> , (B) DE2 FPGA, (C) dSpace I/O Ports, (D) bit-stream converter, (E) power amplifier |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | and (F) D.C. motor plant.                                                                                                                                                 | 62  |

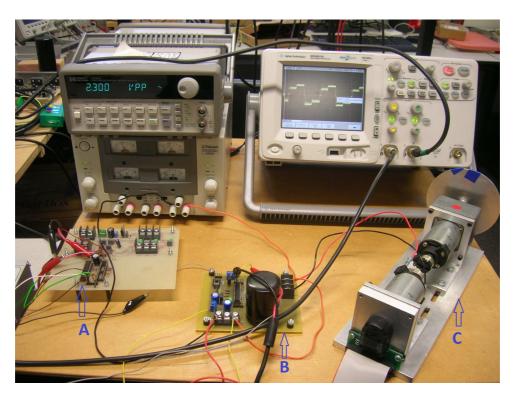

| 3.7  | Detailed view of D.C. motor prototype: (A) bit-stream converter, (B) power amplifier                                                                                      |     |

|      | and (C) a D.C. motor.                                                                                                                                                     | 64  |

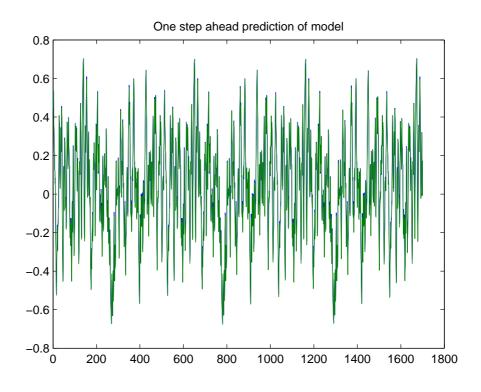

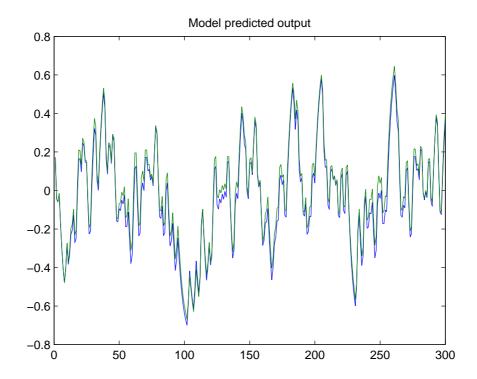

| 3.8  | One step ahead prediction for the identification of a D.C. servo mechanism                                                                                                | 65  |

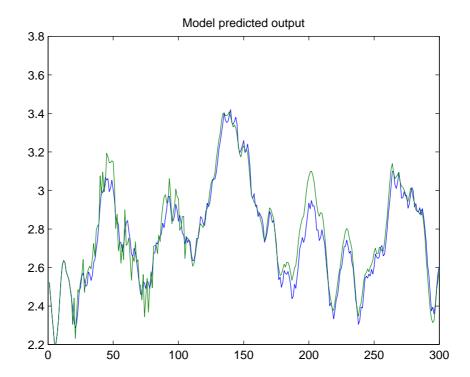

| 3.9  | Model predicted output for the identification of a D.C. servo mechanism                                                                                                   | 65  |

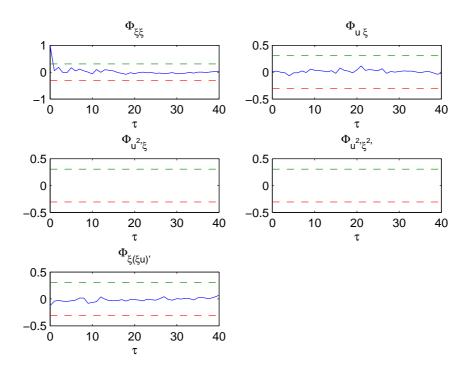

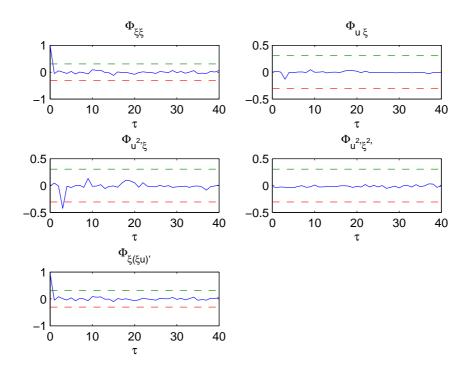

| 3.10 | Correlation plots for the identification a D.C. servo mechanism                                                                                                           | 66  |

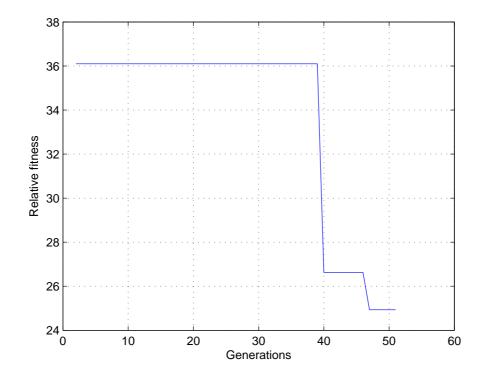

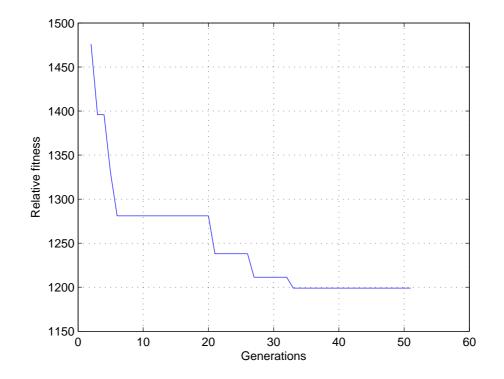

| 3.11 | Fitness trajectory for the optimisation of D.C. servo mechanism GPC parameters.                                                                                           | 69  |

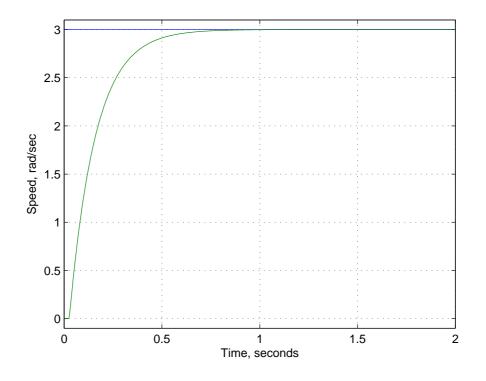

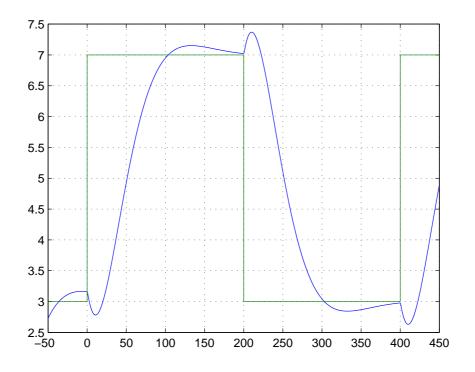

| 3.12 | Speed tracking performance of a D.C. servo mechanism using GPC with optimised parameters obtained via genetic algorithms.                                                 | 70  |

| 3.13 | Simulation results of speed control of D.C. motor using multi-bit GPC.                                                                                                    | 70  |

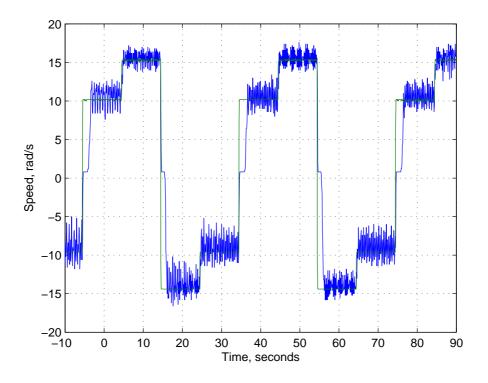

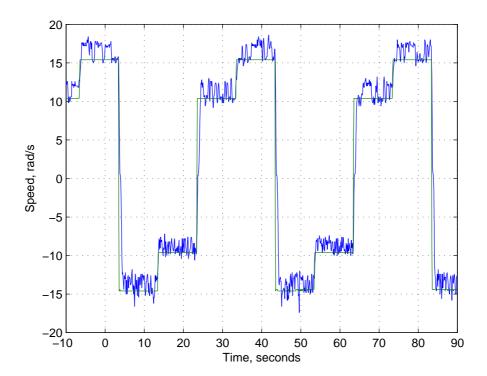

|      | Experimental results for speed control of D.C. motor using multi-bit GPC                                                                                                  | 71  |

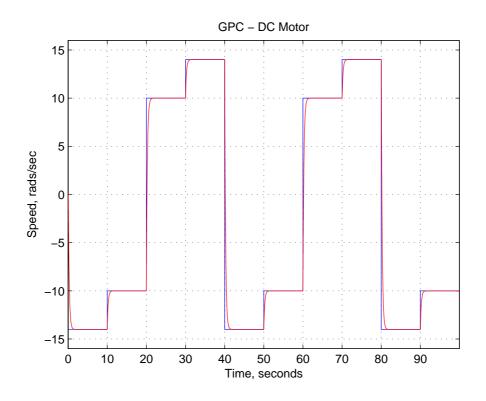

|      | Experimental results for speed control of D.C. motor using bit-stream GPC                                                                                                 | 71  |

|      | Simulation results for temperature tracking of a thermal system using multi-bit                                                                                           |     |

|      | GPC: Upper plot shows the plant output and the lower plot shows the control                                                                                               |     |

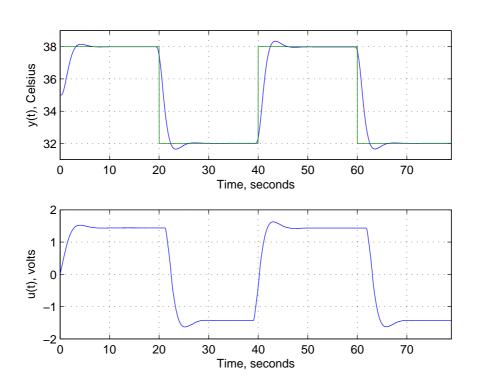

|      | law                                                                                                                                                                       | 73  |

| 3.17 | Simulation results for temperature tracking of a thermal system using bit-stream GPC: Upper plot shows the plant output and the lower plot shows the control law.         | 74  |

| 3.18 | Schematic diagram for thermal plant experiment.                                                                                                                           | 74  |

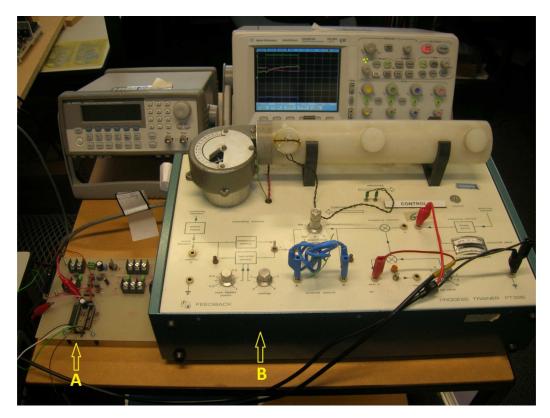

|      | Experimental Prototype of thermal system. (A) Computer interface with Simulink <sup>TM</sup> ,                                                                            |     |

| 0.10 | (B) DE2 FPGA, (C) dSpace I/O Ports, (D) bit-stream converter and (E) thermal plant.                                                                                       | 75  |

| 3.20 | Detailed view of thermal system: (A) bit-stream converter and (B) thermal plant.                                                                                          | 75  |

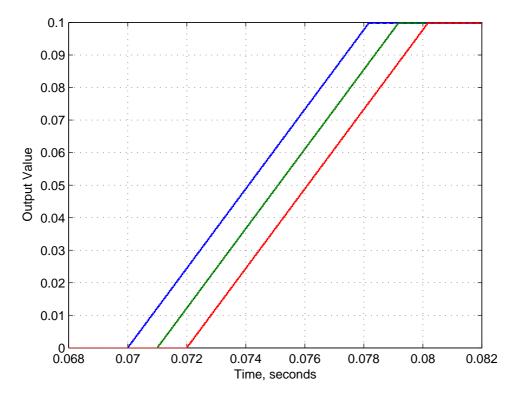

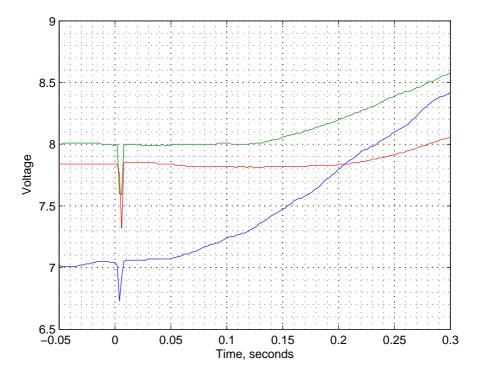

| 3.21 | Transport lag for thermal system: Minimum delay in blue, medium delay in green,                                                                                           |     |

|      | maximum delay in red                                                                                                                                                      | 76  |

| 3.22 | One step ahead prediction of a thermal plant set to medium delay.                                                                                                         | 77  |

| 3.23 | Model predictive output of a thermal plant set to medium delay                                                                                                            | 77  |

| 3.24 | Correlation plots of a thermal plant set to medium delay                                                                                                                  | 78  |

| 3.25 | Fitness optimisation via genetic algorithm for a thermal plant with medium delay .                                                                                        | 79  |

| 3.26 | Simulation of temperature tracking performance of a thermal system set to medium                                                                                          |     |

|      | transport lag using multi-bit GPC.                                                                                                                                        | 81  |

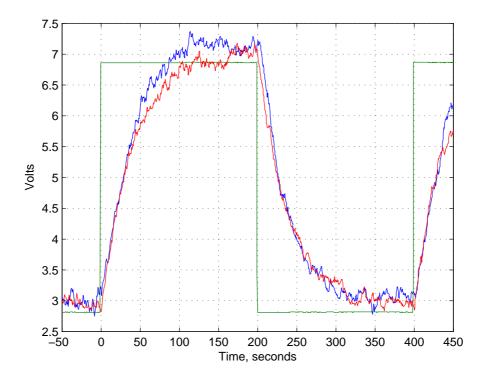

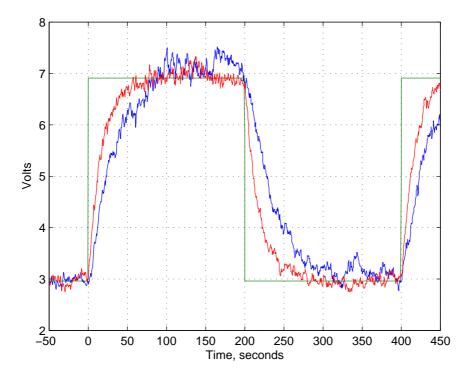

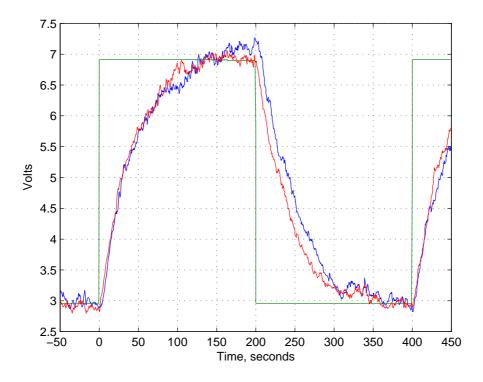

| 3.27 | Temperature tracking performance of a thermal system set to medium delay: Bit-                                                                                            |     |

|      | stream is shown in blue, multi-bit is shown in red and setpoint is shown in green.                                                                                        | 81  |

| 3.28 | Temperature tracking performance of a thermal system set to minimum delay: Bit-                                                                                           |     |

|      | stream is shown in blue, multi-bit is shown in red and setpoint is shown in green.                                                                                        | 82  |

| 3.29 | Temperature tracking performance of a thermal system with maximum delay: Bit-                                                                                             | 0.5 |

|      | stream is shown in blue, multi-bit is shown in red and setpoint is shown in green.                                                                                        | 82  |

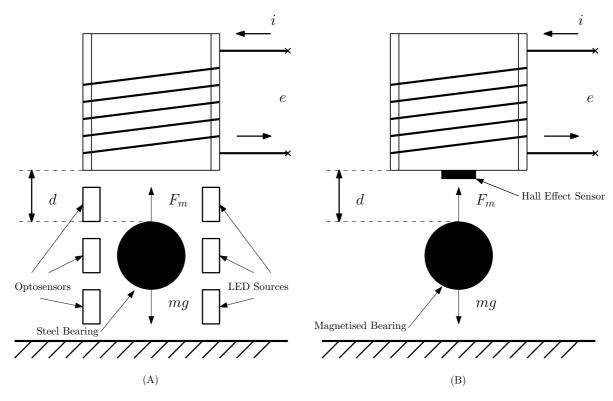

| 4.1  | Magnetic levitation system using (A) optical sensors and (B) a hall effect sensor                                                                                                                                                         | 85  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

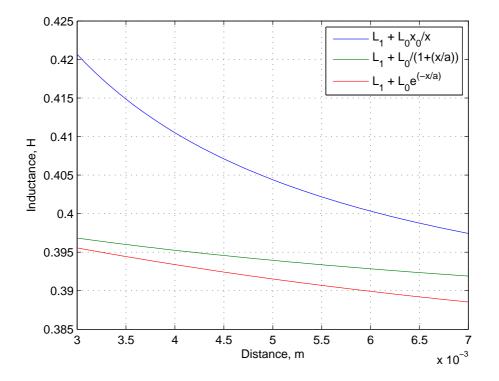

| 4.2  | Comparison between different estimations of nonlinear inductance $L(x)$                                                                                                                                                                   | 86  |

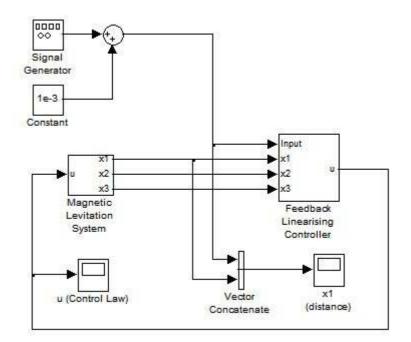

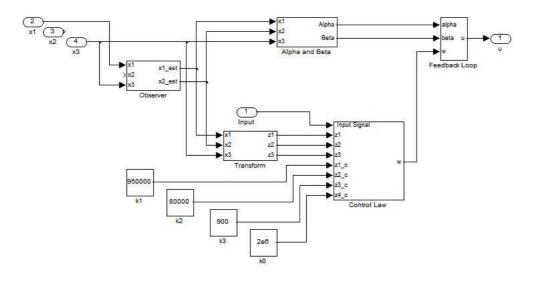

| 4.3  | Schematic diagram for magnetic levitation system with feedback linearising controller implemented in Simulink <sup>TM</sup>                                                                                                               | 90  |

| 4.4  | Schematic diagram for feedback linearising controller.                                                                                                                                                                                    | 91  |

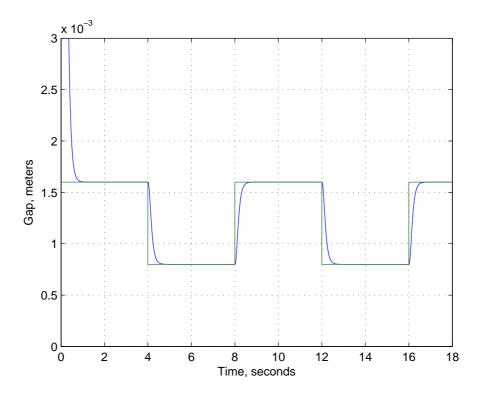

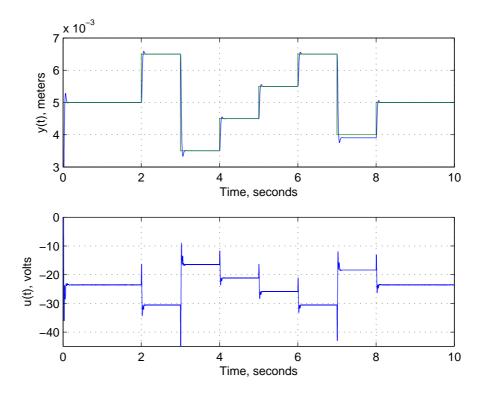

| 4.5  | Tracking performance simulation of a feedback Linearisation controller using multi-<br>bit control                                                                                                                                        | 91  |

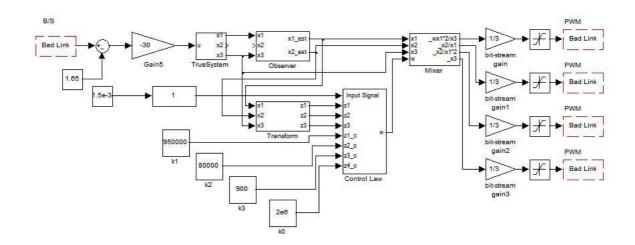

| 4.6  | Magnetic levitation system with feedback linearisation controller implemented for bit-streams.                                                                                                                                            | 92  |

| 4.7  | Tracking performance simulation of a feedback linearisation controller using bit-<br>streams control                                                                                                                                      | 93  |

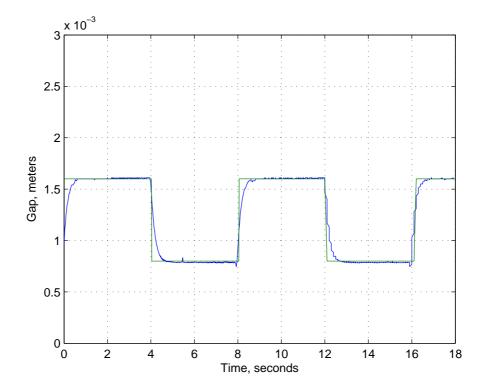

| 4.8  | Tracking performance of MPC implemented using multi-bit: Upper plot shows the displacement and the lower plot shows the control signal                                                                                                    | 98  |

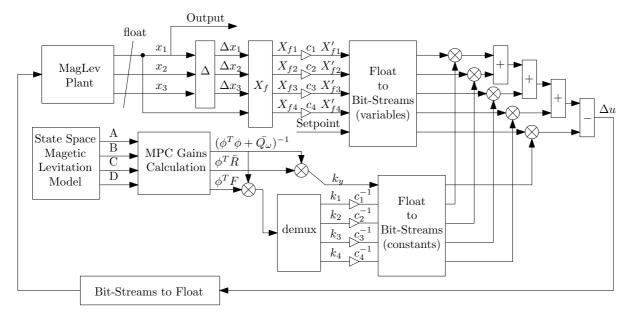

| 4.9  | Layout of bit-stream based MPC implementation using bit-streams                                                                                                                                                                           | 98  |

| 4.10 | Tracking performance of MPC implemented using bit-stream: Upper plot shows displacement and lower plot shows the control signal                                                                                                           | 99  |

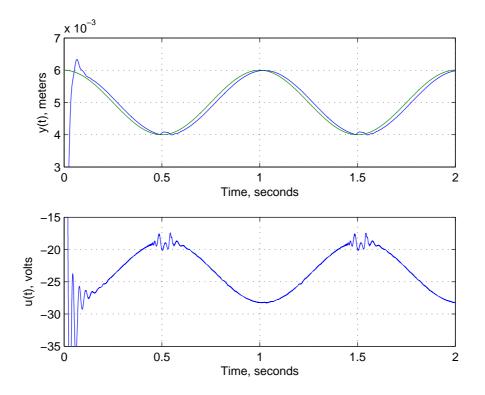

| 4.11 | Sinusoidal tracking performance of MPC implemented using bit-stream: Upper                                                                                                                                                                |     |

|      | plot shows displacement and lower plot shows the control signal                                                                                                                                                                           | 100 |

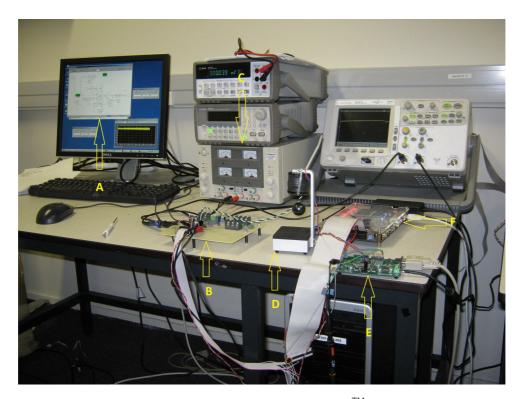

| 4.12 | Photograph of magnetic levitation setup: (A) Simulink <sup>TM</sup> interface, (B) analogue/bit-<br>Stream converter, (C) Power supply, (D) magnetic levitation system, (E) Hilink data<br>acquisition board and (F) DE2 Cyclone II FPGA. | 101 |

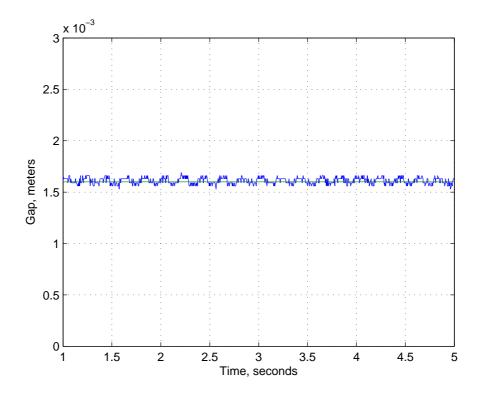

| 4.13 | Tracking performance of a generalised predictive controller using multi-bit control                                                                                                                                                       | 102 |

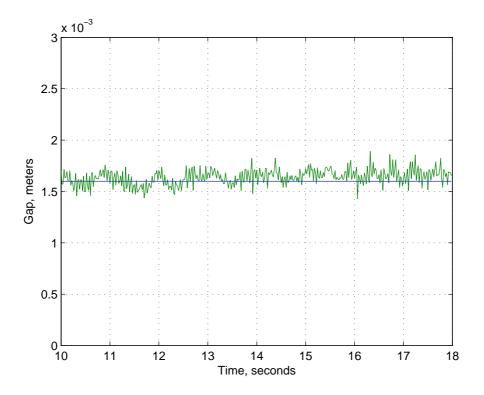

| 4.14 | Tracking performance of a generalised predictive controller using multi-bit and bit-<br>stream control                                                                                                                                    | 102 |

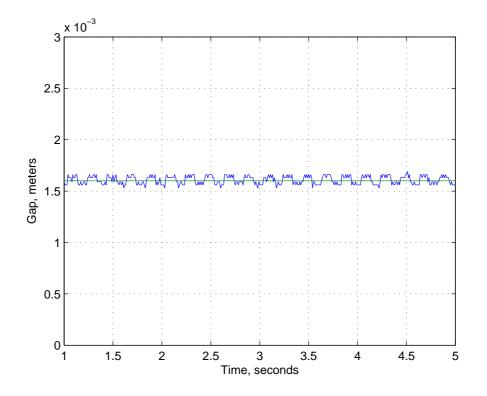

| 4.15 | Tracking performance of a lead compensator using bit-stream control                                                                                                                                                                       | 103 |

| 5.1  | Chromosome encoding for NARMAX model.                                                                                                                                                                                                     | 115 |

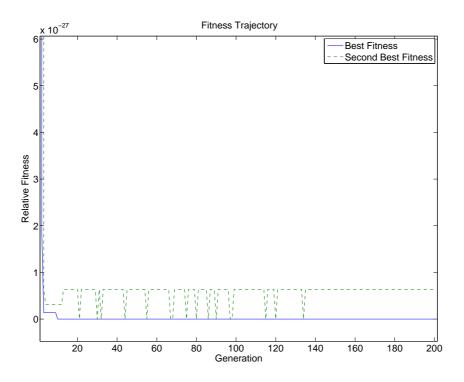

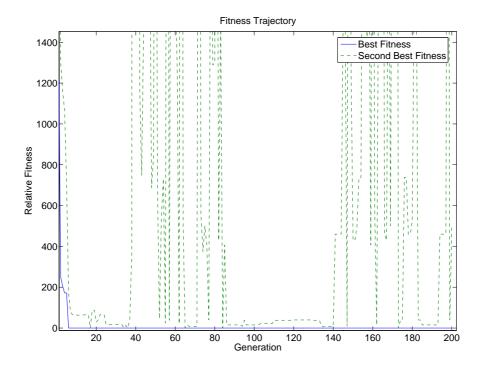

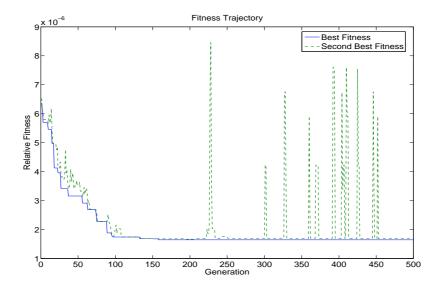

| 5.2  | Convergence curves for Van Der Pol Oscillator                                                                                                                                                                                             | 117 |

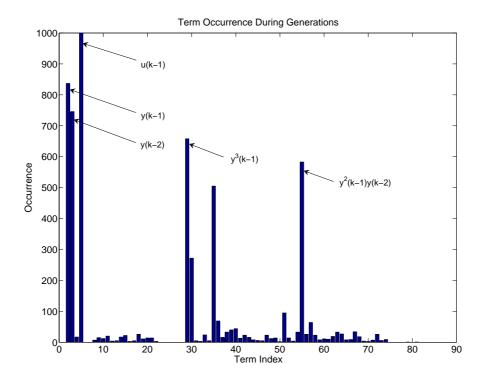

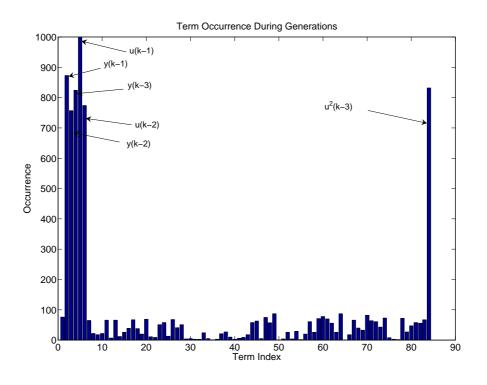

| 5.3  | Term occurrence for Van Der Pol Oscillator                                                                                                                                                                                                | 118 |

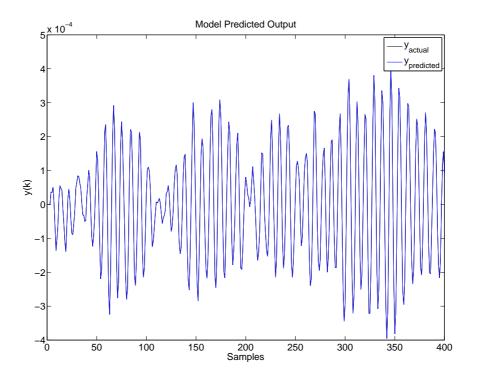

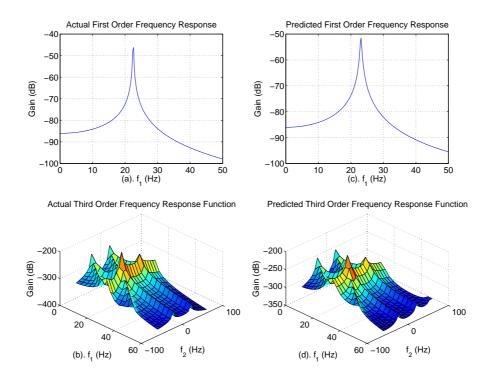

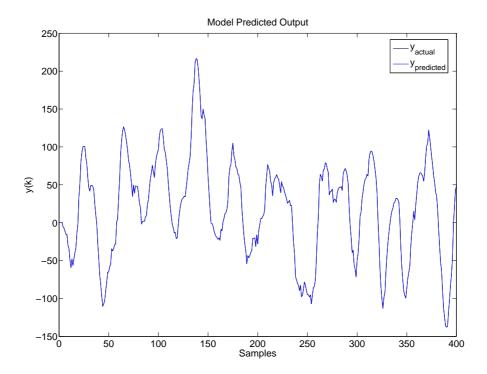

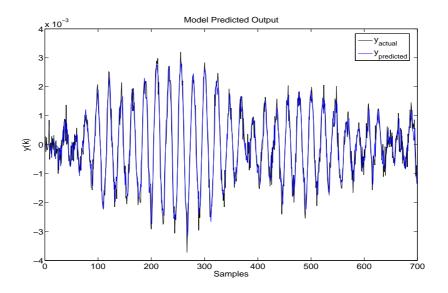

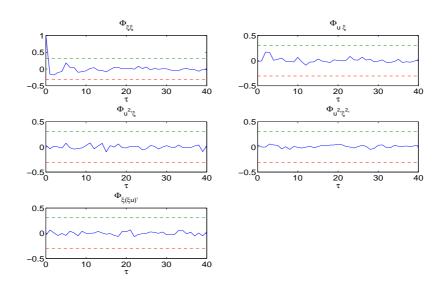

| 5.4  | Model Predicted Output for Van Der Pol Oscillator                                                                                                                                                                                         | 119 |

| 5.5  | Linear and third order frequency response functions (FRF) for a Van Der Pol Os-<br>cillator                                                                                                                                               | 119 |

| 5.6  | Convergence curves for a small scale wave force data                                                                                                                                                                                      | 120 |

| 5.7  | Term occurrence for a small scale wave force data                                                                                                                                                                                         | 121 |

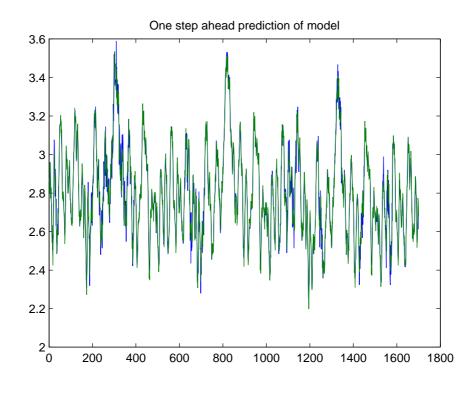

| 5.8  | Model predicted output for a small scale wave force data                                                                                                                                                                                  | 121 |

| 5.9  | Convergence Curves for Duffing's Equation                                                                                                                                                                                                 | 123 |

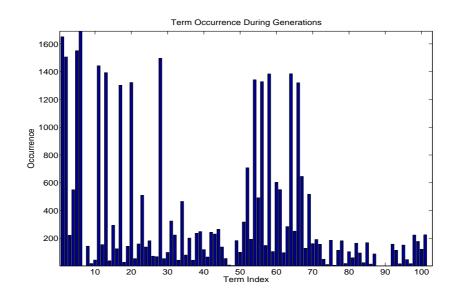

| 5.10 | Term Occurrence for Duffing's Equation                                                                                                                                                                                                    | 123 |

| 5.11 | Model Predicted Output for Duffing's Equation                                                                                                                                                                                             | 125 |

| 5.12 | Model Validation for Duffing's Equation                                            | 125 |

|------|------------------------------------------------------------------------------------|-----|

| 5.13 | Linear and Third Order Frequency Response Functions for Duffing's Equation         | 126 |

| 6.1  | Model predicted output of the NARMAX model fitted to the unmodelled dynamics       |     |

|      | $d_{nl}$ of Example-1                                                              | 134 |

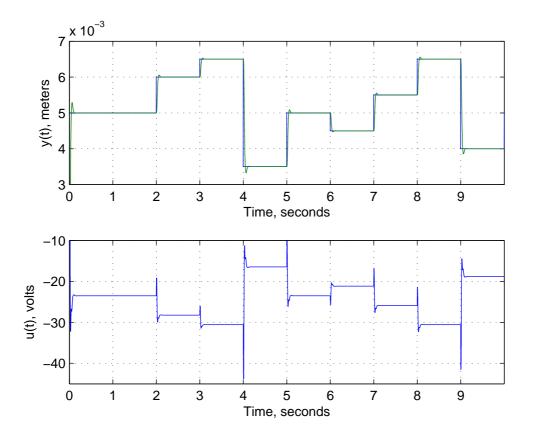

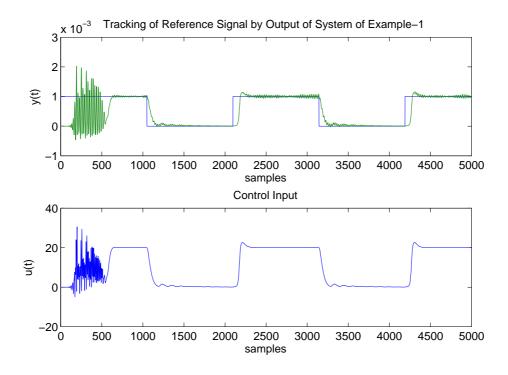

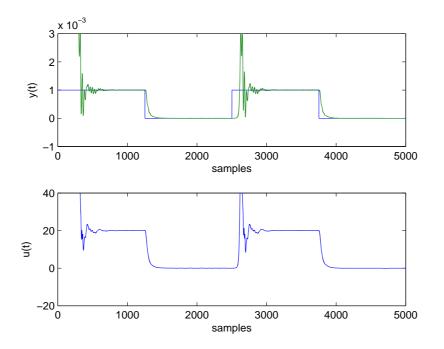

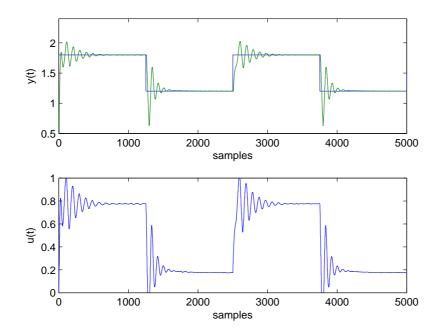

| 6.2  | Tracking performance for Example-1 using multi-bit: Upper graph represents the     |     |

|      | output y(t) and lower graph represents the control input                           | 135 |

| 6.3  | Tracking performance for Example-1 using bit-stream: Upper graph represents the    |     |

|      | output y(t) using bit-stream control and the lower graph represents the real value |     |

|      | interpretation of the bit-stream control input.                                    | 136 |

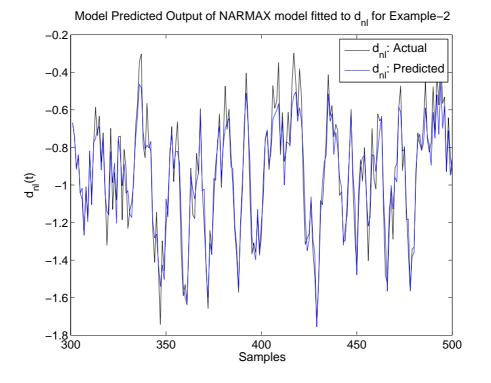

| 6.4  | Model predicted output of the NARMAX model fitted to the unmodelled dynamics       |     |

|      | $d_{nl}$ of Example-2                                                              | 137 |

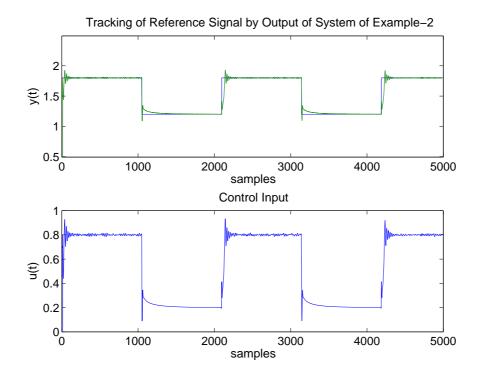

| 6.5  | Tracking performance for Example-2 using multi-bit: Upper graph represents the     |     |

|      | output y(t) and lower graph represents the control input                           | 138 |

| 6.6  | Tracking performance for Example-2 using bit-streams: Upper graph represents       |     |

|      | the output $y(t)$ using bit-stream control and the lower graph represents the real |     |

|      | value interpretation of the bit-stream control input                               | 140 |

# TABLES

| 2.1 | Adder truth table.                                                                                              | 20  |

|-----|-----------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Alternative adder truth table.                                                                                  | 21  |

| 2.3 | Bit-Stream to multi-bit truth table.                                                                            | 25  |

| 2.4 | Type 2 adder truth table.                                                                                       | 28  |

| 2.5 | Adder resource usage                                                                                            | 30  |

| 2.6 | Subtractor truth table                                                                                          | 31  |

| 2.7 | Alternate subtractor truth table.                                                                               | 32  |

| 2.8 | Scale Up decoder truth table.                                                                                   | 37  |

| 3.1 | Optimised GPC parameters obtained via genetic algorithms for D.C. Servo mech-                                   |     |

|     | anism                                                                                                           | 69  |

| 3.2 | Optimised GPC parameters obtained via genetic algorithms for thermal plant with three different transport lags. | 80  |

| 4.1 | Optimised GPC parameters obtained via genetic algorithms for magnetic levitation                                |     |

|     | system.                                                                                                         | 101 |

| 5.1 | Algorithm Result for Duffing's Equation                                                                         | 124 |

| 6.1 | Optimised nonlinear GPC parameters obtained via evolutionary programming for                                    |     |

|     | Example-1                                                                                                       | 134 |

| 6.2 | Optimised nonlinear GPC parameters obtained via evolutionary programming for                                    |     |

|     | Example-2                                                                                                       | 137 |

## CHAPTER 1

## Introduction

## 1.1 Motivation and Rational

Computation is one of the traditions that gave rise to modern analogue electronics [1]. The origins of analogue computing can be traced back to the early 1930's with the mechanical differential analyser [2] which was able to resolve differential equations of up to sixth order. With the technological advancements which followed in the subsequent decades, and the widespread use of transistor technology, analogue circuitry became extremely common in the field of engineering. Moreover, as computation requirements increased, the demand for faster, smaller and more accurate devices increased. Amongst the most popular analogue components of these earlier times were the Operational Amplifiers K2-W, Fairchild  $\mu A709$ , LM101 and OP-07 to name a few [1]. Although the art of analogue circuit design has improved significantly, these circuits have some inherent problems. For example, uncertainty in measurement of values is a well documented effect and analogue circuitry is plagued by it. Some of these include inaccuracies in resistor values, unstable reference voltage and thermal effects [3]. Furthermore, analogue circuitry can be influenced by external radiation, electrostatic noise and other such types of environmental effects.

The technical limitations and imperfections of analogue circuits was an important issue in early years which was resolved due to advancement of digital technology. Many historians have argued that one of the most important driving forces behind technological advances is in the field of communications. A critical landmark that marked the commencement of modern times was the invention of the telephone in the late 1800s, which changed forever the way people interact and shared ideas with one another. The importance of this device is not only attributed to what it accomplished for society, but also for its technological wonder. For the first time in history, a human voice was electronically digitised and successfully decoded back into its original form. In essence, this was the first commercially available *analogue to digital converter*. As decades

passed, and much more technological advancement were merged and discovered, the spectrum of applications for analogue to digital conversion, or ADC/DAC grew exponentially. Analogue to digital converters have evolved to such an unimaginable extend, that a whole new field was created, namely digital electronic systems.

The key characteristic of a digital system is that it only deals with two known possible states. There are many ways to describe these, such as TRUE/FALSE, 1/0, HIGH/LOW or 5.5V/-0.5V, but in essence these are chosen to represent one of the two cases. In this manner, any uncertainty is removed (or rounded). This is where digital systems take their advantage. A digital representation of an audio signal, for example, allows CD players to achieve virtually error free storage using optical disks [4].

A common practice in digital systems is to use binary encoding to interact between different signals. A binary line may consist, for example, of 4 unique lines each of which can represent a true or false value. Using this multi-bit type of encoding it is possible to represent 16 possible states. Arithmetic can be performed in binary-base much like in decimal system. The simple procedure described in this paragraph is the basis of the modern computer.

The advent of the microprocessor in 1970's, gave rise to a new area of control systems: *the digital control systems*. Digital control systems are being used in many applications such as machine tools, metal working processes, chemical processes, aircraft control and automobile traffic control and others [5, 6, 7, 8, 9]. Some of the main advantages of having a completely digital system include: improved measurement sensitivity; the use of digitally coded signals, digital sensors and transducers, and microprocessors; reduced sensitivity to signal noise; and the capability to easily reconfigure the control algorithms in software[10].

With the advancements of Very Large Scale Integration (VLSI) Technology and the widespread availability of low cost digital platforms such as microprocessors and microcontrollers, digital system implementation evolved into the more flexible digital form which is now used almost exclusively [11, 12, 13, 14, 15]. Traditionally, these control systems are implemented using microcontrollers, which perform the required control functions sequentially. However, as the complexity of control algorithms increases to achieve improved functionality and the time available to complete the calculations reduces to keep pace with ever-faster power electronic devices, microprocessor based solutions cannot execute the control program within the available time limit.

A potential solution to this performance limitation is the use of hardware based control systems, which can execute control algorithms extremely quickly because many operations are processed in parallel. This is attractive for use in control systems, but implementing hardware control systems is difficult. The designer must either manually translate the control algorithm into individual operations, which are then usually encoded using a Hardware Description Language (HDL), or employ an automated code generation tool. The code is then synthesised and used to program

#### a Field Programmable Gate Array (FPGA).

An alternative method for implementing digital control systems is by using the bit-stream technique. The concept of 1-bit processing was originally proposed for reducing the silicon area occupied by complex VLSI-based systems[16]. The concept of Sigma-Delta, or 1-bit processing or bit-streams have existed since the middle of the century, however it is only in the last two decades that this method has become more attractive [17, 18, 19]. In contrast to the usual methods of implementing digital controllers, bit-stream control systems are developed using standard schematic editors provided by FPGA manufacturers. Provided that the desired control functions are available in the bit-stream library, the designer need not use HDL to develop the control system.

The application of bit-stream in controller synthesis is relatively new. In recent years, this has been applied to implement simple PI and PID controllers [17, 11, 20, 21, 22]. The use of bit-streams in more complex control algorithms is scarce. Therefore, the objective of this study is to investigate if bit-stream implementation can be considered as a possible alternative to implement advanced controllers due to various advantages this offer.

Amongst various types of controllers, the predictive control method has become one of the most popular control methods in industry and academia [23]. This controller has found a wide range of applications in the process, chemical, food processing and paper industries. Some of the most popular MPC algorithms that have found a wide acceptance in industry are Dynamic Matrix Control (DMC), Model Algorithmic Control (MAC), Predictive Functional Control (PFC), Extended Prediction Self Adaptive Control (EPSAC), Extended Horizon Adaptive Control (EHAC) and Generalised Predictive Control (GPC) [23]. These controllers can be designed either using a discrete parametric model such as CARIMA, ARMAX *et cetera* or by using a state space model [24].

The predictive controller is capable of stable control of processes with variable parameters, with variable dead-time, and with a model order which changes instantaneously provided that the input/output data are sufficiently rich to allow reasonable plant identification[25]. It is effective with a plant which is simultaneously non-minimum phase and open-loop unstable and whose model is over-parameterised by the estimation scheme without special precautions being taken [25]. This controller is therefore being selected for investigating the feasibility of bit-stream implementation. Initially, the performance of a GPC implemented using bit-stream is evaluated considering examples of linear systems and linear systems with delay.

Generalised predictive control has been very successful when the plant is operating in the neighbourhood of the operating point. However, most industrial processes have inherent complex nonlinearities, and these can render the classical GPC algorithm impractical[26]. Thus there is a need to design predictive controllers for nonlinear systems. Many researchers have proposed several methods of designing GPC for nonlinear systems by extending the linear GPC[27, 28, 29,

#### 30, 31, 32].

The first step in designing GPC for nonlinear systems is to select an appropriate model of the system. Although several possible representations of nonlinear systems have been proposed which include traditional functional series of Volterra and Wiener[33], Legendre polynomials[34], neural networks [35, 36] and weighted maps [37], the polynomial Nonlinear Auto Regressive Moving Average with eXogenous inputs (NARMAX) model proposed in [38, 39] provide a concise representation of a wide class of nonlinear systems and has attracted considerable interest during last three decades. Many types of nonlinear models such as Volterra, Hammerstein, Wiener can be considered as a special case of the polynomial NARMAX model [40, 26]. One distinct feature of this model is that it is linear-in-parameters and therefore the parameters associated with different terms can be estimated using simple least squares based algorithms.

However, one of the disadvantages of the polynomial NARMAX models is that the total number of terms increases rapidly with the increase in maximum lag of inputs, outputs, noise terms and degree of nonlinearity. Thus detecting the model structure or which terms to include into the model is extremely important. Amongst several approaches which have been proposed to address this structure selection problem, the Orthogonal Least Squares (OLS) algorithm with Error Reduction Ratio (ERR) introduced in [41] and later modified by Billings and co-workers [42, 43, 44] provides an efficient and elegant solution. The ERR criterion of the OLS algorithm essentially computes the significance of model terms based on their ability to explain the output variance. However, certain linear and nonlinear systems may produce erroneous results [45] as OLS-ERR may select spurious terms.

Parsimonious model structure selection is essentially a complex optimisation problem. With the arrival of faster computing power over the last few decades, Evolutionary Computation (EC) algorithms have become a viable solution for solving complex problems. Evolutionary computing offers insensitivity to mathematical concepts such as differentiability, continuity, optima traps *et cetera* [46]. However, EC algorithms are still in their infancy, especially in the system identification field. Arduous research is currently ongoing in the system identification community [47]. In the present study, a new intelligent structure selection method has been developed to obtain a parsimonious model of nonlinear systems which are represented by polynomial NARMAX model. The robustness of this algorithm is illustrated by successfully identifying three nonlinear systems. Generalised predictive controllers are designed for nonlinear systems using polynomial NARMAX model and implemented in bit-stream.

## **1.2 Objectives of the Thesis**

Although considerable success has been achieved and reported in the use of bit-stream for signal processing applications [48, 49], its application for controller implementation in very limited. Moreover, due to only classical controllers such as P, PI and PID being implemented in bit-streams for various applications [17, 11, 49, 21, 50, 51, 52, 53], there remains several open problems and practical issues that need more attention. Therefore, the main objective of the thesis is to investigate if bit-streams can be considered as a viable alternative to multi-bit implementation of sophisticated controllers. In an attempt to address these issues, existing bit-stream theory, predictive control algorithms and system identification tools will be employed to achieve the following objectives:

- To study the various features of bit-stream functional elements and to test and implement bit-streams on real plants.

- Investigate the performance of generalised predictive controller using bit-streams for linear systems and systems with time delay.

- Investigate the performance of bit-streams for unstable systems.

- Develop new methods of designing generalised predictive controllers for nonlinear system represented by polynomial nonlinear auto regressive moving average with exogenous input (NARMAX) models.

- Investigate the feasibility of a new type of nonlinear generalised predictive controller using polynomial NARMAX representation in bit-streams.

## **1.3 Outline of the Thesis**

The organisation of the thesis proceeds in accordance with the objectives mentioned above.

Following the introduction, Chapter 2 describes the various functional elements, such as bitstream converters, adders, subtractors, multipliers, tapped delay *et cetera*, which are the basic building blocks of a bit-stream system.

Chapter 3 focuses on the design and implementation of generalised predictive controller for linear systems in bit-stream considering two benchmark examples. The general guidelines for successful implementation of bit-stream GPC are presented. The methods of obtaining optimal tuning parameters using genetic algorithm are discussed.

After designing and implanting GPC for stable linear systems, Chapter 4 designs and implements in bit-stream, various types of controllers such as feedback linearising controller, state space based model predictive controller and generalised predictive controller for an unstable magnetic levitation system.

The next objective of the research has been to design and implement nonlinear GPC for nonlinear systems. The first step of this design process is to obtain a nonlinear model of the system. In this study, a nonlinear system is modelled by a polynomial NARMAX model. Therefore, Chapter 5 proposes a new structure selection algorithm to select significant terms of the model using evolutionary programming.

In Chapter 6, a novel GPC is designed for a class of nonlinear systems which are represented by polynomial NARMAX model. This controller is designed and implemented in bit-stream considering several examples of complex nonlinear systems. The conclusions and future work are presented in Chapter 7.

## CHAPTER 2

## **Bit-Streams - An Introduction**

The traditional approach of digital signal processing is based on converting the analogue signals to digital using multi-bit A/D converters. All the computations in the digital processors are essentially executed using finite wordlength, typically 8-bit, 16-bit or 32-bit. Higher number of I/O pins are required to route these multi-bit signals and therefore consumes more silicon area. In order to reduce the silicon area and number of logic elements, researchers have proposed an alternate method of signal processing. This is called 1-bit or bit-stream processing which was initially proposed in [48]. This method offers significant advantages over multi-bit approach [54].

Generally, bit-stream technique has been exploited by many researchers in various fields including audio signal processing, neural networks [55, 56, 57, 58, 59], communication systems [48], power electronics [50, 60, 61], and nano-electronics [62, 63]. Concept of bit-stream and bitstream based processing, which was initially restricted to signal processing application is now becoming popular in control applications. However, the bit-stream based system consists of several functional blocks and there interconnections. This chapter describes briefly about the key function blocks which are used in implementing controllers for both linear and nonlinear systems.

## 2.1 Analogue and Digital Conversion in Bit-stream

The theory of bit-streams has been in existence for many years, but only with recent technological advances in semiconductor devices has their use become widespread [64]. The introduction of bit-stream signal processing for control purposes is a relatively new concept [11]. This type of encoding may be found under several names: Bit-streams, Sigma-Delta conversion,  $\Delta\Sigma$  modulation and 1-bit processing. To understand how bit-stream can be used to represent signals, it is important to first understand the relationship between analogue and digital domains.

Figure 2.1: A continuous signal (A) and a discrete signal (B).

A continuous signal contains infinite information. In order to take advantage of modern computational power, a signal must first be discretised. This offers several advantages to a signal, such as [65]

- Reduced cost over analogue devices.

- Noise immunity.

- Flexibility in response to design changes.

The last item in the above list truly represents the main advantage of a discrete system. In complex systems, where analogue control is utilised, the adjustments of parameters may not be a trivial one. Such an adjustment may require the physical replacement of key components. Instead, by using digital circuitry the complete algorithms can be changed simply by re-configuring a device or via updating software.

However, analogue signal can never be avoided. Discretisation of signal will always involve Analogue to Digital (ADC) and Digital to Analogue (DAC) conversions. Therefore, DACs and ADCs are inherent components of any digital control system.

### 2.1.1 Signal Encoding

Consider a continuous time signal presented in Figure 2.1-A. A generic signal such as this one can be discretised by the use of a *zero-order sample and hold* and this yields the staircase signal shown in Figure 2.1-B. Each one of the particular stair *levels* is set to represent a specific digital number, which is read at each sample time  $t_s$ . For example, if the number of levels is 16, then a 4-bit word can be used for representation. That is, a 4-bit word is obtained at every sample time  $t_s$ .

Conventional digital systems have generally used this type of multi-bit lines to transfer control information by using multi-bit words that are output from ADCs. This typical approach is utilised by

**Figure 2.2:** Canonical control system using multi-bit encoding:  $A_d$  is an n-bit digital signal converted to analogue, and  $A_i$  is the analogue plant output to be digitised.

many control schemes and it is shown in Figure 2.2. A major drawback of multi-bit systems is the requirement for conversion hardware. Such hardware suffers from decimation and interpolation limitations. The bit-resolution of such devices could be increased to reduce quantisation errors, but this causes the number of logic elements to increase dramatically. Another problem is the large amount of digital lines required to source the data out from a digital device and onto an analogue port. Moreover, these problems escalate severely with increasing complexity of the system.

However, it is possible to conceive that a digital system need not be of a base-*n*, but rather of a binary base. Looking at the example above, instead of using 4 individual lines to represent a word, a single line with a faster sampling rate can be used to push the bit information without packages by serialising and adjusting the binary weight of the stream. Moreover, this implies that the resolution of the value is now a factor of the sampling time. The intricacies of this method will be further described in this chapter.

## 2.2 The Concept of Bit-streams

To solve some of the problems inherent to multi-bit processing, a bit-stream signal paradigm using  $\Delta\Sigma$  modulation has been proposed [49]. With the recent spread of hardware description language such as Verilog and VHDL and the development of advance compilers, the threshold of hardware design is becoming lower [66]. Essentially, the digital signal  $\Delta\Sigma$  modulator will output a Pulse Width Density (PWD), which works similar to Pulse Width Modulation (PWM).

A bit-stream control system can be used for control purposes eliminating many unnecessary conversion. This idea is shown in Figure 2.3. Here, the component labelled  $\Delta\Sigma$  represents an analogue to bit-stream modulator. On the controller side, a  $\Delta\Sigma$  modulator is also included, however this is only an indication since the system itself will inherently contain bit-stream component and therefore no conversion should be needed. The  $\Delta\Sigma$  modulator produces a PDM signal that can be fed into the physical system. The analogue system output is passed through a  $\Delta\Sigma$  bit-

**Figure 2.3:** Bit-stream encoding for control system:  $A_i$  is the analogue plant output to be digitised and PDM is the control action.

stream converter which is then fed back into the controller. This type of set up provides many advantages over *n*-bit encoding. As mentioned earlier, an unnecessary encoding layer may be removed by the introduction of a  $\Delta\Sigma$  modulator. These modulators can be used to directly output a bit-stream signal from an analogue signal. This enables the use of a single digital line to transfer all the encoding information. Moreover, it is more convenient to think of digital devices in terms of single-bit arithmetic, since these operate using binary systems.

The propose work expands the concept of bit-streams for control purposes by testing its effectiveness using real plants. This chapter will introduce the theoretical groundwork of bit-streams and many of the tools that are used in later chapter to create controllers.

#### 2.2.1 Quanta

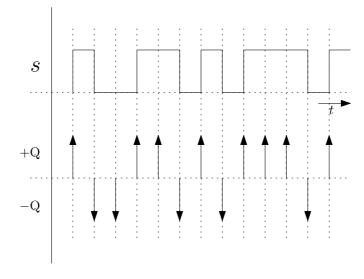

A bit-stream is a made up of collection of positive or negative quanta. Strictly, a bit-stream is a binary signal with logic levels '1' and '0', that can be used to represent any bipolar analogue level. Logic '1' present a positive quantum +Q and logic '0' represents a negative quantum -Q. The injection of a quanta into a bit-stream will adjust the signal level in accordance to the quanta sign. Figure 2.4 shows bit-stream signal *S* and positive quantum impulse +Q and negative quantum impulse -Q.

#### 2.2.2 A Zero Magnitude Bit-Stream

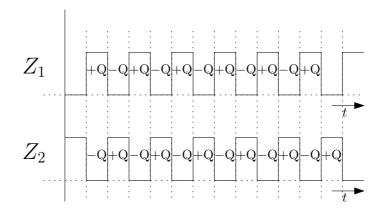

The alternation between a positive and a negative quanta (i.e. logic '1' and logic '0') results in the cancelation of the over all incident quanta thus resulting in a zero value. Figure 2.5 contains two types of zero signal  $Z_1$  and  $Z_2$ . It can be seen that a single or multiple bit delays does not affect the magnitude.

Figure 2.4: A typical bit-stream signal.

Figure 2.5: A zero magnitude bit-stream signal.

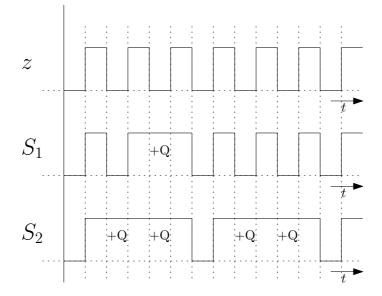

**Figure 2.6:** Positive magnitude bit-stream signals  $S_1$  and and  $S_2$  synchronised with signal z.

#### 2.2.3 Non-Zero Magnitude Bit-Streams

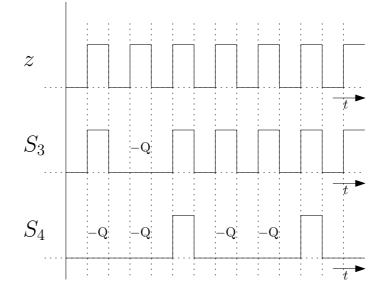

Consider a zero level signal with some of its negative quanta inverted to positive. In this case, the overall net value of the bit-stream has changed positively compared to the original zero value signal. Figure 2.6 shows zero signal, z, a signal  $S_1$  as a zero signal with one negative quantum being inverted and signal  $S_2$  as a zero signal with four negative quanta being inverted. As the amount of negative inverted quanta increases, the magnitude of the overall bit-stream increases positively. Figure 2.7 shows the same concept, albeit with signals  $S_3$  and  $S_4$  as negatively valued bit-streams.

#### 2.2.4 Multi-Bit Binary Word

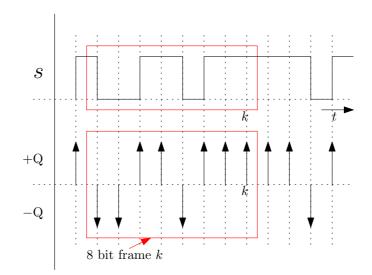

The concept of a frame is introduced here. A frame contains the quanta summation from N past samples. This is shown in Figure 2.8 where a red box is shown to encompass the current quantum k as well as the seven previous quanta. This is known as an 8-bit frame. The frame captures five positive quanta and three negative quanta, thus the overall frame value is 5-3 = 2. Since there are 8-bits in one frame, the resolution is 1/8 and hence its overall value is 2/8. In a bi-polar sense (four positive level and four negative levels) this number actually represents +1/4. If another signal were to contain six positive quanta, then similarly 6-2 = 4 which equals 4/8 or +1/4 in a bi-polar sense. Similarly, if the frame contained seven negative quanta, then 1-7 = -6, -6/8 or -3/4. It is worthwhile noting the relation between positive and negative quanta within a frame. If an 8-bit frame contains six positive quanta, then it must contain two negative quanta. Also, the number of possible states can be seen as  $+Q \times 4, -Q \times 4$  plus one zeros state signal. If more resolution is required, then a bigger frame must be considered.

Figure 2.7: Negative magnitude bit-stream signals  $S_1$  and and  $S_2$  synchronised with signal z

Figure 2.8: An 8-bit frame encompassing a bit-stream signal.

**Figure 2.9:** Instantaneous value of a bit-stream signal: Blue frame shows frame at k, red frame shows frame at k + 1.

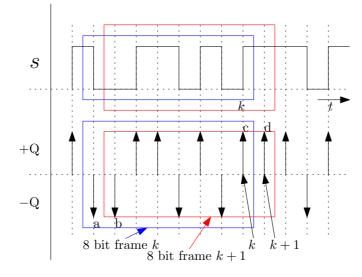

#### 2.2.5 Instantaneous Value

The instantaneous value of a bit-stream can be seen from the extension of the frame concept introduced in §2.2.4 and is shown in Figure 2.8. By evaluating the quanta contained within each frame at every clock pulse it is possible to obtain the instantaneous bit-stream value at time k. This concept will be illustrated in Figure 2.9 using the same examples presented in Figure 2.4 and Figure 2.8. The amount of quanta within the blue 8 bit frame up to the current sample k has the bi-polar value of +1/4 (5 positive, 3 negative quanta). Moving the frame one sample forward to k + 1 the quanta is now +2/4 (6 positive, 2 negative quanta).

The relationship to an analogue input can be seen in the following operation

$$V_i(k) = \frac{A(k) - B(k)}{N}$$

(2.1)

where  $V_i(k)$  is the analogue value at instant k, A(k) is the positive quanta, B(k) is the negative quanta and N is the number of cycles of the bit clock.

#### 2.2.6 Magnitude and Range

All components within the digital logic realm require a clock signal for synchronisation. Since a *zero* bit-stream is simply a square wave of frequency one half the bit rate, it is possible to derive this signal from the global clock. This is very beneficial since it will require minimal additional components.

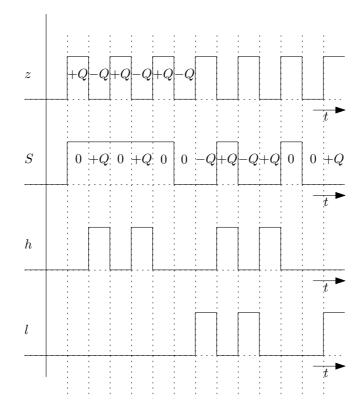

A comparative operation can be performed on bit-streams to identify their sign of the incident

**Figure 2.10:** Synchronised decoding for a bit-stream magnitude. Zero signal z is used to decode bit-stream S to obtain incident quanta h or ejected quanta l.

quanta. Let *S* be the bit-stream under consideration and *z* denote a zero level bit-streams. Comparing all the states in *S* to those of *z* will tells us that *S* is also a zero level signal. Conversely, if the state of *z* is logic '0' and *S* is at logic '1', then *S* is positive by one quantum at that instant. Another way of saying this is that an additional positive quantum can only be inserted when *z* is at logic '0'. The incidence of an additional positive quantum is given by

$$h = S \wedge \bar{z} \tag{2.2}$$

where S is the bit-stream under consideration and z is the zero value signal. Is should be noted that h is active only when positive quanta in addition to those already in z are present in S. This is shown in Figure 2.10. Similarly if z is at logic '1' and S is at logic '0' then S is negative by one quantum at that instant. This can be represented by

$$l = \bar{S} \wedge z \tag{2.3}$$

The signals h and l are used for operation within functional elements, later described in §2.3. Lastly, it should be noted that these operations are shift independent, as the interchanging in logic of the l and h bit-streams will still produce a zero value.

Intuitively, a 4 bit word contains 16 different states. Using unipolar representation all the binary states from  $0000_2$  to  $1111_2$  can be mapped to a distinct value. Two's complement can be used for

bipolar representation. This is where the most significant bit is used as a positive/negative (0/1) flag,  $0001_2$  to  $0111_2$  as positive and  $1000_2$  to  $1111_2$  as negative, while  $0000_2$  remains zero valued. The advantage of this representation is in addition and subtractions, since these operations require no adjustment from the normal procedures. It is worth noting that the effective 4 bit range has shift to include negative numbers. That is, a range of [0,15] for unipolar and [-8,7] for bipolar.

# 2.3 Bit-Stream Functional Elements

The aim of this thesis is to implement complex control algorithms using bit-streams. For this purpose, simple arithmetic operations must be performed using bit-stream. Therefore, the correct implementation of these low level operations are key for successful implementation of a digital controller.

## 2.3.1 Synchronisation

As with most digital components, synchronisation is extremely important. All functional elements must contain a synchronous clock, reset and bit-stream inputs and outputs. For the design of a functional element, it should be noted that all inputs and outputs must be of type bit-stream. Where appropriate, some elements may contain binary constants as for scaling purposes.

Implementation of these building blocks will be simulated in Mentor Graphics' ModelSim<sup>TM</sup>. Upon successful simulation, the blocks are then downloaded into a DE2 Development and Education Board shown in Figure 2.11, using Quartus II 10.0. The DE2 Board contains a Cyclone II EP2C35F672C6 with EPCS16 16-Mbit serial configuration device FPGA. Some of the terminology for the design of bit-streams is shown below.

- 1. ggclock, is the fastest clock within the device.

- 2. gclock, is half of ggclock and used for the calculations of bit-stream operations.

- 3. z, is the clock rate of a zero valued bit-stream.

- 4.  $f_B$ , is the bit-stream frequency. This is also equal to *gclock*.

- 5. init, is a reset/enable trigger.

The following sections briefly describes some of the already existing bit-stream elements [17].

Figure 2.11: The Altera DE2 development and education board.

## 2.3.2 Analogue to Bit-Stream Conversion Theory

Let  $V_i(t)$  be an analogue input and  $V_i(k)$  be its bit-stream counterpart. The true value of  $V_i(t)$  can be evaluated by integrating over a the  $NT_B$  interval as show below.

$$\int_{T-NT_B}^{T} V_i(t) = T_B \sum_{i=k-N}^{i=k} D(i)$$

(2.4)

where  $D_N(k)$  is the value of the duty cycle at sample interval k and the resolution is give to be one part in N (usually taken to be  $N = 2^R$  where R is the effective resolution). If the value for  $V_i(t)$  is kept constant then  $V_a$  can be show to be

$$V_a = \frac{\sum_{k=N}^k D(i)}{N} \tag{2.5}$$

D(i) can be written in terms of positive and negative quanta. If a(i) represents the positive quanta and b(i) the negative quanta, then

$$V_a(k) = \frac{\sum_{k=N}^{k} [a(i) - b(i)]}{N}$$

(2.6)

and let  $\sum_{k=N}^{k} a(i)$  be  $A_N(k)$ ,  $\sum_{k=N}^{k} b(i)$  be  $B_N(k)$  and  $\sum_{k=N}^{k} D(i)$  by  $[A_N(k) - B_N(k)]$  then

$$V_a(k) = \frac{A_N(k) - B_N(k)}{N} = \frac{D_N(k)}{N}$$

(2.7)

In summary, this expression represents the sampled analogue input signal  $V_i(k)$ , known as  $V_a(k)$  in terms of positive and negative quanta with a resolution of one part in N. Note the following special cases: