#### http://researchspace.auckland.ac.nz

#### ResearchSpace@Auckland

#### **Copyright Statement**

The digital copy of this thesis is protected by the Copyright Act 1994 (New Zealand).

This thesis may be consulted by you, provided you comply with the provisions of the Act and the following conditions of use:

- Any use you make of these documents or images must be for research or private study purposes only, and you may not make them available to any other person.

- Authors control the copyright of their thesis. You will recognise the author's right to be identified as the author of this thesis, and due acknowledgement will be made to the author where appropriate.

- You will obtain the author's permission before publishing any material from their thesis.

#### General copyright and disclaimer

In addition to the above conditions, authors give their consent for the digital copy of their work to be used subject to the conditions specified on the <u>Library Thesis</u> <u>Consent Form</u> and <u>Deposit Licence</u>.

## ACCELERATION OF ODE-BASED BIOMEDICAL SIMULATIONS WITH RECONFIGURABLE HARDWARE

TING YU

Supervised by Dr Oliver Sinnen and Dr Chris Bradley

A thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy in Electrical and Electronic Engineering, the University of Auckland, 2015.

Ting Yu: Acceleration of ODE-Based Biomedical Simulations with Reconfigurable Hardware © 2015

### ABSTRACT

Biomedical models and simulations often require high performance computing environments. For example, simulating one minute of electrical activity of a human heart may require more than one month of computation time with today's fastest processor. Biomedical models often are based on ordinary differential equations (ODEs) which require numerical integration during the simulation. The numerical integration is regular and easy to parallelise. Parallel systems that consist of a large number of general purpose processors (GPPs) and graphics processing units (GPUs) as accelerators have been traditionally used for these types of simulations. However, such systems usually involve high financial cost and energy consumption. Given the inherent parallelism and high computational requirements, FPGAs (Field Programmable Gate Arrays) with their high parallel architecture and flexibility, are promising for accelerating these kind of computations, whilst being power efficient.

FPGAs are highly configurable devices with logic blocks and interconnects. The logic blocks are programmable and can incorporate parallelism into arbitrary digital circuits such as being arranged into pipelines or replicated for task and data parallelism. However, FPGAs are not widely adopted by biomedical scientists due to their lack of hardware expertise. Furthermore, FPGAs have a limited usable area and so design tool chains can create problems when implementing large sized biomedical models.

To overcome these obstacles and to exploit the potential of FPGAs, this thesis investigates the automatic generation of digital hardware for the domain of biomedical models that can be described as ODEs. The hardware accelerator is based on a pipelined architecture with a hardware/software co-design system. ODoST, an ODE-based domain-specific sythesis tool, is proposed. The tool is capable of automatically generating a FPGA-based hardware accelerator module (HAM) from a high-level description of a mathematical model. This tool will be of benefit to biomedical scientists and engineers without hardware design expertise. In addition, a list of optimisation strategies are investigated and implemented in order to maximise the use of a target FPGA device with limited resources.

The experimental evaluation on real hardware shows that FPGAs deliver a much higher power efficiency than CPU and GPU implementations. Furthermore, FPGA implementations have a significant performance advantage compared to multicore implementations and a comparable processing speed to GPU implementations.

#### ACKNOWLEDGMENTS

It would not have been possible to complete this thesis without the help and support from a number of people.

I would like to sincerely express my gratitude to my supervisors Dr Oliver Sinnen and Dr Chris Bradley for their guidance and inspiration over the past couple of years. Without their constant supervision, encouragement and great support throughout the years, I would not have been where I am now.

I am grateful to all members of the Parallel and Reconfigurable Computing group (PARC) for their generosity in sharing knowledge and experience in work and life.

I would like to acknowledge the financial support I have received during the work. This work has been supported by the Tertiary Education Commission (TEC) and the Auckland Bioengineering Institute (ABI) under the Bright Future Enterprise Scholarship and University of Auckland under a University of Auckland Doctoral Scholarship.

Finally, I must thank my friends for their help and support, especially Wendy for proof-reading my thesis chapters and offering grammatical assistance. Most importantly, I should thank my beloved husband, Yang, and my parents for their understanding and believing in me, for helping me get through the difficult times, and for all the emotional support and caring they provided.

## CONTENTS

#### 1 INTRODUCTION

1.1Biomedical Modelling and Simulation1

1

- 1.1.1Biomedical Modelling with CellML2

- 1.1.2 Biomedical Simulation with OpenCMISS 9

- 1.2 Hardware Acceleration with Reconfigurable Hardware 11

- 1.2.1 Hybrid Acceleration System 12

- 1.2.2 Field Programmable Gate Arrays 12

- 1.2.3 PCI Express 17

- 1.2.4 Floating Point Unit 19

- 1.3 High-level Synthesis 24

- 1.3.1 Benefit 24

- 1.3.2 Design Processes 25

- 1.4 Thesis Motivation and Contributions 26

- 1.4.1 Motivations 26

- 1.4.2 Contributions 28

- 1.5 Thesis Structure 29

- 2 HARDWARE ACCELERATOR MODULE 31

- 2.1 Introduction 32

- 2.2 Related Work 34

- 2.3 CellML Hardware Model 35

- 2.3.1 A Motivating Example 35

- 2.3.2 Model Overview 35

- 2.3.3 Pipelined Floating Point Operations 38

|   |     | 2.3.4 Th   | e Hardware Model Architecture 41       |  |

|---|-----|------------|----------------------------------------|--|

|   | 2.4 | System De  | rstem Design and Implementation 42     |  |

|   |     | 2.4.1 Ov   | erall System Architecture 42           |  |

|   |     | 2.4.2 Ho   | st Computer Design 43                  |  |

|   |     | 2.4.3 FP   | GA Design 43                           |  |

|   | 2.5 | Experime   | nts 46                                 |  |

|   |     | 2.5.1 Ex   | perimental Setup 46                    |  |

|   |     | 2.5.2 Sy   | nthesis Results 47                     |  |

|   |     | 2.5.3 Per  | formance comparison 49                 |  |

|   |     | 2.5.4 Dis  | scussion 49                            |  |

|   | 2.6 | Conclusio  | ns 51                                  |  |

| 3 | ODE | -BASED D   | OMAIN-SPECIFIC SYNTHESIS TOOL53        |  |

|   | 3.1 | Introducti | on <u>54</u>                           |  |

|   | 3.2 | Related W  | Vork 56                                |  |

|   | 3.3 | Biomedica  | al Hardware Accelerator Module 58      |  |

|   |     | 3.3.1 A    | Motivating Example 58                  |  |

|   |     | 3.3.2 Bio  | omedical Model Overview 58             |  |

|   |     | 3.3.3 Pip  | belined Floating Point Operations 62   |  |

|   |     | 3.3.4 Ha   | rdware Accelerator Module Architecture |  |

|   | 3.4 | ODE-base   | d High-level Synthesis 70              |  |

|   |     | 3.4.1 OI   | DoST Overview 71                       |  |

|   |     | 3.4.2 Inp  | out Model Format 73                    |  |

|   |     | 3.4.3 An   | alysis Phase 74                        |  |

|   |     | 3.4.4 Ge   | neration Phase 79                      |  |

|   |     | 3.4.5 Sys  | stem Integration 87                    |  |

|   | 3.5 | Evaluation | n 88                                   |  |

|   |     | 3.5.1 Mc   | odels 89                               |  |

|   |     | 3.5.2 Ex   | perimental Setup 90                    |  |

|   |     | 3.5.3 Sy   | nthesis Results 92                     |  |

|   |     | 3.5.4 Per  | formance Results 95                    |  |

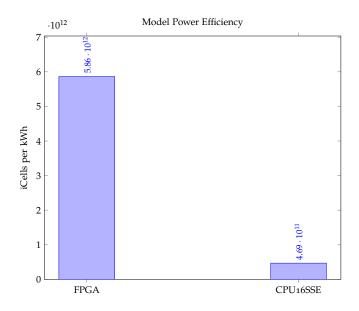

|   |     | 3.5.5 Po   | wer Efficiency 100                     |  |

|   | 3.6 | Conclusio  | ns 102                                 |  |

65

| 4 | PER | FORM   | ANCE OPTIMISATION AND RESOURCE UTILISATION 103 |

|---|-----|--------|------------------------------------------------|

|   | 4.1 | Introc | luction 104                                    |

|   | 4.2 | Relate | ed Work 106                                    |

|   | 4.3 | HAM    | and ODoST 108                                  |

|   |     | 4.3.1  | Biomedical Model Overview 108                  |

|   |     | 4.3.2  | Hardware Accelerator Module 109                |

|   |     | 4.3.3  | ODE-based Domain Specific Synthesis Tool 110   |

|   | 4.4 | Comp   | oiler Optimisation 111                         |

|   |     | 4.4.1  | Local Optimisations 112                        |

|   |     | 4.4.2  | Common Subexpression Elimination 114           |

|   |     | 4.4.3  | Higher-order powers 114                        |

|   |     | 4.4.4  | Exponential Function Simplification 115        |

|   |     | 4.4.5  | Source-to-source Optimiser 116                 |

|   | 4.5 | Resou  | rce Fitting and Balancing 117                  |

|   |     | 4.5.1  | FPGA Resource Capacity 118                     |

|   |     | 4.5.2  | Floating Point Cores 119                       |

|   |     | 4.5.3  | Resource Allocation Techniques 121             |

|   | 4.6 | Multi  | ple Pipelines 127                              |

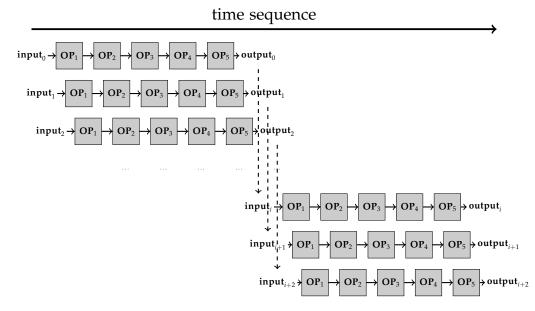

|   |     | 4.6.1  | Single Pipeline 128                            |

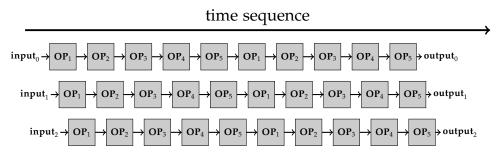

|   |     | 4.6.2  | Extended Pipeline 129                          |

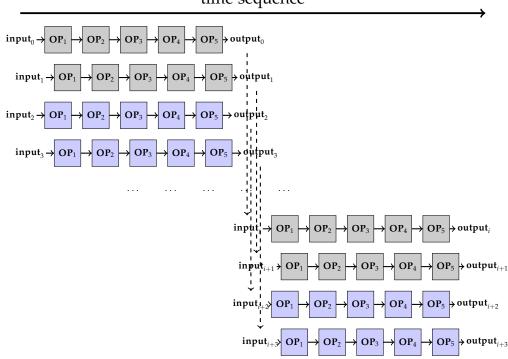

|   |     | 4.6.3  | Parallel Pipelines 130                         |

|   |     | 4.6.4  | Implementation 131                             |

|   | 4.7 | Evalu  | ation 132                                      |

|   |     | 4.7.1  | Experimental Setup 132                         |

|   |     | 4.7.2  | Synthesis Results 135                          |

|   |     | 4.7.3  | Performance Results 139                        |

|   |     | 4.7.4  | Power Efficiency 141                           |

|   | 4.8 | Concl  | usions 145                                     |

| 5 | CON | ICLUSI | IONS 147                                       |

| A | EXA | MPLE   | CELLML MODELS 151                              |

|   | A.1 | Hodg   | kin-Huxley Model 151                           |

A.1.1 Mathematics 151

- A.1.2 C-code Representation 153

- A.2 Beeler-Reuter Model 155

- A.2.1 Mathematics 155

- A.2.2 C-code Representation 157

- A.3 Hilemann-Noble Model 161

- A.3.1 Mathematics 161

- A.3.2 C-code Representation 166

- A.4 TNNP Model 175

- A.4.1 Mathematics 175

- A.4.2 C-code Representation 183

BIBLIOGRAPHY 195

## LIST OF FIGURES

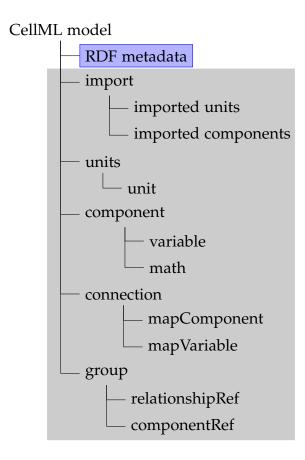

| Figure 1.1  | CellML model structure 3                                     |

|-------------|--------------------------------------------------------------|

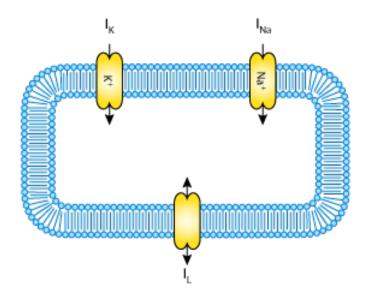

| Figure 1.2  | A schematic cell diagram describing the Hodgkin-Huxley       |

|             | model 5                                                      |

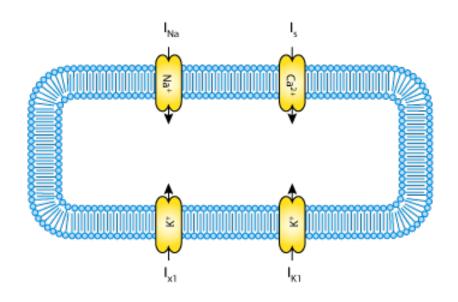

| Figure 1.3  | A schematic diagram describing the Beeler-Reuter model 6     |

| Figure 1.4  | A schematic diagram describing the Hilemann-Noble            |

|             | model 7                                                      |

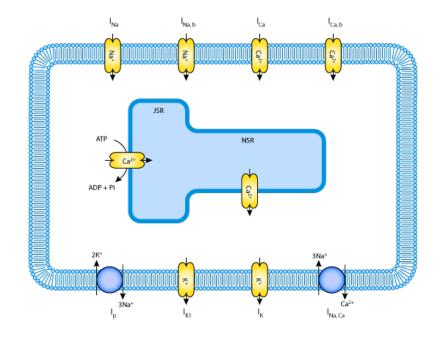

| Figure 1.5  | A schematic diagram describing the model of human            |

|             | ventricular myocyte 9                                        |

| Figure 1.6  | Typical hybrid hardware acceleration system. 12              |

| Figure 1.7  | Stratix IV FPGA architecture 14                              |

| Figure 1.8  | Stratix IV FPGA ALM 14                                       |

| Figure 1.9  | Altera's FPGA application design flow 16                     |

| Figure 1.10 | PCI express layered architecture 17                          |

| Figure 1.11 | IP compiler for PCI express with Avalon-MM interface 20      |

| Figure 1.12 | IEEE-754 floating point format 21                            |

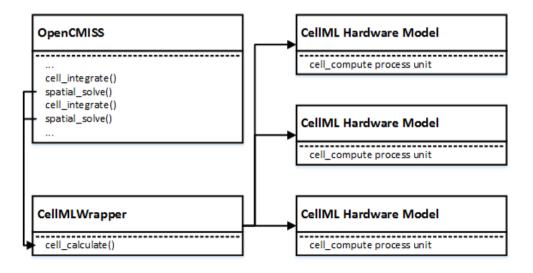

| Figure 2.1  | Abstract view of model interaction 38                        |

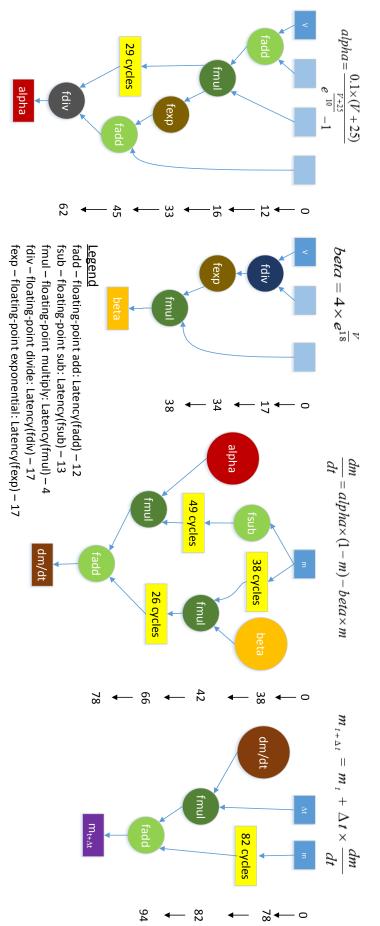

| Figure 2.2  | Pipeline scheduling for <i>sodium_channel_m_gate</i> compon- |

|             | ent 40                                                       |

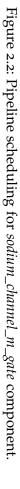

| Figure 2.3  | CellML hardware model core structure 41                      |

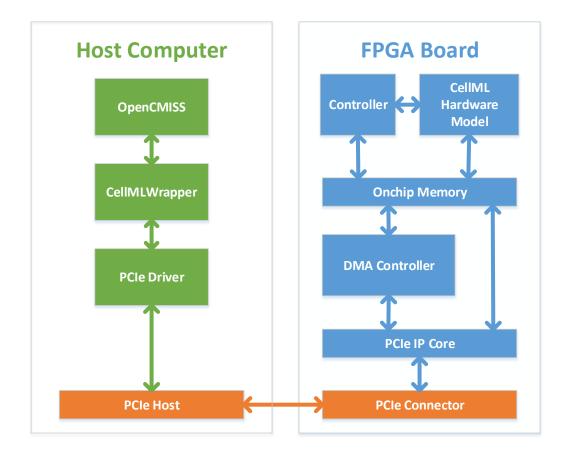

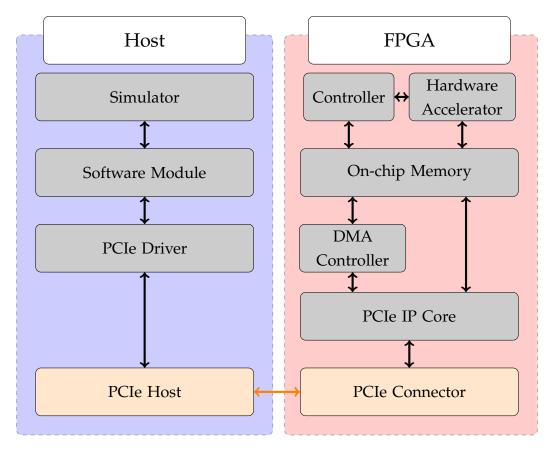

| Figure 2.4  | A block diagram of the overall system architecture 42        |

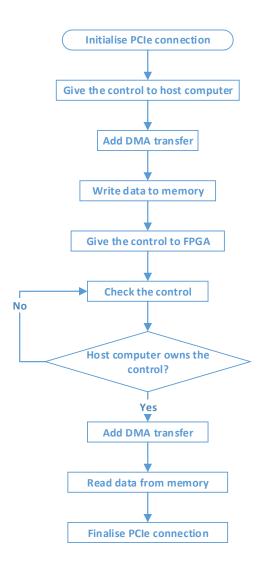

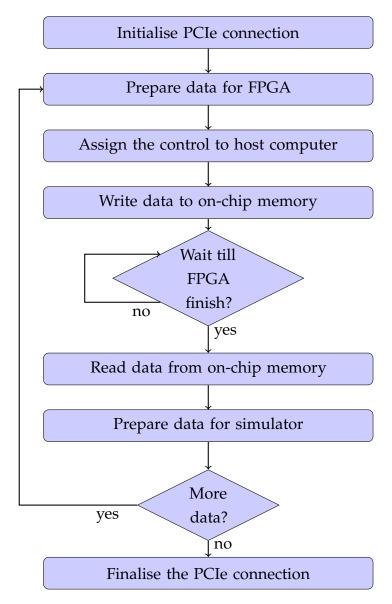

| Figure 2.5  | Flow of <i>CellMLWrapper</i> 44                              |

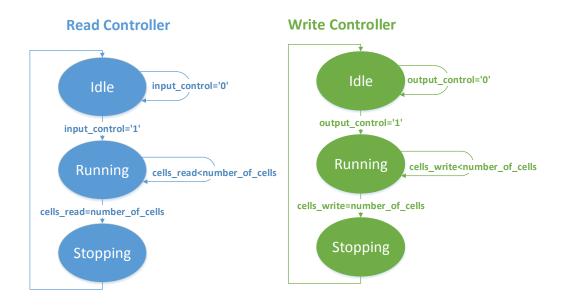

| Figure 2.6  | State machines for read and write controllers 45             |

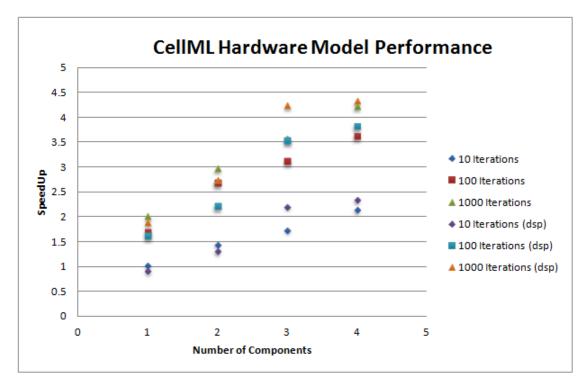

| Figure 2.7  | Performance results of CellML hardware model compu-           |

|-------------|---------------------------------------------------------------|

|             | tation 50                                                     |

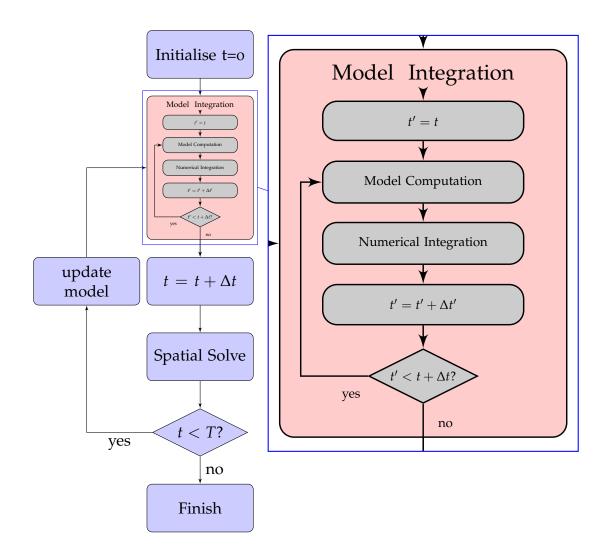

| Figure 3.1  | General flow of model computation 61                          |

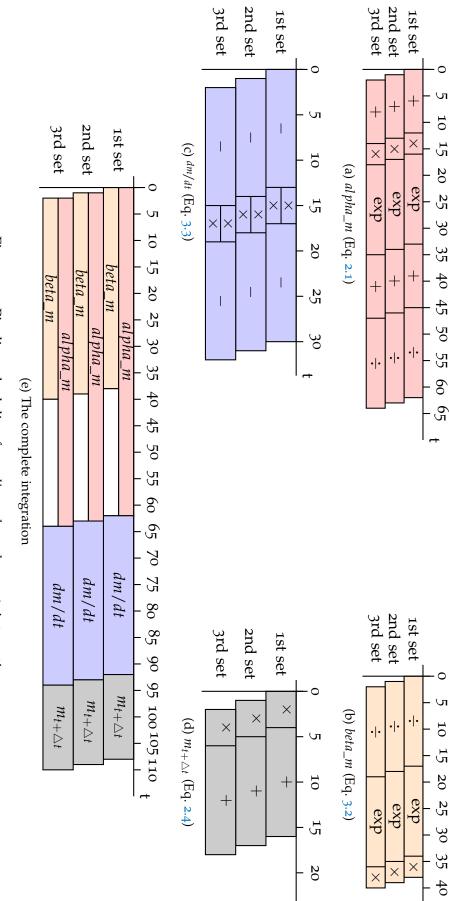

| Figure 3.2  | Pipeline scheduling for <i>sodium_channel_m_gate</i> integra- |

|             | tion 64                                                       |

| Figure 3.3  | Hardware accelerator module system architecture 66            |

| Figure 3.4  | Flow of software module 67                                    |

| Figure 3.5  | State machine for hardware data control 69                    |

| Figure 3.6  | Hardware accelerator structure 71                             |

| Figure 3.7  | Overview of ODoST 72                                          |

| Figure 3.8  | Design flow of ODoST 72                                       |

| Figure 3.9  | C representation of model 73                                  |

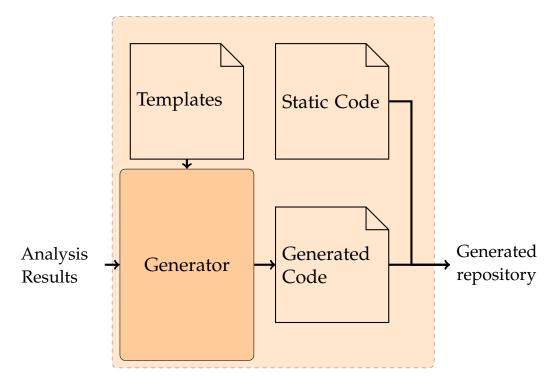

| Figure 3.10 | Generation structure 80                                       |

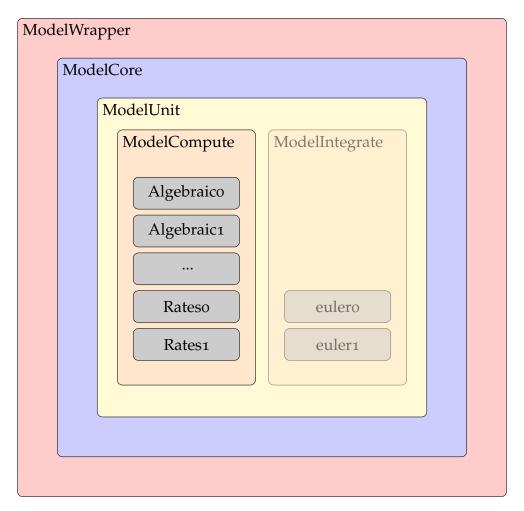

| Figure 3.11 | Hardware accelerator nested framework 81                      |

| Figure 3.12 | Templated entity declaration 82                               |

| Figure 3.13 | Internal signals declaration 82                               |

| Figure 3.14 | Signal shifting 83                                            |

| Figure 3.15 | Operations initiation and mapping 83                          |

| Figure 3.16 | Equations initiation and mapping 84                           |

| Figure 3.17 | On-chip memory allocation 86                                  |

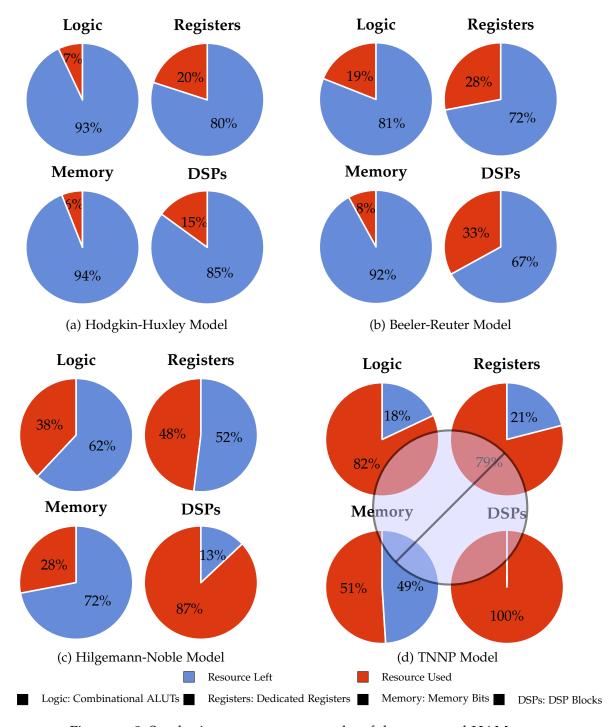

| Figure 3.18 | Synthesis resource usage results of the generated HAMs 93     |

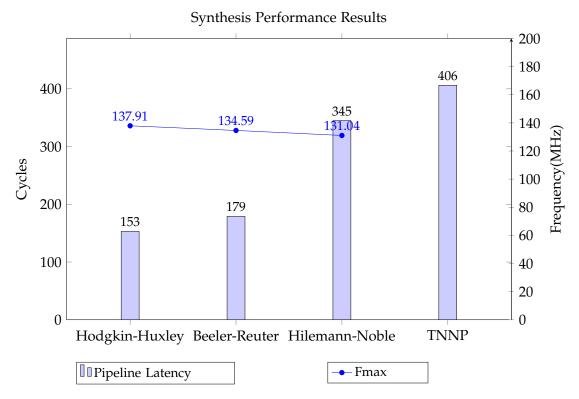

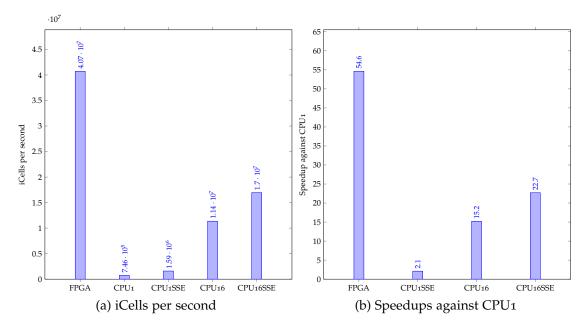

| Figure 3.19 | Synthesis performance results of the generated HAMs           |

|             | with their pipeline latencies 94                              |

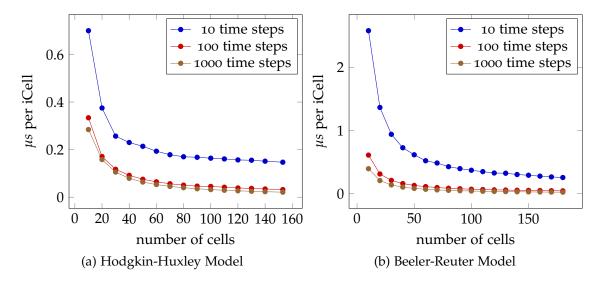

| Figure 3.20 | Average execution time per iCell of the HAMs over num-        |

|             | ber of cells and micro time steps 96                          |

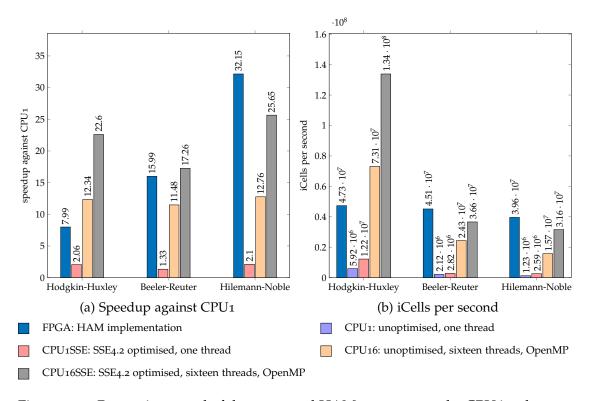

| Figure 3.21 | Processing speed of the generated HAMs compare to             |

|             | the CPU implementations 98                                    |

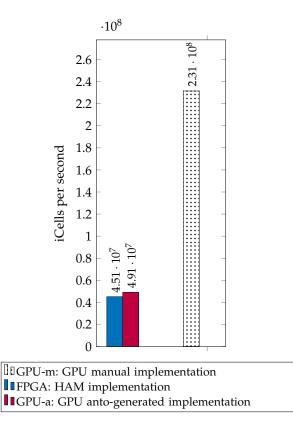

| Figure 3.22 | Processing speed of the HAM for the Beeler-Reuter model       |

|             | compared to the GPU implementations 98                        |

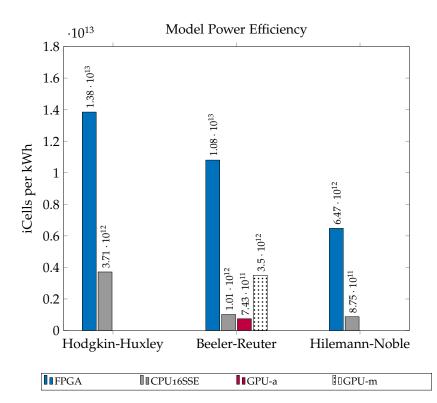

| Figure 3.23 | Power consumption of the generated HAMs compared              |

|             | to the CPU and GPU implementations 101                        |

| Figure 4.1  | Hardware accelerator module system architecture 110           |

- Figure 4.2 Exemplary transformations done by LLVM 113

- Figure 4.3 Single pipeline flow 128

- Figure 4.4 Extended pipeline flow 129

- Figure 4.5 Parallel pipeline flow 131

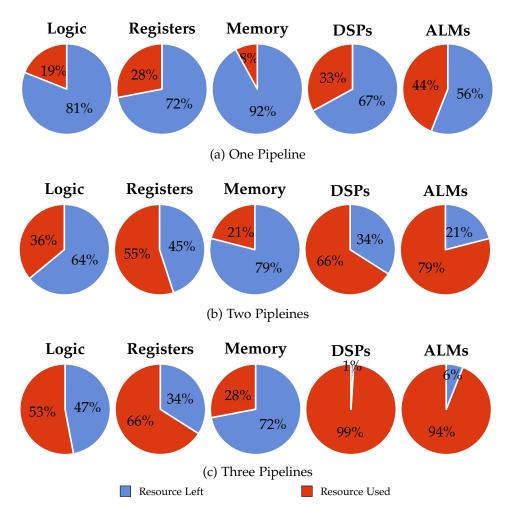

- Figure 4.6 Synthesis resource usage results of the HAMs for the Beeler-Reuter model 136

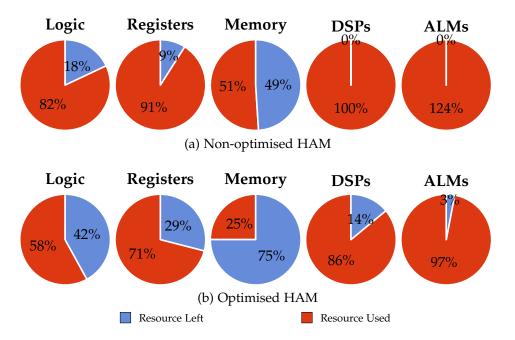

- Figure 4.7 Synthesis resource usage results of the non-optimised and optimised HAMs for the TNNP model 138

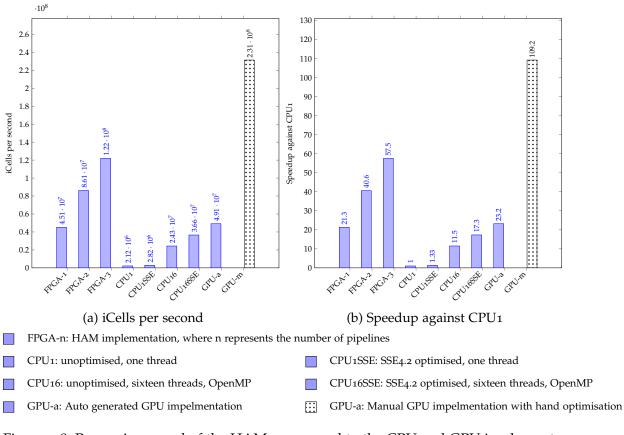

- Figure 4.8 Processing speed of the HAMs compared to the CPU and GPU implementations for the Beeler-Reuter model 140

- Figure 4.9 Processing speed of the HAMs compare to the CPU implementations for the TNNP model 142

- Figure 4.10 Power consumption of the HAM, CPU and GPU implementations for the Beeler-Reuter model 143

- Figure 4.11 Power consumption of the HAM and CPU implementations for the TNNP model 145

## LIST OF TABLES

| Table 1.1 | CellML model metrics 8                                      |

|-----------|-------------------------------------------------------------|

| Table 1.2 | IEEE-754 special case numbers 21                            |

| Table 1.3 | IEEE-754 single and double precision formats 22             |

| Table 2.1 | Number of equations and floating point operations in        |

|           | the Hodgkin-Huxley model components 36                      |

| Table 2.2 | Synthesis results of the floating point operations for Al-  |

|           | tera EP4SGX230 device 48                                    |

| Table 2.3 | Synthesis results of the Hodgkin-Huxley CellML hard-        |

|           | ware model 48                                               |

| Table 2.4 | Synthesis results of the complete hardware system for       |

|           | Altera EP4SGX230 device 49                                  |

| Table 3.1 | FloPoCo resource use and performance for Stratix IV         |

|           | device 62                                                   |

| Table 3.2 | Metrics of the considered biomedical models 90              |

| Table 3.3 | Stratix IV EP4SGX530KH40C2 device specifications 90         |

| Table 3.4 | Power requirements for the three testing platforms 101      |

| Table 4.1 | Resource capability for selected devices 118                |

| Table 4.2 | Altera single precision Floating Point Megafunctions re-    |

|           | source usage and frequency estimation for Stratix IV De-    |

|           | vices 120                                                   |

| Table 4.3 | Resource usage and frequency estimation of FloPoCo          |

|           | generated single precision floating point cores for Stratix |

|           | IV Devices 121                                              |

| Table 4.4  | Resources percentage usage of the three variations of    |

|------------|----------------------------------------------------------|

|            | floating point multiplication 122                        |

| Table 4.5  | Schemes for reducing PT used in the greedy algorithm 125 |

| Table 4.6  | Evaluation results for the resource balancing example    |

|            | for a different numbers of multipliers 127               |

| Table 4.7  | Operations and I/O of Beeler-Reuter models show in-      |

|            | creasing linearly with the number of pipelines 133       |

| Table 4.8  | Operations and I/O of an optimised TNNP model against    |

|            | the original model 134                                   |

| Table 4.9  | Estimated resource consumption of TNNP HAM before        |

|            | and after resource allocation optimisation 137           |

| Table 4.10 | Predicted clock frequencies for the HAMs of the Beeler-  |

|            | Reuter model 138                                         |

| Table 4.11 | Power requirement for the Beeler-Reuter model on the     |

|            | three testing platforms 143                              |

| Table 4.12 | Power requirement for the TNNP model on the two test-    |

|            | ing platforms 144                                        |

|            |                                                          |

#### **Co-Authorship Form**

Graduate Centre ClockTower - East Wing 22 Princes Street, Auckland Phone: +64 9 373 7599 ext 81321 Fax: +64 9 373 7610 Email: postgraduate@auckland.ac.nz www.postgrad.auckland.ac.nz

This form is to accompany the submission of any PhD that contains research reported in published or unpublished co-authored work. Please include one copy of this form for each co-authored work. Completed forms should be included in all copies of your thesis submitted for examination and library deposit (including digital deposit), following your thesis Acknowledgements.

Please indicate the chapter/section/pages of this thesis that are extracted from a co-authored work and give the title and publication details or details of submission of the co-authored work.

Chapter 2 of this thesis is published as a conference paper in International Conference on Field Programmable Technology, FPT'13 as:

Hardware acceleration of biomedical models with OpenCMISS and CellML, DOI: 10.1109/FPT.2013.6718390

| Nature of contribution by PhD candidate | The concepts, ideas and strategies of hardware acceleration of biomedical models, design, development and evaluation of the hardware accelerator and manuscript writing. |  |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Extent of contribution                  | >70%                                                                                                                                                                     |  |

by PhD candidate (%) **CO-AUTHORS**

| Name          | Nature of Contribution                                                                                            |

|---------------|-------------------------------------------------------------------------------------------------------------------|

| Chris Bradley | Academic advisor on biomedical acceleration, co-supervision of the research and manuscript revision.              |

| Oliver Sinnen | The concepts, ideas and strategies of hardware acceleration, supervision of the research and manuscript revision. |

|               |                                                                                                                   |

|               |                                                                                                                   |

|               |                                                                                                                   |

#### **Certification by Co-Authors**

The undersigned hereby certify that:

- the above statement correctly reflects the nature and extent of the PhD candidate's contribution to this .... work, and the nature of the contribution of each of the co-authors; and

- in cases where the PhD candidate was the lead author of the work that the candidate wrote the text. \*\*

| Name          | Signature | Date       |

|---------------|-----------|------------|

| Chris Bradley | thatpadle | 31/03/2015 |

| Oliver Sinnen | Our &     | 31/03/2015 |

|               |           | Click here |

Last updated: 25 March 2013

## **Co-Authorship Form**

Graduate Centre ClockTower – East Wing 22 Princes Street, Auckland Phone: +64 9 373 7599 ext 81321 Fax: +64 9 373 7610 Email: postgraduate@auckland.ac.nz www.postgrad.auckland.ac.nz

This form is to accompany the submission of any PhD that contains research reported in published or unpublished co-authored work. **Please include one copy of this form for each co-authored work**. Completed forms should be included in all copies of your thesis submitted for examination and library deposit (including digital deposit), following your thesis Acknowledgements.

Please indicate the chapter/section/pages of this thesis that are extracted from a co-authored work and give the title and publication details or details of submission of the co-authored work.

Chapter 3 of this thesis is submitted for publication as a research article in ACM Transactions on Reconfigurable Technology and Systems (currently under review) as:

#### ODoST: Automatic Hardware Acceleration for Biomedical Model Integration

>70%

Nature of contribution by PhD candidate

The concepts, ideas, algorithms and strategies of hardware acceleration of biomedical models and domain-specific high-level synthesis, design and development of ODoST, evaluation of the ODoST generated hardware accelerator modules and manuscript writing.

Extent of contribution by PhD candidate (%)

**CO-AUTHORS**

| Name          | Nature of Contribution                                                                                                                                         |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chris Bradley | Academic advisor on biomedical acceleration, co-supervision of the research and manuscript revision.                                                           |

| Oliver Sinnen | The concepts, ideas and strategies of hardware acceleration and domain-specific high-<br>level synthesis, supervision of the research and manuscript revision. |

|               |                                                                                                                                                                |

|               |                                                                                                                                                                |

|               |                                                                                                                                                                |

#### **Certification by Co-Authors**

The undersigned hereby certify that:

- the above statement correctly reflects the nature and extent of the PhD candidate's contribution to this work, and the nature of the contribution of each of the co-authors; and

- in cases where the PhD candidate was the lead author of the work that the candidate wrote the text.

| Name          | Signature     | Date       |

|---------------|---------------|------------|

| Chris Bradley | CHINA AGOLLON | 31/03/2015 |

| Oliver Sinnen | Om Et         | 31/03/2015 |

|               |               | Click here |

|               |               | Click here |

|               |               | Click here |

|               |               |            |

Last updated: 25 March 2013

#### **Co-Authorship Form**

Graduate Centre ClockTower – East Wing 22 Princes Street, Auckland Phone: +64 9 373 7599 ext 81321 Fax: +64 9 373 7610 Email: postgraduate@auckland.ac.nz www.postgrad.auckland.ac.nz

This form is to accompany the submission of any PhD that contains research reported in published or unpublished co-authored work. **Please include one copy of this form for each co-authored work**. Completed forms should be included in all copies of your thesis submitted for examination and library deposit (including digital deposit), following your thesis Acknowledgements.

Please indicate the chapter/section/pages of this thesis that are extracted from a co-authored work and give the title and publication details or details of submission of the co-authored work.

Chapter 4 of this thesis is submitted for publication as a research article in Concurrency and Computation: Practice and Experience (currently under review) as:

Performance Optimisation Strategies for Automatically Generated FPGA Accelerators for Biomedical Models

Nature of contribution by PhD candidate

The concepts, ideas and strategies of hardware acceelration of biomedical models and hardware optimisations, design, development and evaluation of the optimisation strategies and manuscript writing.

Extent of contribution by PhD candidate (%)

>70%

#### **CO-AUTHORS**

| Name             | Nature of Contribution                                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Julian Oppermann | Implementation of the source-to-source optimiser.                                                                                  |

| Chris Bradley    | Academic advisor on biomedical acceleration, co-supervision of the research and manuscript revision.                               |

| Oliver Sinnen    | The concepts, ideas and strategies of hardware acceleration and optimisation, supervision of the research and manuscript revision. |

|                  |                                                                                                                                    |

|                  |                                                                                                                                    |

#### **Certification by Co-Authors**

The undersigned hereby certify that:

- the above statement correctly reflects the nature and extent of the PhD candidate's contribution to this work, and the nature of the contribution of each of the co-authors; and

- in cases where the PhD candidate was the lead author of the work that the candidate wrote the text.

| Name             | Signature    | Date       |

|------------------|--------------|------------|

| Julian Oppermann | Julian Opper | 29/03/2015 |

| Chris Bradley    | CHARLadley   | 31/03/2015 |

| Oliver Sinnen    | Ofur St      | 31/03/2015 |

|                  |              | Click here |

|                  |              | Click here |

|                  |              |            |

Last updated: 25 March 2013

# 1 INTRODUCTION

The traditional approach in high performance computing (HPC) is to build parallel systems that consist of a large number of general purpose processors (GPPs). However, such systems usually involve high financial cost and energy consumption. Systems with a small number of processors can normally achieve a near-linear speedup. However for systems with a large number of processors, the speedup can flatten out into a constant value [48]. Power and cooling demands can also restrict the number of processors that are affordable [18, 44]. These limitations push HPC engineers to look for other computing technologies such as dedicated computation hardware acceleration for special application areas like bioengineering and scientific computing. A more flexible approach is to use reconfigurable hardware based on Field Programmable Gate Arrays (FPGAs), which can improve performance and reduce power consumption in HPC applications. FPGAs are highly configurable devices with logic blocks and interconnects. The logic blocks are programmable and can incorporate parallelism into arbitrary digital circuits such as being arranged into pipelines or replicated for task and data parallelism.

#### 1.1 BIOMEDICAL MODELLING AND SIMULATION

Biomedical models involve sets of mathematical equations that describe a biomedical system of interest. Biomedical simulations often use numerical computations of these equations to simulate dynamic systems and helping researchers understand different physiological functions. Due to the increased complexity of models and accuracy requirements, the number of variables or Degrees-Of-Freedom (DOF) used for modern biomedical models has rapidly increased in recent times. Complex models with fine mesh size and short time steps require a significant amount of computation, which can result in very long run times even with today's fastest CPUs [94]. However, such models often contain a small and fixed portion of code that executes a large number of times using different data. These code portions are ideally suited for hardware acceleration with FPGAs. In this thesis, CellML is used to describe biomedical models and develop hardware acceleration modules (HAMs) based on FPGAs for these models. These HAMs are to be used with the biomedical modelling environment, OpenCMISS [24], in order to simulate multi-scale physiological systems.

#### 1.1.1 Biomedical Modelling with CellML

CellML [34] is an XML based model description language for specifying and exchanging biophysically based systems of Ordinary Differential Equations (ODEs) and Differential Algebraic Equations (DAEs). It takes advantage of the extensibility of the XML language and incorporates other XML-based standards, including MathML [17], XLink [41], and Resource Description Framework (RDF) [25].

#### 1.1.1.1 CellML Model Structure

CellML contains its own defined elements for describing the model structure. Other information is incorporated into the model document using existing standards. For example, MathML is used to encode the mathematics of the model, XLink is used to establish the connection between the original model and the importing model, and background information, or metadata, is included via RDF [34].

Figure 1.1: CellML model structure.

The structure of a CellML model is illustrated in Figure 1.1. A CellML model is represented by a set of interconnected components. A component is the functional unit of a CellML model that contains variables and mathematical equations. A variable is associated with a unit that is defined in the units entity. The mathematical equations are expressed using MathML that is embedded within the CellML framework. Biochemical reactions between substrates are organized into components that represent the reactants and products of the reactions, the reactions themselves, and the enzymes or inhibitors that influence the reaction rates. The properties of a reaction—such as its reactants, products, enzymes, and inhibitors—and the reaction kinetics are all captured by the variables and the mathematical equations of a component [34]. Connections are used to link two components by mapping the variables inside one component with variables inside the other component. Grouping adds structure to a model by defining named relationships between components. Importing provides authors with the ability to reuse parts of other models by importing components or units from other models. RDF metadata is included in CellML to provide structured descriptive information such as the model author, literature reference, copyright, etc., and to facilitate searches of collections of models and model components from the CellML model repository [64].

#### 1.1.1.2 Mathematical Representation

Mathematically, a CellML model describes a vector system, **F**, of DAEs in the form of:

$$\mathbf{F}(t, \mathbf{x}, \mathbf{x}', \mathbf{a}, \mathbf{b}) = \mathbf{0} \tag{1.1}$$

where *t* is the independent variable, **x** is a vector of state variables,  $\mathbf{x}'$  is a vector of the derivatives of state variables with respect to the independent variable, **a** is a vector of independent parameters/constants, and **b** is an optional vector of intermediate/algebraic "output" variables from the model. All the variables are defined in the *variable* entity under each component.

#### 1.1.1.3 Example CellML Models

Four CellML model examples are described here. The four models are selected from the CellML model repository<sup>1</sup> with each model having a different level of complexity. The mathematics and C-code representation for each example model are shown in Appendix A. Of the four example models, the first two simple models, the Hodgkin-Huxley model and the Beeler-Reuter model are used as the case studies for model investigation and hardware design. These two models together with two more complex models, the Hilemann-Noble and the TNNP model are also used as the test cases for the evaluation of the research work throughout the thesis.

HODGKIN-HUXLEY MODEL The Hodgkin-Huxley Model was developed by Hodgkin and Huxley [53] in 1952. The model describes the flow of electric current through the surface membrane of the giant nerve axon of a squid.

<sup>1</sup> http://www.cellml.org/model

Figure 1.2: A schematic cell diagram describing the current flows across the cell membrane that are captured in the Hodgkin Huxley model [52].

The schematic diagram of the model is shown in Figure 1.2. The model describes the flow of ions across a cell membrane (the ionic current). The ionic current is divided into components carried by sodium and potassium ions ( $I_{Na}$ and  $I_K$ ), and a small 'leakage current' ( $I_L$ ) carried by chloride and other ions. Each component of the ionic current is determined by the transmembrane potential (a driving force which may conveniently be measured as an electrical potential difference between the inside and outside of the cell) and a permeability coefficient which has the dimension of conductance. Thus the sodium current ( $I_{Na}$ ) is equal to the sodium conductance ( $g_{Na}$ ) multiplied by the difference between the membrane potential (V) and the equilibrium potential for the sodium ion ( $E_{Na}$ ). Similar equations apply to  $I_K$  and  $I_L$ . This model has been used as the basis for almost all other ionic current models of excitable tissues, including cardiac atrial and ventricular muscle. The Hodgkin-Huxley model is the simplest of the four models.

BEELER-REUTER MODEL The Beeler-Reuter Model was developed by Beeler and Reuter [21] in 1977. The model describes the membrane action potentials of mammalian ventricular myocardial fibres. The total ionic flux is divided into four discrete, individual ionic currents as shown in Figure 1.3. The main

Figure 1.3: A schematic diagram describing the current flows across the cell membrane that are captured in the Beeler-Reuter model [20].

additional feature of the Beeler-Reuter ionic current model compared to the Hodgkin-Huxley model is its inclusion of a representation of the intracellular calcium ion concentration. The model incorporates two voltage-dependent and time-dependent inward currents: the excitatory inward sodium current,  $I_{Na}$ , and a secondary, or slow inward, current,  $I_s$ , which is primarily carried by calcium ions. A time-independent outward potassium current,  $I_{K1}$ , exhibiting inward-going rectification, and a voltage-dependent and time-dependent outward current,  $I_{x1}$ , primarily carried by potassium ions, are further elements of the model.

HILEMANN-NOBLE MODEL The Hilemann-Noble Model was developed by Hilemann and Noble [51] in 1987. The model describes the interactions of electrogenic sodium-calcium exchange, calcium channel and sarcoplasmic reticulum in the mammalian heart which occur when the extracellular calcium transients are stimulated with tetramethylmurexide in the rabbit atrium. The schematic diagram of the model is shown in Figure 1.4.

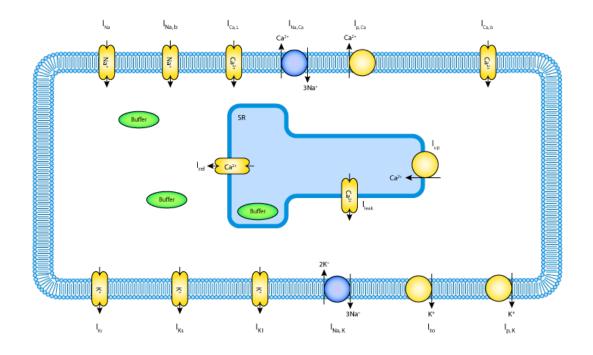

Figure 1.4: A schematic diagram describing the current flows across the cell membrane that are captured in the Hilemann-Noble model [50].

TUSSCHER-NOBLE-NOBLE-PANFILOV MODEL The Tusscher-Noble-Noble-Panfilov (TNNP) model for human ventricular tissue was developed by Ten Tusscher et al. [96]. This model describes the action potential of human ventricular cells including a high level of electrophysiological detail, and can be applied in large-scale spatial simulations for the study of reentrant arrhythmias. The model is based on the experimental data on most of the major ionic currents: the fast sodium, L-type calcium, transient outward, rapid and slow delayed rectifier, and inward rectifier currents, and it also includes a basic calcium dynamics, allowing for the realistic modeling of calcium transients, calcium current inactivation, and the contraction staircase. A schematic diagram of the model is shown in Figure 1.5.

MODEL METRICS The model metrics with the number of components, equations, parameters/variables and operations for the four example models from the CellML model repository are presented in Table 1.1. These metrics are used in model analysis and evaluation in later chapters.

| Operation: $log(x)$ | Operation: $x^y$ | Operation: $e^x$ | Operation: ÷ | Operation: × | Operation: – | Operation: + | Algebraic variables | Parameters/rate constants | State variables | Equations | Components | Model          |

|---------------------|------------------|------------------|--------------|--------------|--------------|--------------|---------------------|---------------------------|-----------------|-----------|------------|----------------|

| ı                   | 2                | 6                | 10           | 17           | 11           | 9            | 10                  | 8                         | 4               | 14        | 8          | Hodgkin-Huxley |

| 1                   | 1                | 25               | 28           | 52           | 34           | 41           | 18                  | 12                        | 8               | 30        | 13         | Beeler-Reuter  |

| 4                   | 7                | 21               | 52           | 134          | 72           | 47           | 40                  | 55                        | 15              | 45        | 23         | Hilemann-Noble |

| 4                   | 26               | 52               | 129          | 139          | 64           | 112          | 67                  | 46                        | 17              | 84        | 30         | TNNP           |

Table 1.1: CellML model metrics.

Figure 1.5: A schematic diagram describing the ion movement across the cell surface membrane and the sarcoplasmic reticulum, which are described by the Ten Tusscher et al. 2004 mathematical model of the human ventricular myocyte [95].

#### 1.1.1.4 CellML API

For CellML models to be useful, tools which can process them correctly are needed. Therefore, an Application Programming Interface (API), and a good implementation of that API, are required for supporting CellML. The developed CellML API [67] allows for the information in CellML models to be retrieved and/or modified. It also contains a series of optional API extension, for tasks such as simplifying the handling of connections between variables, dealing with physical units, validating models, and translating models into different procedural languages e.g., the C language.

#### 1.1.2 Biomedical Simulation with OpenCMISS

OpenCMISS [24] is a general modelling environment with particular features for biomedical simulations. It consists of two main parts: a graphical and field manipulation library, OpenCMISS-Zinc, and a parallel computational library for solving partial differential and other equations using a variety of numerical methods, OpenCMISS-Iron. OpenCMISS-Iron is a re-engineering of the CMISS (Continuum Mechanics, Image analysis, Signal processing, and System identification) computational code that has been developed and used for over 30 years.

#### 1.1.2.1 OpenCMISS Fields

In OpenCMISS fields are the central mechanism that describe and store information of physical problems. OpenCMISS fields are in hierarchical structure, with each field containing a set of field variables and each field variable containing a set of field variable components. A field is defined over a domain which is, conceptually, an entire computational mesh representing the model of interest. However, when executing in parallel, the mesh is decomposed into a number of computational domains depending on the number of computational nodes. OpenCMISS allows each field variable component to have different forms of DOFs structures including:

- constant structure (one DOF for the component);

- element structure (one or more DOFs for each element);

- node structure (one or more DOFs for each node);

- Gauss point structure (one or more DOFs for each Gauss or integration point);

- data point structure (one or more DOFs for each data point).

OpenCMISS collects all the DOFs from all the field variable components and stores them as a single distributed vector. The DOFs stored in the distributed vector include those from the computational domain and also a layer of "ghosted" DOFs (local copies of the value of DOFs in a neighbouring domain). To ensure consistency of data OpenCMISS handles the updates between computational nodes if a computational node changes the value of a DOF, which is ghosted on a neighbouring computational node [24].

#### 1.1.2.2 Use of CellML Models in OpenCMISS

In biomedical simulations using OpenCMISS, CellML allows for the "plug and play" of mathematical models and model configurations. OpenCMISS uses the CellML API [67] to interact with CellML models. In OpenCMISS-Iron, a higher level CellML interface is defined with the use of the CellML API, and this interface is used by the OpenCMISS core library [71].

Since models in OpenCMISS are defined using a collection of fields, CellML models are integrated into OpenCMISS through these fields. The CellML variables are mapped with OpenCMISS models field variable components. Depending on the direction of dataflow, there are two types of maps. A "known" CellML variable represents a map link from OpenCMISS to CellML (input variable to the CellML model) and a "wanted" CellML variable represents a map link from CellML to OpenCMISS (output variable from the CellML model). A map is specified by identifying a particular OpenCMISS field variable component and the name of a CellML variable in the CellML model. OpenCMISS looks at each DOF in each field variable component that has been mapped and determines the DOF location (i.e., the position of the node) for each instances of a CellML model [71].

#### 1.2 HARDWARE ACCELERATION WITH RECONFIGURABLE HARDWARE

Hardware acceleration is the use of computer hardware to perform particular functions faster than if they are executed on a more general-purpose CPU. Normally, processors execute instructions one by one in sequence. The performance of sequential processors can be improved by various techniques and including hardware acceleration. Programming at the hardware level enables optimal parallel processing by removing the architectural constraints of a traditional CPU and its operating system layers [87].

Hardware accelerators are designed for computationally intensive software code, such as those with repetitive mathematical calculations e.g., integrations.

Examples of devices that are commonly used as hardware accelerators are Graphics Processing Units (GPUs), FPGAs and Application Specific Integrated Circuits (ASICs). Compared to GPPs, there is a trade-off between flexibility and efficiency, with hardware accelerators. Implementing an application in hardware increases efficiency but decreases flexibility.

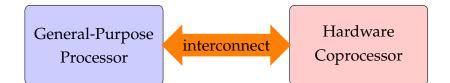

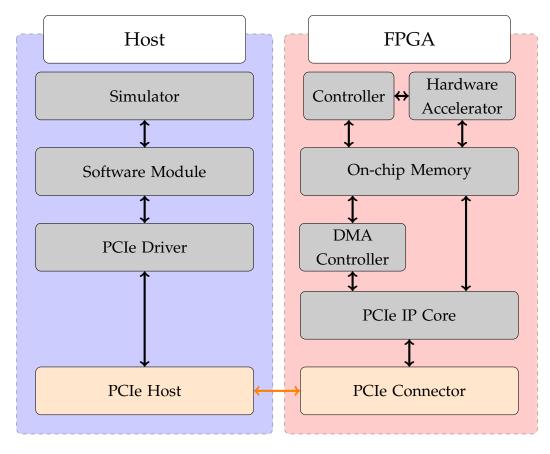

#### 1.2.1 Hybrid Acceleration System

Hardware accelerators like FPGAs yield fast performance. However, large applications implemented on a GPP may be more area efficient and require less designer's effort, albeit at the expense of slower performance. A hybrid hardware acceleration system (or hardware/software co-design system) is a system combining a GPP and one or more custom coprocessors through an interconnect. The system enables the critical computational region of a given application to be put into a coprocessor and to keep the rest in the GPP to achieve an implementation that best satisfies requirements of performance, area and designer effort. Figure 1.6 illustrates a typical hybrid hardware acceleration system.

Figure 1.6: Typical hybrid hardware acceleration system.

#### 1.2.2 Field Programmable Gate Arrays

Computation in the computer and electronic world is usually performed in two ways: via hardware and via software. Computer hardware, like ASICs, provides high performance for critical tasks but it is permanently configured to the specified application. On the other hand, computer software provides flexibility for performing different tasks/applications, but is orders of magnitude worse than ASIC implementations in terms of performance and power usage. FPGAs fill the gap between the two and blend the benefits of computation via both hardware and software. FPGAs implement circuits just like ASICs, providing huge power and performance benefits over software, and yet can be reprogrammed in order to implement a wide range of tasks.

Like other computational hardware, FPGAs are essentially integrated circuits that are able to implement computations spatially and simultaneously so that millions of operations can be executed by resources distributed on a silicon chip. Furthermore, since the dynamic power consumed by a FPGA depends on clock frequency, the overall power consumption is lower than either a CPU or GPU as the FPGA's clock frequency is typically hundreds of MHz compared to a CPU's or GPU's GHz.

#### 1.2.2.1 Architecture

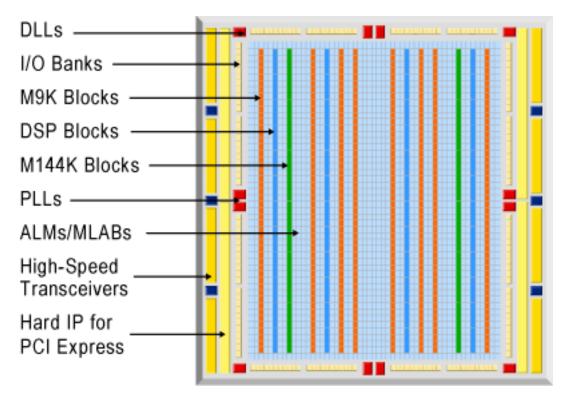

In general, a FPGA contains a matrix of logic blocks, with interconnects between these logic blocks. The logic blocks may be named differently depending on vendors. Altera<sup>2</sup> and Xilinx<sup>3</sup> are the two dominating manufacturers of FPGAs. In Altera FPGAs, these logic blocks are called Logic Array Blocks (LABs) and for Xilinx FPGAs, they are named as Configurable Logic Blocks (CLBs). A highlevel overview of an Altera Stratix IV is shown in Figure 1.7. This FPGA serves as the basis for experimental work conducted in this thesis.

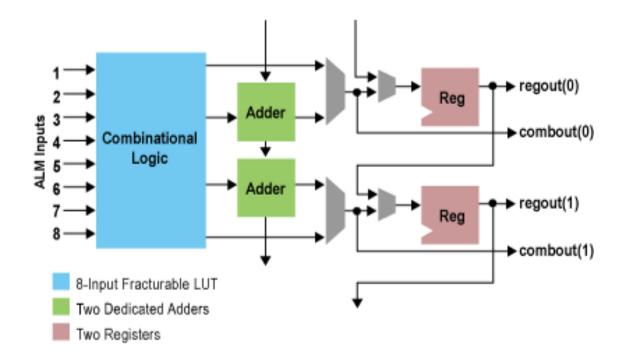

In Stratix IV FPGAs, each LAB consists of ten Adaptive Logic Modules (ALMs). An ALM is the basic building block of Stratix IV FPGAs and each ALM contains an 8-input fracturable Look-Up Table (LUT), two embedded adders and two registers as shown in Figure 1.8. The 8-input fracturable LUT can be used to implement any logic function with up to six inputs and certain functions with seven inputs. The two dedicated full adders are capable of two two-bit or two three-bit additions. Two programmable registers are directly embedded in the ALM for an optimal logic-to-register ratio. Signals are transferred between ALMs within the same LAB through local interconnects and between neighbouring LABs through direct link interconnects [11].

<sup>2</sup> http://www.altera.com

<sup>3</sup> http://www.xilinx.com

Figure 1.7: Stratix IV FPGA architecture [12].

Figure 1.8: Stratix IV FPGA ALM [11].

Stratix IV FPGAs provide two to seven columns of Digital Signal Processing (DSP) blocks that can be used to implement floating point arithmetic functions more efficiently than ALMs alone. The DSP blocks can provide functions like multiplication, multiply-add, multiple-accumulate (MAC) and dynamic shift functions. Biomedical models usually require a large number of mathematical computations which can be efficiently performed by DSPs.

Two types of storage resources, registers and memory blocks, are embedded in FPGAs. Compared to registers, resources for on-chip memory are, in general, abundant. Stratix IV FPGAs offer three different memory types, namely Memory Logic Array Block (MLAB), M9K and M144K, each having differing memory capacities and bandwidths. An increase in memory capacity normally results in a decrease in bandwidth. MLABs have the highest memory bandwidth but their size is limited to only 640 bits. They are useful for shift registers, small First-In First-Out (FIFO) buffers and filter delay lines. M9K memory blocks have 9 kb and are used for general-purpose memory, packet headers or cell buffers. M144K memory blocks have 144 kb of memory and are used for larger general-purpose memory, packet headers or cell buffers.

All the resource elements discussed above are embedded within a switched routing fabric including many short-distance links and a few fast global links which interconnect the elements within the device. This is often referred as *island-style* architecture and is common in modern FPGAs.

## 1.2.2.2 Hardware Description Language

A Hardware Description Language (HDL), such as VHSIC Hardware Description Language (VHDL) or Verilog, can be used to program the structure, design and operation of digital logic circuits. A HDL enables a precise, formal description of an electronic circuit that allows for the automated analysis, simulation, and simulated testing of an electronic circuit. It also allows for the compilation of a HDL program into a lower level specification of physical electronic components, such as the set of masks used to create an integrated circuit [15].

Similar to other programming languages, a HDL is a textual description consisting of expressions, statements and control structures. One important differ-

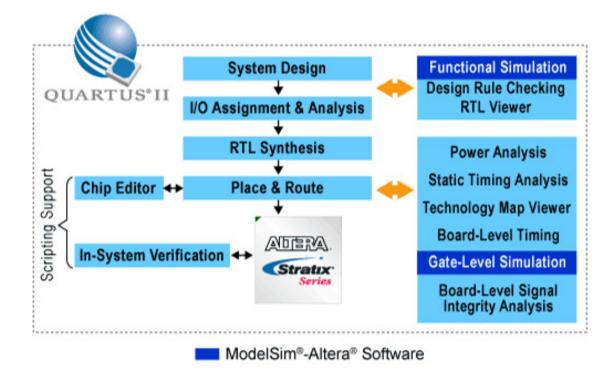

Figure 1.9: Altera's FPGA application design flow [9].

ence between most programming languages and HDLs is that HDLs explicitly include the notion of time, which is the primary attribute in an integrated circuit.

# 1.2.2.3 Design Flow

The FPGA design flow for a typical application including system design, I/O assignment and analysis, Register Transfer Level (RTL) synthesis, place-and-route process, programming and simulations at multiple stages throughout the design process, is shown in Figure 1.9.

After an application has been developed in a HDL, the synthesis engine compiles the design from the HDL sources to an architecture-specific netlist. The design components will then be put through an automated place-androute procedure to generate a pinout, which will be used to interface with components outside of the FPGA. The final step is the generation of a bitstream programming file in a format that can be downloaded to the target device. The bitstream file is programmed to the FPGA though a connection cable, such as USB-JTAG.

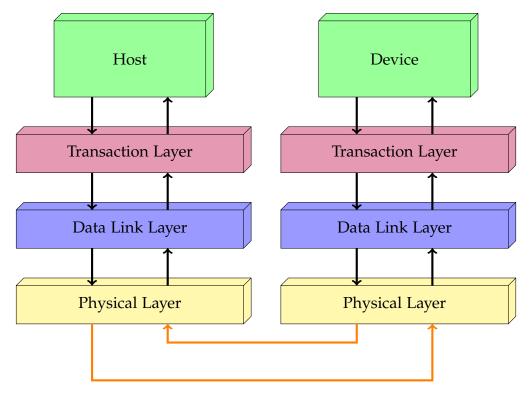

Figure 1.10: PCI Express layered architecture.

## 1.2.3 PCI Express

PCIe (Peripheral Component Interconnect Express) is a scalable, chip-to-chip, high-speed serial expansion bus protocol used in computing and communication. PCIe is based on point-to-point topology, with separate serial links connecting every device to the host machine [14].

## 1.2.3.1 Architecture

The PCI Express architecture is specified in layers as shown in Figure 1.10. The host normally uses a software model or driver to generate read and write requests that are transported through the transaction layer, the data link layer and finally the physical layer to the I/O devices using a packet-based, split-transaction protocol.

TRANSACTION LAYER The transaction layer receives read and write requests from a software model or driver and creates request packets for transmission to the data link layer. All requests are implemented as split transactions and some of the request packets also require a response packet. The transaction layer receives response packets from the link layer and matches these with the original software requests. Each packet has a unique identifier that enables response packets to be directed to the correct originator. The packet format offers 32-bit memory addressing and extended 64-bit memory addressing.

DATA LINK LAYER The primary role of a data link layer is to ensure reliable delivery of the packet across the PCI Express link(s). The data link layer is responsible for data integrity and adds a sequence number and a Cyclic Redundancy Codes (CRC) to packets initiated by the transaction layer.

PHYSICAL LAYER The physical layer contains the fundamental PCI Express links with a dual simplex channel (refered to as a lane), implemented as a transmit pair and a receive pair. A data clock is embedded using the 8b/10b encoding scheme to achieve very high data rates with an initial bandwidth of 2.5 Gb/s/direction (Generation 1). The rates are doubled in each successor generation. The physical layer transports packets between the data link layers of two PCI Express agents. The physical layer provides x1, x2, x4, x8, x12, x16, and x32 lane widths, which conceptually splits the incoming data packets among these lanes. Each byte is transmitted with 8b/10b encoding across the lane(s). This data disassembly and reassembly is transparent to other layers. During initialization, each PCI Express link is set up following a negotiation of lane widths and frequency of operation by the two agents at each end of the link.

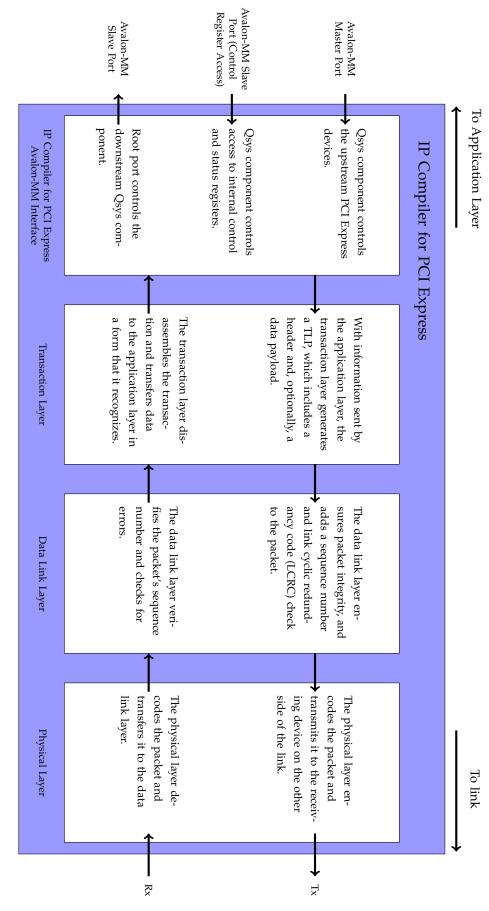

# 1.2.3.2 PCI Express IP Core

Interfacing a FPGA to the PCIe bus is not a simple task. Fortunately, there are numerous PCIe cores available provided by FPGA vendors and third parties. In this thesis, the Intellectual Property (IP) Compiler for PCI Express, available in the Qsys design flow provided by Altera, is used. Figure 1.11 shows the block diagram of the IP core with an Avalon Memory Mapped Interface (Avalon-MM) [7].

Custom variations, generated by the IP Compiler for PCI Express in the Qsys design, provides a bridge interface between the PCI Express transaction layer and other components across the system interconnect fabric through an Avalon MM interface. The hard IP implementation of the PHY (Physical), MAC (Media Access Control) and data link layers of the Open Systems Interconnection (OSI) model communicates with a soft IP implementation of the transaction layer optimized for the Avalon-MM protocol. The Avalon-MM interface helps the PCIe IP core to remove some of the complexities associated with the PCIe protocol and to abstract the addressing, transfer size and packet rules of PCIe [6].

## 1.2.4 Floating Point Unit

Floating-point functionality is used to achieve a high degree of numeric precision and dynamic range that most high performance applications (e.g., radar, sonar, biomedical simulation and financial modelling) require. As many of these applications use FPGAs there is a demand for floating-point capabilities. There are a good number of existing floating point cores provided either by the vendors of FPGAs, or independently developed third party floating point platforms. These cores typically exploit the freedom of a FPGA by allowing for the customisation of variable widths of exponent and mantissa to meet designers specifications. They also offer IEEE-754 standard single and double precision cores.

## 1.2.4.1 IEEE-754 Standard for Floating Point Format

IEEE-754 standard floating point is the most common representation for real numbers. It is used in computer systems ranging from large servers to small embedded systems and is supported by all major operating systems and programming languages. In this thesis, the floating point numbers in our hardware accelerator follow the IEEE-754 standard. This allows the accelerator to produce accurate results which are compatible with pure software solutions.

Figure 1.11: IP compiler for PCI express with Avalon-MM interface [6].

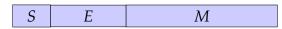

Figure 1.12: IEEE-754 floating point format (*S* represents a sign bit, *E* represents an exponent field, and *M* is the mantissa field).

| Numbers               | Sign       | Exponent | Mantissa |  |

|-----------------------|------------|----------|----------|--|

| 0                     | Don't care | All o's  | All o's  |  |

| Positive Denormalised | 0          | All o's  | Non-zero |  |

| Negative Denormalised | 1          | All o's  | Non-zero |  |

| Positive Infinity     | 0          | All 1's  | All o's  |  |

| Negative Infinity     | 1          | All 1's  | All o's  |  |

| Not-a-Number (NaN)    | Don't care | All 1's  | Non-zero |  |

Table 1.2: IEEE-754 special case numbers.

The IEEE-754 floating point formats have binary patterns of the form shown in Figure 1.12. A normal floating point number can be represented by the following equation where b represents the exponent bias and m represents the number of bits in the mantissa field:

$$value = (-1)^{S} (1 + \sum_{i=1}^{m} M_{m-i} 2^{-i}) \times 2^{(E-b)}$$

In addition to the normal numbers, the IEEE-754 standard also defines some special case numbers as shown in Table 1.2.

The IEEE 754-1985 standard provides definitions for four levels of precision, of which the two most commonly used are single precision and double precision. Table 1.3 describes the binary patterns, range and accuracy of these two precisions.

## 1.2.4.2 Altera Floating Point Megafunctions

Altera provides IEEE 754-compliant floating-point megafunctions for its device family. The key floating point megafunctions Altera supports include addition and subtraction, multiplication, division, square root, compare, logarithm, exponential function, inverse, etc. All the floating point (FP) cores are pipelined. The performance of a floating point computation is influenced by the fre-

|                     | Width                                                   | Sign Bit               | Exponent Bits             | Mantissa Bits             | Bias |  |

|---------------------|---------------------------------------------------------|------------------------|---------------------------|---------------------------|------|--|

| Single<br>Precision | 32                                                      | 31                     | 3023                      | 220                       | 127  |  |

|                     |                                                         | Rang                   | ge                        | Precision                 |      |  |

|                     | ±1.18                                                   | $3 \times 10^{-38} tc$ | $p \pm 3.4 	imes 10^{38}$ | approx. 7 decimal digits  |      |  |

|                     | Width                                                   | Sign Bit               | Exponent Bits             | Mantissa Bits             | Bias |  |

| Double              | e 64 63 6252                                            |                        | 510                       | 1023                      |      |  |

| Precision           | Range                                                   |                        |                           | Precision                 |      |  |

|                     | $\pm 2.23 	imes 10^{-308}$ to $\pm 1.80 	imes 10^{308}$ |                        |                           | approx. 15 decimal digits |      |  |

Table 1.3: IEEE-754 single and double precision formats.

quency at which the operators run at and the pipeline latency of the operator hardware. When designing for maximum FP performance in a FPGA, the total number of operators that can be placed in a FPGA is vital. As such, the Altera floating-point megafunctions can be customised in many different ways to fine-tune FP performance, power consumption and area usage to meet the application-specific requirements [5]. The configurable features include:

- Single and double-precision selection;

- Single extended configurable precision;

- Operator latency versus area tradeoff;

- Reduced functionality;

- Optional denormalized number support;

- Reduced rounding accuracy;

- Optional indefinite support;

- Support for dedicated multiplier circuitry (multiplier only);

- Optional add or subtract-only mode (adder or subtracter only).

# 1.2.4.3 FloPoCo

FloPoCo [37] is an open source generator of arithmetic cores for FPGAs. In contrast to IEEE floating point representations, FloPoCo has a special floating point format which has an additional two-bit prefix. The two bits are only used

to signal special case numbers, namely 00 for zero, 01 for normal numbers, 10 for infinities, and 11 for *NaN*. In IEEE-754 format, these exception signals are handled by the exponent and mantissa as shown in Table 1.2. The advantage of the FloPoCo format is that it saves quite a lot of decoding/encoding logic. The main drawback of this format is when results have to be stored in memory as they require two additional bits. However, as the FPGA embedded memory can accommodate 36-bit data, the addition of two bits to a 32-bit IEEE-754 format is harmless as long as data resides within the FPGA.

FloPoCo supports floating point operations including addition and subtraction, multiplication, division, square root, logarithm, exponential function, power, etc. FloPoCo is used as a command-line tool to create arithmetic cores. A VHDL based floating point core can be created with the numbers of bits in the exponent and mantissa specified by the user. For example, an execution of

flopoco FPDiv 8 23

will produce a file *flopoco.vhdl* containing the floating point division core with single precision format.

In addition, FloPoCo also provides customisation options that allows users to manipulate resources, frequency and latency to suit their applications. For example:

- -target=Stratix4 sets the target device to the Stratix IV family. Having this

option set will target the highest speed grade available for the device

family;

- -pipeline=yes instructs FloPoCo to produce a pipelined core;

- -frequency=300 sets the target frequency (in MHz), this option is used when the -pipeline option is set. FloPoCo will try to pipeline the operators to the target frequency;

- -useHardMult=yes instructs FloPoCo to use hard multipliers or DSP blocks wherever possible;

- -unusedHardMultThreshold=0.3 instructs FloPoCo to use a hard multiplier (or DSP block) if less than 30% of the hard multipliers are unused. The

ratio is between 0 and 1, such that 0 means: any sub-multiplier that does not fully fill a DSP goes to logic; 1 means: any sub-multiplier, even very small ones, will consume a DSP.

A FloPoCo operator can be either combinational or pipelined, which is controlled by the *-pipeline* and *-frequency* options. With the pipelined implementation, registers maybe inserted to reach a target frequency. However, the pipeline built by FloPoCo may depend on the target device and the effort is always tentative [36].

# 1.3 HIGH-LEVEL SYNTHESIS

High-level Synthesis (HLS) is an automated design process that interprets a high-level description of a design and creates digital hardware that implements that design [32]. The synthesis begins with a high-level specification of the problem, for example, high-level languages like C, state diagrams or logic networks. The code is analysed, architecturally constrained, and scheduled to create a Register Transfer Level (RTL) HDL, which is then, in turn, commonly synthesized to the gate level by the use of a conventional logic synthesis tool.

# 1.3.1 Benefit

It is common knowledge that the RTL creation process for hardware implementations is much more time consuming and error prone than an equivalent software development. The main benefit of HLS is to avoid this problem by automating the RTL implementation process and providing an error-free path from an abstract specification to RTL and hence significantly reducing the design and verification efforts.

#### 1.3.2 Design Processes

The HLS process consists of a number of stages. Different HLS tools may vary their design process or order. Some frequently used processing stages are discussed below [66].

LEXICAL PROCESSING HLS synthesis begins with an algorithmic description of the design expressed in a high-level language. Lexical processing parses the high-level language source code and transforms it into an internal representation which is similar to the high-level language compilation.

DESIGN OPTIMIZATION Optimizations that can be performed on the design itself include common subexpression elimination and constant folding. Many of these optimizations are commonly used in high-level language compilers or parallelising compilers.

CONTROL/DATAFLOW ANALYSIS The inputs, outputs, and operations of the design are identified and the data dependencies between them are determined. The result of this process is usually a Control/Dataflow Graph (CDFG) which determines the order of the computation.

LIBRARY PROCESSING The RTL implementation produced by HLS will depend on the capabilities and characteristics of the library of parts available for the specific implementation technology to be used. Library processing reads the available libraries and determines the functional, timing, and area characteristics of the available parts.

**RESOURCE ALLOCATION** Resource allocation establishes a set of functional units that will be adequate for implementation of the design. In many behavioural synthesis systems, an initial resource allocation is performed and subsequently modified during scheduling and/or binding.

SCHEDULING Scheduling introduces parallelism and the concept of time. It transforms the algorithm into an FSM (Finite State Machine) representation. Using the data dependencies of the algorithm and the latencies of the functional units in the library, the operations of the algorithm are assigned to specific clock cycles. There are often many possible schedules. Directives that constrain the result with respect to latency, pipelining, and resource utilization will affect the schedule that is chosen.

FUNCTIONAL UNIT BINDING Binding assigns the operations of the algorithm to specific instances of functional units from the library.

**REGISTER BINDING** In cases where values are produced in one clock cycle and consumed in another, these values must be stored in registers or memory. The register binding process allocates registers as needed and assigns each value to a physical register. Analysis of the lifetime of each data value can identify opportunities to use the same physical register to store different values at different times. This is done to reduce the size of the resulting design.

OUTPUT PROCESSING The datapath and finite state machine resulting from all of the previous steps are written out as RTL source code in the target language. This code can be structured in a number of ways to optimize the downstream logic synthesis process or to enhance the readability of the code.

# 1.4 THESIS MOTIVATION AND CONTRIBUTIONS

## 1.4.1 Motivations

Benefiting from the development of HPC in recent decades, the number of degrees-of-freedom (DOFs) used in biomedical modelling has increased rapidly in response to increased model complexity and increased model accuracy requirements. In order to reduce run times, parallel computing is now becoming increasingly important as individual CPUs reach the physical limits of processor technology. Simulations involving the numerical integration of models (such as using CellML with OpenCMISS to simulate large multi-scale physiology) are generally limited by the available computational hardware and the acceptable duration of simulation. For certain simulations in OpenCMISS, a CellML model needs to be evaluated a very large number of times, resulting in a significant computational time. In order to reduce this time, we can take advantage of the fact that each instance of a CellML model at a particular DOF is completely independent from the CellML models at every other DOF and so it is possible to evaluate the models in parallel. Therefore, special purpose hardware, in particular FPGAs, is very promising for accelerating these kinds of computations and are expected to lead to higher performance at lower cost and less power consumption.

Unfortunately, there are two major problems that have to be overcome. First, developing a FPGA hardware design for a given application is much more complex, time consuming and error prone than programming general purpose processors. Second, integrating the general purpose processors in parallel computing systems with the reconfigurable computing capacity of the FPGAs is not trival. Therefore, despite the benefits that heterogeneous computing has to offer in the area of science and technology, the existing tools that enable development for FPGA-platforms are highly dependent on hardware design expertise, i.e., an excellent understanding of a HDL and fine-grained digital hardware architecture. This impedes the ability of biomedical scientists/engineers to explore acceleration on such platforms, and creates a wide gap between their speciality and the vast computational capacity of FPGAs.

Being able to automatically generate Hardware Accelerator Modules (HAMs) from existing high-level model descriptions, e.g., CellML models, would open up the use of the FPGAs to biomedical scientists/engineers. This vision leads to the key motivations for this thesis:

- To provide a high performance hardware/software co-design framework for biomedical simulations;

- To design and develop a domain specific high-level synthesis process that enables the generation of the above framework in an automated way;

- To demonstrate that domain specific high-level optimisation can deliver competitive performance and lower energy costs;

- To investigate and develop automatic methods and technologies for optimised automatic hardware generation.

# 1.4.2 Contributions

The following major novel and innovative contributions have been made while undertaking the research presented in this thesis:

- Exploration into the current state of the art of biomedical modelling and simulation with hardware acceleration and HLS, identifying areas of improvement and new ways to exploit parallelism;

- Design and development of a parallel floating point pipeline based on

a hardware accelerator module for biomedical models. The presented

module is embedded in a proposed hardware/software co-design framework that can be integrated with biomedical simulators;

- Investigation and design of a domain specific HLS tool for biomedical modelling to automatically create the designed hardware accelerating modules from high-level descriptions of biomedical models. The tool is named ODoST, standing for ODE-based Domain-specific Synthesis Tool, and it allows biomedical scientists/engineers (without hardware design expertise) to perform simulations with the use of HAMs;

- Investigation of **performance optimisation and resource utilisation strategies** for large hardware computing designs. These strategies are used in the HLS processes to create hardware acceleration modules with better performance and resource usage. Furthermore, the framework is general and can be adopted for other applications with floating point computations.

- Extensive experimental evaluation on real hardware of the generated hardware accelerator modules regarding resource usage, scalability, per-

formance and power consumption, including a comparison of performance and power consumption with the corresponding models in CPU and GPU implementations.

## 1.5 THESIS STRUCTURE

This thesis is structured as a compilation of publications. References in the papers have been adjusted to cross-references within this thesis. The work is presented following the outline below.

This chapter describes, in detail, the background of the research. It presents a brief overview of CellML and OpenCMISS. A number of representive CellML models are explained and selected as the base models for the HAM development and evaluation in later chapters. The chapter then presents the concepts, techniques and tools of reconfigurable computing used in the thesis. At the end, a summary of the motivation and contributions of this research is presented.

Chapter 2 presents the initial design and development of the hardware accelerator module with a hardware/software co-design framework. This module is implemented manually, and evaluations are performed to obtain preliminary results of the design. The content of this chapter is published at the Field-Programmable Technology (FPT) Conference [100].

In Chapter 3, a domain-specific high level synthesis tool called ODoST is investigated and designed, mainly based on the accelerator design discussed in Chapter 2. HAMs are generated automatically using ODoST and an in-depth evaluation is performed, including a comparison with pure software and GPU designs. The content of this chapter is submitted as a manuscript and is currently under review for publication in the ACM Transactions on Reconfigurable Technology and Systems.

Chapter 4 proposes several general optimisation strategies, including sourceto-source compiler optimisation, resource balancing and parallel pipelines to further increase the performance of HAMs and to better use the capabilities of the target devices. The proposed strategies have in common that they still can maintain the automatic nature of the overall process of the FPGA implementations. The optimised HAMs are evaluated and compared against CPU and GPU designs as well as non-optimised HAM implementations. This work is submitted for publication as a research article in the Journal of Concurrency and Computation: Practice and Experience.

Finally, Chapter 5 concludes this thesis. The contributions and outcomes of this work are summarised and reconsidered within the context of the motivations, and a number of directions and suggestions for future research are presented.

# 2 HARDWARE ACCELERATOR MODULE

This chapter presents the initial design and development of the hardware accelerator module, along with a hardware/software co-design framework. The contents of this chapter are based on the published paper in Proceedings of the International Conference on Field Programmable Technology, FPT'13 [100].

Contributions in this chapter are: (i) investigation of biomedical models for code portions that are suitable for hardware acceleration, (ii) design of the hardware/software co-design framework purposed for the hardware accelerator, and (iii) development of a manual implementation of a hardware accelerator module based on the co-design framework for the identified computation kernel.

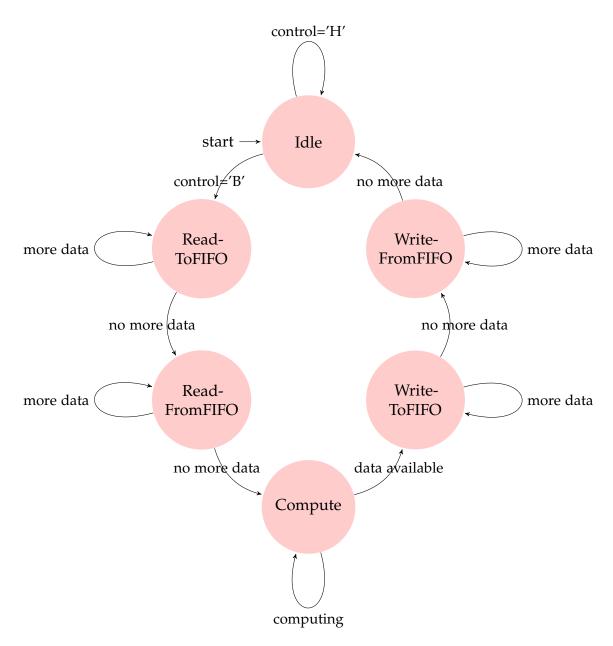

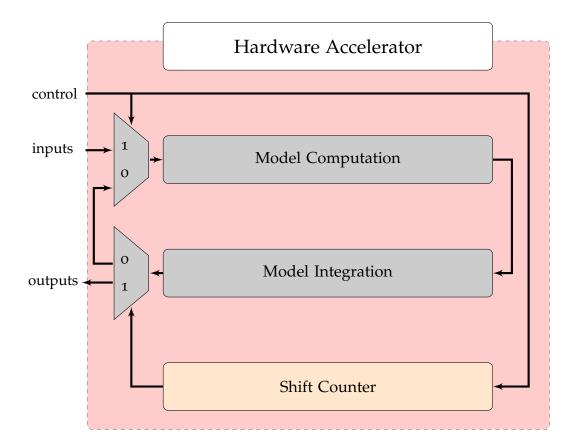

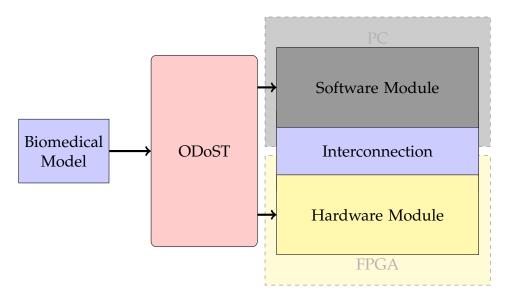

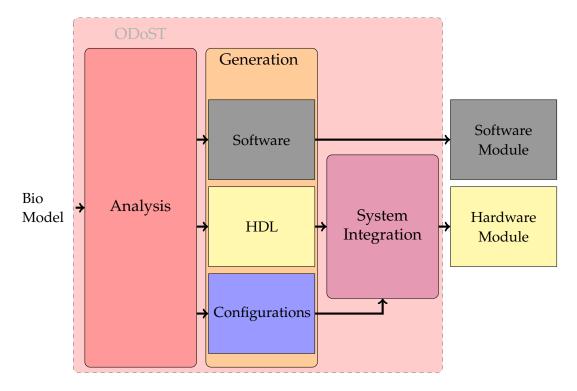

Preliminary evaluation results show that (i) the hardware accelerator module gains significant speedup compared to a pure software implementation, (ii) the scalability of performance results indicates the potential for further performance improvements with a more complex designs, and (iii) a manual implementation of the module is impractical and an auto generation process is required.