### http://researchspace.auckland.ac.nz

### ResearchSpace@Auckland

#### **Copyright Statement**

The digital copy of this thesis is protected by the Copyright Act 1994 (New Zealand).

This thesis may be consulted by you, provided you comply with the provisions of the Act and the following conditions of use:

- Any use you make of these documents or images must be for research or private study purposes only, and you may not make them available to any other person.

- Authors control the copyright of their thesis. You will recognise the author's right to be identified as the author of this thesis, and due acknowledgement will be made to the author where appropriate.

- You will obtain the author's permission before publishing any material from their thesis.

To request permissions please use the Feedback form on our webpage. <u>http://researchspace.auckland.ac.nz/feedback</u>

#### General copyright and disclaimer

In addition to the above conditions, authors give their consent for the digital copy of their work to be used subject to the conditions specified on the <u>Library Thesis</u> <u>Consent Form</u> and <u>Deposit Licence</u>.

# Optimal Task Scheduling on Parallel Systems

Sarad Venugopalan

A thesis submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Faculty of Electrical and Computer Engineering, The University of Auckland, 2015.

## Supervisor

Dr. Oliver Sinnen Co-supervisor Prof. Matthias Ehrgott

"Everything is simple, we are stupid" - Paul Irofti

## Abstract

To fully benefit from a multiprocessor system, the tasks of a program are to be carefully assigned and scheduled on the processors of the system such that the overall execution time is minimal.

Due to the reached physical limits of processor technology the improvements are fading out and manufacturers have moved to multi(core)processors. With multiple processors, however, the performance growth is not automatic anymore and can only be achieved when the processors are efficiently employed in parallel. For the performance and efficiency of a parallel program the scheduling of its (sub)tasks is crucial. Unfortunately, scheduling is a fundamental unsolved problem (an NP-hard optimisation problem), as the time needed to solve it optimally grows exponentially with the number of tasks. I.e. the associated task scheduling problem with communication delays,  $P|prec, c_{ij}|C_{max}$ , is a well known NP-hard problem.

The tasks that are to be scheduled may or may not be dependent on each other and are represented as an acyclic directed graph. The nodes in the graph represent the tasks and the edges between the nodes, the communications. The node cost is the time required for the task to complete and the edge cost is the communication time between two tasks on different processors. We assume a connected network of processors with identical communication links. Further, there is no multitasking or parallelism within a task. Each processor may execute several tasks but no concurrent execution of tasks is permitted. The tasks are to be assigned in such a way as to minimise the overall schedule length.

Existing scheduling algorithms are mostly heuristics (for e.g. the list scheduling algorithm) as they try to produce good rather than optimal schedules. Having optimal schedules can make a fundamental difference, e.g. for time critical systems such as flight control, industrial automation, automotive applications, telecommunication systems, consumer electronics, robotics and multimedia systems. Multiprocessor systems are also popular in small portable devices such as cellphones or navigators to large systems such as industrial robots or aircraft. An optimal schedule may also be used as a benchmark to enable the precise evaluation of scheduling heuristics. Moreover, once an optimal schedule is found, it may be reused when a parallel program is rerun.

This work has two main contributions 1) investigate and propose novel Mixed Integer Linear Programming (MILP) solutions to this scheduling problem, despite the fact that scheduling problems are often difficult to handle by MILP solvers. 2) Propose memory limited versions of the A\* scheduling algorithm since A\* for larger problem instances may run out of memory before finding an optimal schedule. The applicability of existing pruning techniques used on A\* are re-investigated and new pruning techniques to further speedup the memory limited A\*algorithms are proposed.

The first part of the work proposes MILP solutions that use problem specific knowledge to eliminate the need to linearise the bi-linear equations arising out of communication delays. The classic ILP formulation for the scheduling problem and its improved formulations PACKING-USUAL and PACKING-COMPACT are studied. Two new ILP formulations, namely ILP-RBL and ILP-TC are proposed to further speedup the solution. This is attained by re-formulating the constraints and variables needed to linearise the bi-linear forms arising from communication delays between tasks running on different processors. Next, the work in the thesis proposes the formulation ILP-DELTA by introducing new overlap constraints to ensure that no two tasks running on the same processor overlap in time and space. The purpose is to test if re-formulating these constraints would help speedup the formulation.

Further, the work in the thesis proposes the MILP formulations SHD-BASIC, SHD-RELAXED and SHD-REDUCED wherein the size of the proposed formulations in terms of variables are independent of the number of processors. We analyse and discuss the influence of the different MILP components in respect to characteristics of the task graph such as structure and communication to computation ratio. The proposed MILP formulations are experimentally compared with previous MILP formulations used to solve this scheduling problem. The proposed formulations displays a drastic improvement in performance, which allows to solve larger problems optimally. The work also observe strengths and weaknesses of the formulations related to the input characteristics.

The second part of the work proposes two memory limited optimal scheduling al-

gorithms: Iterative Deepening A<sup>\*</sup> (IDA<sup>\*</sup>) and Depth-First Branch and Bound A<sup>\*</sup> (BBA<sup>\*</sup>). When finding a guaranteed near optimal schedule length is sufficient, the proposed algorithms can be combined, reporting the gap while they run. A novel method to find a good initial lower bound close to the optimal schedule length in order to speed-up the execution of IDA<sup>\*</sup> is proposed. Problem specific pruning techniques, which are crucial for good performance, are studied and new pruning techniques proposed for the two memory limited algorithms. Duplicate avoidance without memory and processor normalisation without memory are the pruning techniques proposed. Extensive experiments are conducted to evaluate and compare the proposed algorithms with previous optimal algorithms.

# Acknowledgments

I thank my aunt Suma Verma, uncle Jairam, Mikhil and and Mythili for their love and hospitality, the very first of my extended family in Auckland. I thank Biju Balakrishnan and Priyanka Biju for being there for me. I thank my good friends Ruchi Chowdhary, Pankti Kansara, Hyewon Oh, Leandro Rasmussen, Sizhu (Carol) Zong, Gerry Geneva, Matt Ozball, Urie Bezuidenhout, Aisha Abubakar, Chandan Datta, Jeyavel Jawahar, Arulmozhivarman Parthiban, Anisha, Tomomi Fujikawa, Osberta Li, Dhruv Gaur, Rumi Yokoyama, Misaki Iwamoto, Zong Chen, Shey Mahendran, Helen He, Shradha Khiani, Shin Yee Teh, Dinoy Jose, Yosra, Emma Kang, Dominic Dagbanja, Latha Murugesan, Enoch D, Tony Zhao and Winyee Phong.

I am grateful to my extended family in Auckland, Anna Zhang for her clear, crisp soul and beautiful singing voice, Le Luo for more reasons than I can think of, Asha Rana for her amazing kindness and in teaching me how to cook, Lucy Law for being vibrant and energetic, Alvin Chan for being a sincere friend, Zainab Zeezi for her very beautiful spirit, Rivindu Weerasekera for saying probably-maybe but gets all the work done, Rusiru Karunaratne for being the funny guy, Supriya Siddiqui for her loving personality, Sarah Lim for being a strongly spirited lady and a wonderful violinist, Mika Tokida for her dry humor and evil laughs we share, Sonny P Kumar for being cool as a cucumber, Janu Rangel for having a welcoming heart, Ben Chayanun for bringing out the best of me, Shen Song for being precise and showing me the wisdom of the sunset, Keezrawati Mujan for being kind, Chiara Mannoni Papakonstantinou for having an open heart and an open mind, Cindy Cheung for having deep meaningful conversations, Sohaib Ijaz Majeed for his kindness, Caroline Ding for her empathy, Mark Kong for being caring, Samuel Mandal for his critical thinking, Melinda Thomas for celebrating life, Mike Rosing for inspiring me to solve problems and to continue with my studies, Balamurali B for his humility and vast understanding of humanity, Lu Yu for being my all weather friend, no matter the circumstances. Sahil Chaplot, Parth Doriwala for being kind and caring for the time I lived with them. Prem Kumar, Arijit Chakraborty for letting me stay with them until I completed writing this thesis.

I extend my gratitude to my other friends whom I an constantly in touch with: Aparna Anil, Vipin Thekkedam, Dr. Gopi Krishna Kolluru, Indumathi Ram, Sreedevi Chandrakumar, Kip Kwiatkowski, Dr. Sobha Devi, Dr. Srikanth S, Sujith Raman, Divya Bhaskar, Navin Parakkal, Dr. Sanjeev Saini, Abhinesh Narayanan, Jayasurya Nambiar, Vidya Menon, Dr. Manikandadas Menon, Sankar K, Gesly George, Prof. Bharat B Amberker.

I thank Dilmah for making such fine Ceylon tea and the flat white coffee in New Zealand. They are both fuel for research and responsible for some of the eureka moments.

I thank the Electrical and Computer engineering department staff: Aruna S, Hanlie Van Zyl and Christine Salter; the most student friendly and compassionate staff.

I gratefully acknowledge that this work is supported by the Marsden Fund Council from Government funding, Grant 9073-3624767, administered by the Royal Society of New Zealand and additional postgraduate support from the University of Auckland.

I thank my supervisor Dr. Oliver Sinnen for teaching me how to research, provide valuable and critical feedback, to clearly present work in written form as conference and journal publications and giving me space to wander around the applied mathematics realm and solve some important questions related to the research problem. I thank Prof. Matthias Ehrgott for his feedback and deep insight into linear programming solutions that are used to solve the research problem. I also thank my PHD advisors Dr. Michael Dinneen and Dr. Partha Roop for their valuable feedback.

I thank my dad for the love and the will to see that I get the very best they could give. I thank my brother for having simple solutions to most problems, to take it easy and learn from him. Getting here would not have been possible without my mother, this one is for you mom.

# **Abbreviations and Acronyms**

| BBA*                 | - | Branch and Bound A <sup>*</sup>    |

|----------------------|---|------------------------------------|

| BIP                  | - | Binary Integer Programming         |

| CBL                  | - | Computational Bottom Level         |

| CCR                  | - | Communication to Computation Ratio |

| $\operatorname{CTL}$ | - | Computational Top Level            |

| DAG                  | - | Directed Acylic Graph              |

| DEC-DEV              | - | Decision Destructive               |

| DLB                  | - | Destructive Lower Bound            |

| DRT                  | - | Data Ready Time                    |

| EST                  | - | Earliest Start Time                |

| FSL                  | - | Feasible Schedule Length           |

| FTO                  | - | Fixed Task Order                   |

| GB                   | - | Green Banana                       |

| GXL                  | - | Graph eXchange Language            |

| IDA*                 | - | Iterative Deepening $A^*$          |

| ILP                  | - | Integer Linear Programming         |

| ILP-RBL              | - | ILP-Revised Boolean Logic          |

| ILP-TC               | - | ILP-Transitivity Clause            |

| LB<br>xii            | - | Lower Bound                        |

- MILP Mixed Integer Linear Program

- MINLP Mixed Integer Non Linear Program

- MSPCD Multi-processor Scheduling Problem with Communication Delays

- OSL Optimal Schedule Length

- SL Schedule Length

# Contents

| A | Abstract |                                                                                                                 |     |  |

|---|----------|-----------------------------------------------------------------------------------------------------------------|-----|--|

| A | cknow    | ledgments                                                                                                       | ix  |  |

| A | bbrevi   | ations and Acronyms                                                                                             | xii |  |

| 1 | Intro    | oduction                                                                                                        | 1   |  |

|   | 1.1      | Objective                                                                                                       | 2   |  |

|   | 1.2      | $Problem \ Statement \ \ \ldots \ \ldots \ \ldots $                 | 2   |  |

|   | 1.3      | Task scheduling model $\ldots$ | 3   |  |

|   | 1.4      | $Methodology  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $                         | 4   |  |

|   | 1.5      | Introduction to MILP                                                                                            | 4   |  |

|   | 1.6      | Related Work using Mixed Integer Linear Programming                                                             | 5   |  |

|   |          | 1.6.1 Linearisation of the classic formula $\ldots \ldots \ldots \ldots \ldots \ldots$                          | 7   |  |

|   | 1.7      | Introduction to $A^*$                                                                                           | 11  |  |

|   | 1.8      | Related Work using $A^*$                                                                                        | 12  |  |

|   |          | 1.8.1 A* Scheduling Algorithm                                                                                   | 14  |  |

|   | 1.9      | Thesis Framework                                                                                                | 16  |  |

|   | 1.10     | Contributions                                                                                                   | 17  |  |

| 2 | ILP      | formulations for Task Scheduling Solutions for MSPCD                                                            | 19  |  |

|   | 2.1      | Abstract                                                                                                        | 20  |  |

|   | 2.2      | Introduction                                                                                                    | 21  |  |

|   | 2.3      | Task scheduling model $\ldots$ | 22  |  |

|   | 2.4      | Related work $\ldots$          | 23  |  |

|   | 2.5      | $Proposed \ formulations \ \ \ldots $   | 23  |  |

|   |          | 2.5.1 ILP-REVISEDBOOLEANLOGIC                                                                                   | 24  |  |

|   |          | 2.5.2 ILP-TRANSITIVITYCLAUSE                                                                                    | 26  |  |

|   |          | 2.5.3 Packing formulation                                                                                       | 27  |  |

|   | 2.6  | Computational results                                        | 28                         |

|---|------|--------------------------------------------------------------|----------------------------|

|   |      | 2.6.1 Experimental setup                                     | 29                         |

|   |      | 2.6.2 Result table                                           | 29                         |

|   | 2.7  | Conclusions                                                  | 32                         |

|   |      |                                                              |                            |

| 3 | Bi-L | Linear Reductions for MSPCD Using Integer Linear Programming | 33                         |

|   | 3.1  | Abstract                                                     | 34                         |

|   | 3.2  | Introduction                                                 | 34                         |

|   | 3.3  | Task Scheduling Model                                        | 35                         |

|   | 3.4  | Related Work                                                 | 35                         |

|   | 3.5  | Bi-Linear Reductions                                         | 36                         |

|   | 3.6  | Proposed Formulation                                         | 37                         |

|   |      | 3.6.1 ILP-DELTA                                              | 38                         |

|   |      | 3.6.2 ILP-TC                                                 | 40                         |

|   | 3.7  | Computational Results                                        | 41                         |

|   |      | 3.7.1 Experimental Setup and Result Table                    | 42                         |

|   | 3.8  | Conclusions                                                  | 43                         |

|   |      |                                                              |                            |

| 4 | ILP  | formulations for Task Scheduling with Communication Delays   | 45                         |

|   | 4.1  | Abstract                                                     | 46                         |

|   | 4.2  | Introduction                                                 | 47                         |

|   | 4.3  | Mixed Integer Linear Programming                             | 49                         |

|   | 4.4  | Task scheduling model                                        | 49                         |

|   | 4.5  | Bi-linear reductions                                         | 50                         |

|   | 4.6  | Proposed formulation                                         | 53                         |

|   |      |                                                              | 00                         |

|   |      | 4.6.1 BASIC formulation (SHD-BASIC)                          |                            |

|   |      | -                                                            | 53                         |

|   |      | 4.6.1 BASIC formulation (SHD-BASIC)                          | 53<br>56                   |

|   |      | <ul> <li>4.6.1 BASIC formulation (SHD-BASIC)</li></ul>       | 53<br>56                   |

|   |      | <ul> <li>4.6.1 BASIC formulation (SHD-BASIC)</li></ul>       | 53<br>56<br>56             |

|   | 4.7  | <ul> <li>4.6.1 BASIC formulation (SHD-BASIC)</li></ul>       | 53<br>56<br>56<br>57       |

|   | 4.7  | <ul> <li>4.6.1 BASIC formulation (SHD-BASIC)</li></ul>       | 53<br>56<br>56<br>57       |

|   | 4.7  | <ul> <li>4.6.1 BASIC formulation (SHD-BASIC)</li></ul>       | 53<br>56<br>56<br>57<br>58 |

| 5 | Mer | nory Limited Algorithms for Task Scheduling on Parallel Systems                                                      | 71          |

|---|-----|----------------------------------------------------------------------------------------------------------------------|-------------|

|   | 5.1 | Abstract                                                                                                             | 72          |

|   | 5.2 | Introduction                                                                                                         | 72          |

|   | 5.3 | Related work                                                                                                         | 74          |

|   | 5.4 | Task scheduling model                                                                                                | 75          |

|   | 5.5 | Memory limited optimal scheduling algorithms                                                                         | 77          |

|   |     | 5.5.1 IDA* Scheduling Algorithm                                                                                      | 79          |

|   |     | 5.5.2 $f$ function calculation $\ldots \ldots \ldots$ | 80          |

|   |     | 5.5.3 Branch and Bound A <sup>*</sup> Scheduling Algorithm                                                           | 81          |

|   |     | 5.5.4 Gap Calculation $\ldots$      | 82          |

|   | 5.6 | Lower Bound for IDA <sup>*</sup> Scheduling                                                                          | 83          |

|   |     | 5.6.1 Generic Lower Bound                                                                                            | 83          |

|   |     | 5.6.2 Destructive Lower Bounds                                                                                       | 83          |

|   | 5.7 | State Space Pruning                                                                                                  | 88          |

|   |     | 5.7.1 Fixed Task Order Pruning                                                                                       | 88          |

|   |     | 5.7.2 Equivalent Schedules                                                                                           | 89          |

|   |     | 5.7.3 Partial Duplicate Avoidance                                                                                    | 90          |

|   |     | 5.7.4 Memory Limited Processor Normalisation                                                                         | 91          |

|   | 5.8 | Experimental evaluation                                                                                              | 94          |

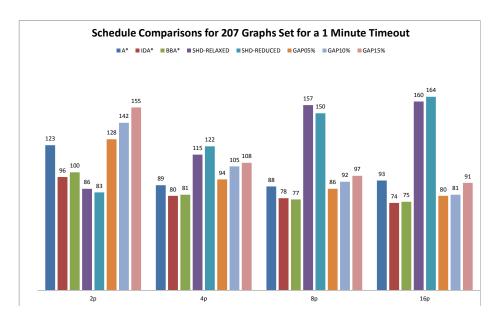

|   |     | 5.8.1 Comparisons with 1 minute time-out                                                                             | 94          |

|   |     | 5.8.2 Comparisons with 12 hour time-out                                                                              | 96          |

|   | 5.9 | Conclusions                                                                                                          | 97          |

| 6 | Con | clusions and Future Work 1                                                                                           | L <b>03</b> |

### References

105

# **List of Figures**

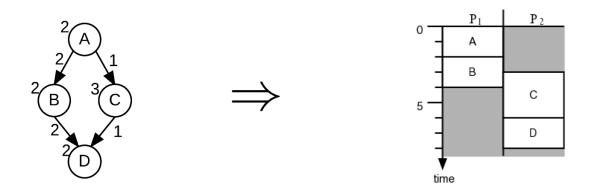

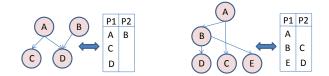

| 1.1 | Tasks scheduled onto two processors                                   | 3  |

|-----|-----------------------------------------------------------------------|----|

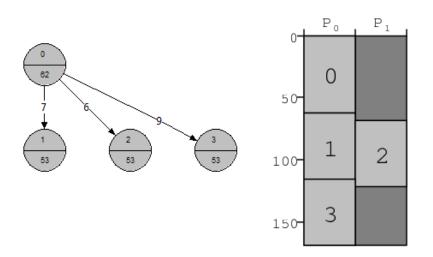

| 1.2 | A fork graph scheduled onto two processors                            | 7  |

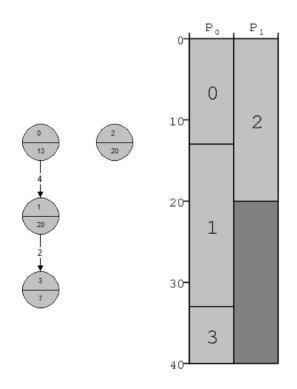

| 1.3 | A random graph scheduled onto two processors                          | 14 |

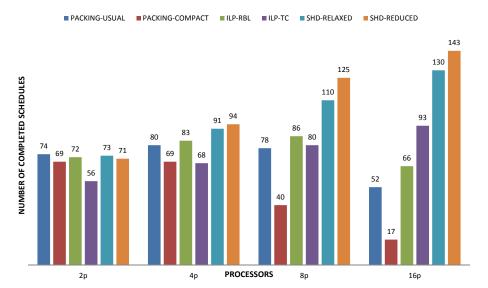

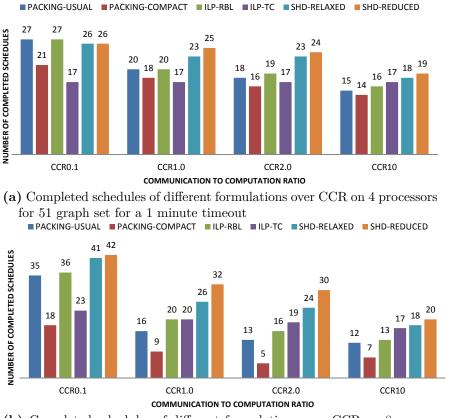

| 4.1 | Completed schedules of different formulations over number of pro-     |    |

|     | cessors                                                               | 60 |

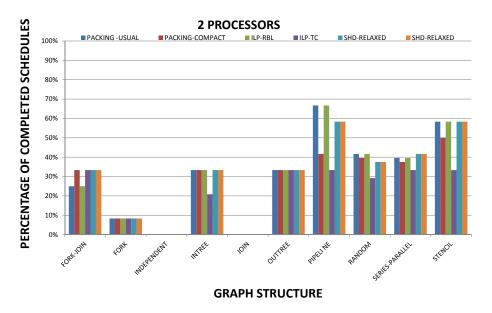

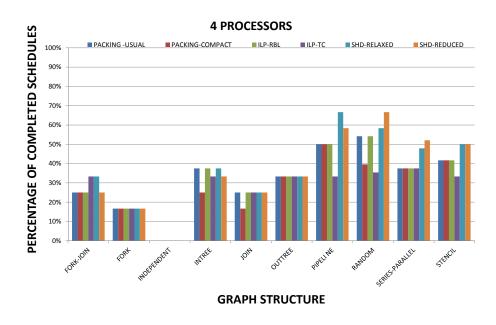

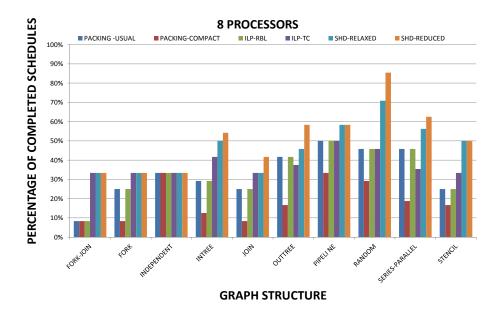

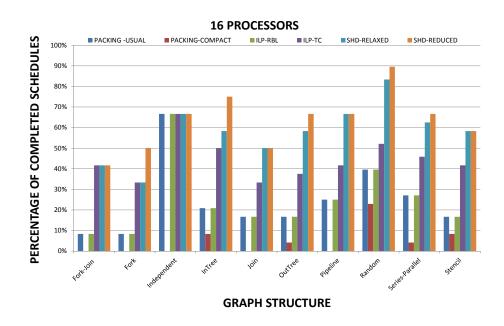

| 4.2 | Completion percentage of formulations over graph structures 2 pro-    |    |

|     | cessors                                                               | 63 |

| 4.3 | Completion percentage of formulations over graph structures on 4      |    |

|     | processors                                                            | 64 |

| 4.4 | Completion percentage of different formulations over graph structures |    |

|     | on 8 processors                                                       | 65 |

| 4.5 | Completion percentage of formulations over graph structures on 16     |    |

|     | processors                                                            | 66 |

| 4.6 | CCR Comparisons on 4 and 8 Processors Set for a 1 minute Timeout      |    |

|     |                                                                       | 67 |

| 5.1 | Graphs with corresponding schedules                                   | 90 |

| 5.2 | Completed schedules (out of 207) in 1 minute over algorithms for      |    |

|     | different number of processors                                        | 95 |

|     |                                                                       |    |

# List of Tables

| 2.1 | Solution Time Comparison of Packing with ILP-RBL                | 30  |

|-----|-----------------------------------------------------------------|-----|

| 2.2 | Solution Time Comparison of Packing with ILP-TC                 | 30  |

| 2.3 | Solution Time Comparison of ILP-RBL with ILP-TC                 | 31  |

| 3.1 | Solution Time Comparison of ILP-DELTA with Packing and ILP-TC   |     |

|     |                                                                 | 42  |

| 4.1 | Comparison between formulations tested                          | 57  |

| 4.2 | Detailed Structure of the 207 Graph Database                    | 59  |

| 4.3 | Performance Statistics on Individual Graph Structures over SHD- |     |

|     | RELAXED and SHD-REDUCED                                         | 62  |

| 4.4 | 12 hour Timeout Comparisons on ILP Formulations - Set 1         | 69  |

| 4.5 | 12 hour Timeout Comparisons on ILP Formulations - Set 2         | 70  |

| 5.1 | Detailed Structure of the 207 Graph Database                    | 95  |

| 5.2 | 12 hour Time-out Comparisons on Algorithms Tested               | 102 |

# **1** Introduction

In the past, engineering and science have strongly benefited from an exponential growth in processor performance. Yet, due to the reached physical limits of processor technology the improvements are fading out [36] and manufacturers have moved to multi(core)processors. With multiple processors, however, the performance growth is not automatic anymore and can only be achieved when the processors are efficiently employed in parallel [21]. For the performance and efficiency of a parallel program the scheduling of its (sub)tasks is crucial. Unfortunately, scheduling is a fundamental unsolved problem (an NP-hard optimisation problem [44]), as the time needed to solve it optimally grows exponentially with the number of tasks. Existing scheduling algorithms are therefore heuristics that try to produce good rather than optimal schedules, e.g. [31], [37], [21], [41], [48], [55], [58], [7], [23]. However, having optimal schedules can make a fundamental difference, e.g. for time critical systems or to enable the precise evaluation of scheduling heuristics. The focus of this work is to find fundamental theoretical results that reduce the solution space, making it possible to efficiently search for an optimal solution.

The tasks that are to be scheduled are represented as a weighted directed acyclic graph. The nodes in the graph represent tasks while directed edges represent data precedence relationships. Precedence relationships (if any) have to be respected at all times. The node cost is the time required for the task to complete its execution on a processor and the edge cost is the communication time between two tasks on different processors. If two tasks with data dependence are mapped onto the same processor, the communication between them is implemented by data sharing in local memory and no communication delay is incurred. The model assumes a fully connected network of homogeneous multiprocessors  $P = \{1, \ldots, |P|\}$  with identical communication links. Each processor may execute several tasks, but each task has to be assigned to exactly one processor, in which it is entirely executed without pre-emption. Further, no multi-tasking or parallelism is permitted within a task.

The execution time for each task on each processor and the data transfer times (or communication delays) between tasks with data dependence are given in advance as part of the task graph.

### 1.1 Objective

The objective of this work is to present fast solutions for the classic problem of scheduling task graphs on parallel systems with communication delay, which is  $P|prec, c_{ij}|C_{max}$ . I.e. to allocate and schedule the tasks onto the processors such that the overall completion time W (makespan) is minimised [11], [40]. Here P specifies the identical processor environment used,  $prec, c_{ij}$  are the precedence characteristics and with communication costs  $c_{ij}$ ;  $C_{max}$  is the maximum completion time of all tasks, which is the objective function to be minimised. Many heuristics have been proposed for task scheduling on parallel systems [27]. While they often provide good results and tend towards the optimal schedule there is no guarantee that the solutions are optimal, especially for task graphs with high communication costs [47], [46]. A number of approximation algorithms have been proposed for the scheduling problem [9], [17]. For the here addressed scheduling problem,  $P|prec, c_{ij}|C_{max}$ , no  $\alpha$ -approximation is known [15]. The only known guaranteed approximation algorithm in [24] has an approximation factor depending on communication costs of the longest path in the schedule.

Given the NP-hardness, finding an optimal solution requires an exhaustive search of the entire solution space. For scheduling, this solution space is spawned by all possible processor assignments combined with all possible task orderings. Clearly this search space grows exponentially with the number of tasks, thus it becomes impractical already for very small task graphs. Hence, few attempts have been made to solve  $P|prec, c_{ij}|C_{max}$  optimally. With the increase in processor power in computers, it is now feasible to find optimal solutions to larger instances of the scheduling problem. An example of a task graph wherein tasks are scheduled onto two processors is shown in Figure 1.1.

## **1.2 Problem Statement**

To develop novel methods to optimally solve the task scheduling problem onto a

Figure 1.1: Tasks scheduled onto two processors

homogeneous multi-processor system for small to medium sized task graphs. I.e. the classic problem of scheduling task graphs on parallel systems with communication delay, which is  $P|prec, c_{ij}|C_{max}$  in the  $\alpha|\beta|\gamma$  notation [18], [51]. This will make the efficient parallelisation of more applications viable, hence allowing performance growth that can satisfy the future needs of engineering and science.

### 1.3 Task scheduling model

Formally, the tasks to be scheduled are represented by a directed acyclic graph (DAG) defined by a 4-tuple G = (V, E, C, L) where V denotes the set of tasks and E represents the set of edges. Each edge  $(i, j) \in E$  defines a precedence relation between the tasks  $i, j \in V$ . A task cannot be executed unless all of its predecessors (parents) have completed their execution and all relevant data is available. The set  $C = \{c_{ij} : (i,j) \in E\}$  denotes the set of edge communication times. If tasks i and j are executed on different processors  $h, k \in P, h \neq k$ , they incur a communication time penalty  $c_{ij}$ . If both tasks are scheduled to the same processor the communication time is zero. For a graph with |V| = n tasks, the set  $L = \{L_1, \ldots, L_n\}$ represents the task computation times (execution time length). Let  $\delta^{-}(j)$  be the set of precedents of task j, that is  $\delta^{-}(j) = \{i \in V | (i, j) \in E, j \in V\}$ . The variables  $t_i$ and  $p_i$  are the main variables that describe a schedule for the problem to be solved. The start time of task i is  $t_i$  and the processor on which task i executes is  $p_i$ . The objective of this task scheduling problem is to allocate and schedule the tasks onto the processors such that the overall completion time W (makespan) is minimised [11], [40].

When the communication links between homogeneous processors are non-identical,

the communication delay is modeled differently. If tasks *i* and *j* are executed on different processors  $h, k \in P, h \neq k$ , they incur a communication cost penalty  $\gamma_{ij}^{hk}$ dependent on the distance  $d_{hk}$  between the processors and on the amount of exchanged data  $c_{ij}$  between tasks ( $\gamma_{ij}^{hk} = \Gamma c_{ij} d_{hk}$ , where  $\Gamma$  is a known constant). For a fully connected processor network,  $\gamma_{ij}^{hk}$  is equivalent to  $\gamma_{ij}$  since the distance  $d_{hk}$ is unity. i.e.  $\gamma_{ij} = \Gamma c_{ij}$ .

## 1.4 Methodology

The proposal is to investigate novel search methods for optimal task scheduling that incorporate new problem specific knowledge. This is significant because generalised solution methodologies (as seen later in the thesis) may not be the best approach to solve the problem. Recent success in other NP-hard optimisation problems shows, e.g. Knapsack [38] or Traveling Salesman Problem [4], that an efficient algorithm for small to medium sized problems might be obtained by pruning the search space with problem specific knowledge.

The two approaches employed are 1) formulating the scheduling problem as a Mixed Integer Linear Program (MILP) 2) Use memory limited derivatives of the popular artificial intelligence A\* algorithm.

### 1.5 Introduction to MILP

Integer Linear Programming are those linear programming problems which have the additional constraint that some or all the variables have to be integers. In contrast to linear programming, which can be solved efficiently in the worst case, integer programming problems are in many practical situations NP-hard. 0-1 integer programming or Binary Integer Programming (BIP) is the special case of integer programming where variables are required to be 0 or 1 (rather than arbitrary integers). This problem is also classified as NP-hard, and in fact the decision version was one of Karp's 21 NP-complete problems [25]. If only some of the unknown variables are required to be integers, then the problem is called a Mixed Integer Linear Program problem. These are generally also NP-hard. Many practical problems in operations research can be expressed as linear programming problems. Certain special cases of linear programming, such as network flow problems and multicommodity flow problems are considered important enough to have generated much research on spe-

cialised algorithms for their solution. Some of the popular problems solved using linear programming are the diet problem, portfolio optimisation, crew scheduling, machine and job scheduling, manufacturing and transportation, vehicle routing, call routing, capacity design in networks, traveling salesman problem and VLSI chip board manufacturing [34].

For the task scheduling problem, the MILP formulations can be broadly classified as discrete time and continuous time approaches [10], [16]. The discrete time approach introduces a new variable for each instant of time on each processor [1]. The number of time variables introduced in this approach explode when diverse execution times are present in the formulation. The continuous time approach, on the other hand, can handle diverse execution times, but its efficiency depends on how well the constraints and variables are formulated. The continuous time approach is further subdivided into three lines - sequencing, slots and overlaps. In sequencing, the formulation involves invoking new variables to determine if one task is executed after another task on the same processor [8], [5]. The number of constraints required to enforce the schedule requirements on each processor are known to grow quickly. In slots, each task is assigned to a space-time vacancy on a processor. The slot defines an order of tasks running on a processor [13], [32]. The start time and end time of tasks entering the slot are not fixed a priori. Since the exact number of slots required on each processor is not known a priori, a conservative number of slots (the number of tasks) has to be reserved and it suffers from a variable blow-up if the number of tasks to be scheduled is large. In overlap, variables are defined to prevent overlap of tasks scheduled on the same processor. Unlike other approaches, the number of variables and constraints in the formulation scales well as the number of tasks to be scheduled increases [10], [11].

## 1.6 Related Work using Mixed Integer Linear Programming

The classic formulation (as it is called in [11]) for a homogeneous multiprocessor system (with non-identical communication links) employs a set of binary variables which control both assignment of tasks to processors and positions in the order of tasks executed by the given processor and a set of continuous variables indicating the start time for each task. Let

$$\forall i \in V, k \in P, s \in tasknum_k; \ y_{ik}^s = \begin{cases} 1 & \text{task } i \text{ is the } s^{th} \text{ task on processor } k \\ 0 & \text{otherwise} \end{cases}$$

and  $t_i \in \mathbf{R}$  be the starting time of task *i* for all  $i \in V$ . Note that  $s \in tasknum_k$  gives the index of the task run on the  $k^{th}$  processor.

The Mixed Integer Non-Linear Program (MINLP) for the scheduling problem is as shown

$$min$$

$Z$  (A01)

$$\forall i \in V \qquad \qquad t_i + L_i - Z \le 0 \quad (A02)$$

$$\forall i \in V \qquad \qquad \sum_{k=1} \sum_{s=1}^{s} y_{ik}^s = 1 \quad (A03)$$

$$\forall k \in P \qquad \qquad \sum_{i=1}^{n} y_{ik}^{1} \le 1 \quad (A04)$$

$$\forall k \in P, s \in V \setminus \{1\} \qquad \qquad \sum_{i=1}^{n} y_{ik}^{s} \leq \sum_{i=1}^{n} y_{ik}^{s-1} \quad (A05)$$

$$\forall j \in V, i \in \delta^{-}(j) \qquad t_{j} \ge t_{i} + L_{i} + \sum_{h=1}^{p} \sum_{s=1}^{n} \sum_{k=1}^{p} \sum_{r=1}^{n} \gamma_{ij}^{hk} y_{jk}^{s} y_{jk}^{r} \quad (A06)$$

A03 ensures that each task is assigned exactly to one processor. A04 - A05 state that each processor cannot be simultaneously used by more than one task. A04 means that at most one task will be on the first one at k, while A05 ensures that if some task is the  $s^{th}$  one  $(s \ge 2)$  scheduled to the processor k then there must be another task assigned as  $(s-1)^{th}$  to the same processor. A06 express precedence constraints together with communication time required for tasks assigned to different processors. A07 define the sequence of the starting times for the set of tasks assigned to the same processor. They express the fact that task j must start at least  $L_i$  time units after the beginning of task i whenever j is executed after i on the same processor k; the M parameter (set to a large positive integer constant) must be large enough so that A07 is active only if *i* and *j* are executed on the same processor *k* and r > s. The mathematical formulation of the Multi-processor Scheduling Problem with Communication Delays (MSPCD) given by A02 - A09 contains linear terms in the continuous *t* variables and linear and bi-linear terms in the binary *y* variables. It therefore belongs to the class of mixed integer bi-linear programs. It is possible to linearise this model by introducing a new set of variables  $\zeta_{ijhk}^{sr} \in [0,1]$  which replaces the bi-linear terms  $y_{ih}^{s} y_{jk}^{r}$  in A06.

Figure 1.2: A fork graph scheduled onto two processors

An example fork graph with 4 tasks (task 0, task 1, task 2 and task 3) and its optimal schedule on 2 processors is shown in Figure 1.2. The optimal schedule length is Z = 168. The Boolean variables  $\sigma_{01}$ ,  $\sigma_{02}$  and  $\sigma_{03}$  are set to 1 to indicate the precedence constraints. From the optimal schedule, the start times are seen to be  $t_0 = 0$ ,  $t_1 = 62$ ,  $t_3 = 115$  and  $t_2 = 62 + 6 = 68$  because  $\gamma_{02}^{01} = 6$ . Also,  $L_0 = 62$ ,  $L_1 = 53$ ,  $L_2 = 53$  and  $L_3 = 53$ . From the optimal schedule, it is also seen that  $y_{00}^1$ ,  $y_{10}^2$ ,  $y_{30}^3$  and  $y_{21}^1$  are set to 1.

### 1.6.1 Linearisation of the classic formula

The above classic formulation has all but linear constraints in A06. The work in [11] linearises A06 by the introduction of a new set of continuous variables  $\zeta_{ijhk}^{sr} \in [0,1]$  to replace the bi-linear term  $y_{ih}^s y_{jk}^r$  in A06.

The linearisation variable  $\zeta_{ijhk}^{sr}$  satisfies the constraints

$$y_{ih}^s \ge \zeta_{ijhk}^{sr} \tag{A10}$$

$$y_{jk}^r \ge \zeta_{ijhk}^{sr} \tag{A11}$$

$$y_{ih}^s + y_{jk}^r - 1 \le \zeta_{ijhk}^{sr} \tag{A12}$$

$\forall i, j, s, r \in V, \forall h, k \in P$ , which guarantees that  $\zeta_{ijhk}^{sr} = y_{ih}^s y_{jk}^r$ . This approach is called the **usual linearisation**.

The number of variables and constraints in the linearised model is  $O(|V|^4|P|^2)$ . Since the constraint size is due to A10 - A12, a compact linearisation approach is used.

Compact Linearisation of the Classic Formula: The idea is to reduce the number of constraints by elimination A10 to A12. This is done by multiplying each assignment constraint in A03 by  $y_{jk}^r$ ; the resulting bi-linear terms are successively linearised by substituting with the appropriate  $\zeta$  variable: giving us a relationship between  $\zeta$  and y variables. The compact linearisation also assumes  $\zeta_{ijhk}^{sr} = \zeta_{jikh}^{rs}$  by commutativity of the product. Thus, the compact linearisation for the scheduling problem with communication delays is as follows:

$$\forall i, j, r \in V, k \in P \qquad \qquad \sum_{h=1}^{p} \sum_{s=1}^{n} \zeta_{ijhk}^{sr} = y_{jk}^{r} \qquad (A13)$$

$$\forall i, j, s, r \in V, \forall h, k \in P \qquad \qquad \zeta_{ijhk}^{sr} = \zeta_{ijkh}^{rs} \qquad (A14)$$

Although, there are still  $O(|V^4||P^2|)$  constraints in A14, these can be used to eliminate half of the linearisation variables and deleted from the formula. Hence, there are only  $O(|V^3||P|)$  in the compact linearisation (see A13).

#### 1.6.1.1 Packing Formulation

The idea on which the model is based is to liken task i to a rectangle of length  $L_i$  and height 1, and to pack all the rectangles representing the tasks into a larger rectangle of height |P| and length W, where W is the total makespan to be minimised [11], [19].

For each task  $i \in V$  let  $t_i \in \mathbf{R}$  be the start execution time and  $p_i \in \mathbf{N}$  be the ID of the processor where task i is to be executed. Let W be the total makespan. Let

$x_{ik}$  be 1 if task *i* is assigned to processor *k*, and zero otherwise. In order to enforce non-overlapping constraints, define two sets of binary variables:

$$\forall i, j \in V \sigma_{ij} = \begin{cases} 1 & \text{task } i \text{ finishes before task } j \text{ starts} \\ 0 & \text{otherwise} \end{cases}$$

$$\forall i, j \in V \epsilon_{ij} = \begin{cases} 1 & \text{the processor index of task } i \text{ is strictly less than that of task } j \\ 0 & \text{otherwise} \end{cases}$$

where  $W_{max}$  is an upper bound on the makespan W, e.g.

$$W_{max} = \sum_{i \in V} L_i + \sum_{i,j \in V} c_{ij} \tag{A31}$$

The makespan is minimised in A15 and A16, the time order on the tasks in terms of the  $\sigma$  variables in A17, similarly the CPU ID order on the tasks in terms of the  $\epsilon$  variables in A18. By A19, the rectangles must have at least one relative positioning on the plane. By A20 a task cannot both be before and after another task; similarly, by A21 a task cannot be placed both on a higher and lower CPU ID than another task. A22 enforce the task precedents; A23 model the communication delays. A24 link the assignment variable x with the CPU ID variables p and A25 are the assignment constraints.

A15 - A30 is also a bi-linear MINLP, where the bi-linearities arise because of the communication delay constraints. This formulation has variables only in i, j, h and k where as the classic formulation and its linearisation had variables in i, j, h, k, s and r. It appears clear that the packing formulation is smaller than the classic one.

Linearisation of the packing formula: A15 - A30 are linearised by introducing variables  $0 \le z \le 1$  as follows:

$$\forall j \in V : i \in \delta^{-}(j), h, k \in P \quad (z_{ij}^{hk} = x_{ih}.x_{jk})$$

Integrality on the linearisation variable z follows from the **usual linearisation** constraints

$$\forall j \in V, i \in \delta^{-}(j), h, k \in P \qquad (x_{ih} \ge z_{ij}^{hk} \land x_{jk} \ge z_{ij}^{hk} \land x_{ih} + x_{jk} - 1 \le z_{ij}^{hk})$$

(A32)

The above linearisation constraints are equivalent to the following **compact linearisation**:

$$\forall i \neq j \in V, k \in P \qquad \qquad \sum_{h \in P} z_{ij}^{hk} = x_{jk} \qquad (A33)$$

$$\forall i \neq j \in V, h, k \in P \qquad \qquad z_{ij}^{hk} = z_{ji}^{kh} \qquad (A34)$$

Although the set of compact linearisation constraints A33 - A34 are smaller than the set of usual linearisation constraints in A32, the difference is not as dramatic as the classic formulation  $O(|V|^2|P|)$  against  $O(|V|^2||P|^2)$ .

The work in Chapters 2 to 4 use the PACKING formulation as a basis for proposing

and deploying faster ILP formulations to speedup the solution time for the optimal task scheduling problem.

## 1.7 Introduction to A\*

For many difficult problems, algorithms require an exponential amount of time or memory or both. Brute force searches are prohibitively slow and the runtime of the algorithm is only fast enough for very small instances of the problem that may not be of sufficient for practical use. The result is a search that is too slow or never completes. The solution, for many problems, is to use pruning techniques to eliminate choices that are impossible to reach the goal state (called pruning the search tree). Pruning techniques may also supply the program with a best guess for the path on which the solution lies. For many problems, it is possible to begin the search with some form of a guess (heuristic) and then refine the guess incrementally until no more refinements can be made and leads to the goal (optimal) state much faster than without the guesses. It is important to note that the nature of the guesses are referred to as heuristics. The algorithm itself is not a heuristic since it finds an optimal solution (subject to its memory constraints).

The basic search strategy will be based on  $A^*$ , a best-first search technique [33], [14], [42].  $A^*$  is guided by a problem specific cost function f(s) for each solution state s, which underestimates the final cost of any solution based on s. In each step the state with the best f(s) is expanded (hence best-first), with the aim that a goal state (i.e. a complete optimal schedule) is found without considering all other states with worse cost values. In general, the better the cost function, the less states have to be considered. Crucial for a successful search method is the investigation of scheduling theory that gives precise cost functions and allows to reduce the search space, as the limited success of the approach in [28] demonstrated. For example, proving that certain task to processor assignments can never lead to optimal solutions significantly reduces the space that has to be searched. This has not been fully investigated before due to the focus on heuristic algorithms that gives a solution close to the optimal solution (but whose quality of solution cannot be guaranteed). However, our results demonstrate that this is very feasible.

Depth first - Iterative Deepening  $A^*$  (IDA<sup>\*</sup>) [26] is a memory limited version of  $A^*$  which tries to reduce the number of iterations in iterative deepening by setting

an initial threshold that is below the cost of the goal node and then successively increases this threshold. It sets the initial threshold to a cost that is below the cost of the goal node and it is then successively increased. When the goal node is found, the IDA\* algorithm terminates. The IDA\* algorithm for any given iteration regenerates all the states for the previous iteration along with the new states generated for the present iteration. The main motivation in using IDA\* is its very limited memory requirement. This gives IDA\* an extremely small memory footprint when compared to A\*. On the downside, IDA\* generates more states than A\* due to iterative deepening. Depth first - Branch and Bound A\* (BBA\*) is another memory bounded algorithm that searches the state space in depth first order. The initial state (feasible solution) is an overestimate on the goal state (optimal solution) [39], [57]. As such it approaches the optimal solution from above, successively improving the best found solution. Both IDA\* and BBA\* are employed for the proposed memory limited task scheduling algorithms in Chapter 5.

# 1.8 Related Work using A\*

A<sup>\*</sup> is a best-first search algorithm that searches through a graph, visiting one node at a time. It does so by looking in each step at the most promising node, according to a cost function f, hence the best-first search. The nodes adjacent to the currently best one are added to the candidate nodes for the next step.

Scheduling the task graph G on processors P is the assignment of a **processor** allocation  $p_i$  and a start time  $t_s(i) = t_i$  to each  $i \in V$ . The task's finish time is given by  $t_f(i) = t_s(i) + L_i$ , i.e. the task's start time plus its computation costs. Let  $tf(p) = \max_{i \in \mathbf{V}: p_i = p} \{t_f(i)\}$  be the **processor finish time** of  $p \in P$  and let  $sl(S) = \max_{i \in V} \{t_f(i)\}$  be the schedule length (or makespan) of schedule S, assuming  $\min_{i \in V} \{t_s(i)\} = 0$ . A fully connected network of homogeneous multi-processor is considered [49].

For such a schedule to be feasible, the following two conditions must be fulfilled for all tasks in G. The **Processor Constraint** in A35 enforces that only one task is executed by a processor at any point in time, which means for any two tasks  $i, j \in V$

$$i = j \Rightarrow \begin{cases} t_f(i) \le t_s(j) \\ \text{or } t_f(j) \le t_s(i) \end{cases}$$

(A35)

A task cannot be executed unless all of its predecessors (parents) have completed their execution and all relevant data is available. The **Precedence Constraint** given in A36 enforces that for every edge  $(i, j) \in E$ ,  $i, j \in V$ , the destination task jcan only start after the communication associated with (i, j) has arrived at  $p_j$ .

$$t_s(j) \ge t_f(i) + \begin{cases} 0 & \text{if } p_i = p_j \\ \gamma_{ij} & \text{otherwise} \end{cases}$$

(A36)

For task  $j \in V$ , its start time on processor p is constrained by the **Data Ready Time (DRT)** and is represented as  $t_{dr}(j, p)$ . The DRT for task j is the time when all communications from task j's predecessors have arrived at p as shown in A37.

$$t_{dr}(j,p) = \max_{i \in \mathbf{parents}(j)} \left\{ t_f(i) + \begin{cases} 0 & \text{if } p_i = p \\ \gamma_{ij} & \text{otherwise} \end{cases} \right\}$$

(A37)

If  $j \in V$  is a source task, then  $t_{dr}(j, p) = 0$ . The task may however not be able to immediately start its execution since the processor assigned may be occupied with the execution of another task. The Earliest Start Time (EST) of task  $i \in V$  on processor p is given by (A38).

$$t_{EST}(i, p) = \max\{tf(p), t_{dr}(i, p)\}$$

(A38)

The computation bottom level of a task  $i \in V$  is the length of the longest path starting in *i*, denoted by  $cbl_i$ . Recursively it is defined in (A39) as

$$cbl_i = L_i + \max_{j \in \mathbf{children}(i)} \{cbl_j\}$$

(A39)

Given the start time of any task i, the schedule length sl is bounded by  $t_s(i) + cbl_i$ . In other words, after the task i has started execution, it still takes (at least) the time to sequentially execute all the tasks on the longest path starting in i.

Let the computation top level of a task  $j \in V$  be defined as the length of the longest path (sum of computational task weights) starting in j, denoted by  $ctl_j$  to the longest length of its parent, excluding its own weight. Recursively it is defined as

$$ctl_j = \max_{i \in \mathbf{parent}(j)} \{ ctl_i + L_i \}$$

(A40)

Figure 1.3: A random graph scheduled onto two processors

In Figure 1.2 we note that task 2 runs on  $P_1$ . Since there are no other tasks running on  $P_1$ ,  $t_f(P_1) = 0$ . The data ready time of task 2 on  $P_1$ ,  $t_{dr}(2, P_1)$  is the sum of processing time of task 1 on  $P_0$  and the communication cost between task 0 and task 2. Hence,  $t_{dr}(2, P_1) = 62 + 6 = 68$ . Then by (A38), Earliest Start Time of task 2 on  $P_1$ , denoted as  $EST(2, P_1) = max(0, 68) = 68$ . From Figure 1.3, it is seen that tasks 1 and 3 have precedence constraints. Then, by the computational bottom length definition in (A39),  $cbl_0 = 13 + 20 + 7 = 40$ . Since, task 2 has no successors,  $cbl_2 = 20$ . I.e. its own computation time on  $P_1$ .

### 1.8.1 A\* Scheduling Algorithm

When  $A^*$  is used for combinatorial optimisation, as in our case, the search space has the form of a tree. Each node (usually called state) of the tree corresponds to a partial solution of the problem to be optimised, which becomes more complete the deeper we get in the tree. The root of the tree is the initial, empty state  $s_{init}$ . While a depth-first search or a breadth-first search only looks at a limited number of possible next states in each step, A\* considers all currently unexplored states and chooses the state s with the best cost value f(s). To achieve that it uses a priority queue, called OPEN, into which all discovered but unexplored states are inserted, ordered according to their cost f. Taking the best state s from OPEN in each step, s is expanded creating new states. This is done by extending the partial solution represented by state s, making it more complete. For each of these newly created states the cost is computed and they are inserted into the OPEN queue. When a state has been fully expanded, it is removed from OPEN and placed into the CLOSED list. The purpose of CLOSED is to be able to detect duplicates, i.e. identical states, before states are inserted into OPEN. The algorithm continues with this process until the state with the lowest cost value is also a **goal state**, i.e. a complete solution. This state is the optimal solution, if certain requirements on the cost function f hold for all states (see Section 1.8.1.1). Algorithm 1.1 gives the pseudo-code for the basic  $A^*$ algorithm [49].

| <b>Algorithm 1.1</b> Pseudo-code for A <sup>*</sup> algorithm              |

|----------------------------------------------------------------------------|

| Input: OPEN, a priority queue, ordered by ascending $f$ -value of elements |

| Output: Optimal solution $s$                                               |

| Method: Algorithm_Astar()                                                  |

| 01: OPEN $\leftarrow s_{init}$                                             |

| 02: While OPEN $\neq \phi$ do                                              |

| $03:  s \leftarrow \text{headOf(OPEN)}$                                    |

| 04: If s complete state then                                               |

| 05: return optimal solution $s$                                            |

| 06: Expand $s$ to new states <b>NEW</b>                                    |

| 07: For all $s_i \in \mathbf{NEW}$ do                                      |

| 08: Calculate $f(s_i)$                                                     |

| 09: Insert $s_i$ into OPEN, unless duplicate in CLOSED or OPEN             |

| 10: $CLOSED \leftarrow CLOSED + s; OPEN \leftarrow OPEN - s$               |

To apply this A<sup>\*</sup> algorithm to solve our scheduling problem, we formulate the following components:

- State s: A partial schedule where some tasks have been allocated and scheduled on the processors.

- Initial state  $s_{init}$ : The initial state represents an empty schedule, where no task has been scheduled yet.

- Expansion operator: Based on state s, a new state is created by scheduling one more task, hence growing the partial solution represented by s. A task that can be scheduled must be *free*, which means it must be either independent or all its predecessors have already been scheduled in the partial schedule of s. The set of all those tasks are denoted as **free**(s). The number of new states expanded from s is then the product of all free tasks times the number of processors, |NEW| = |**free**(s)| · |P|. Each task of **free**(s) is scheduled on every processor in P as early as possible after all other tasks on the same processor according to A38.

- Cost function f: The cost function f(s) is an *underestimate* of the length of a complete schedule based on the partial schedule represented by s.

#### **1.8.1.1** *f* function

According to the A\* principle [50], the f(s) function is an *underestimate* of the exact minimum cost  $f^*(s)$  of any goal state that is based on the state s. Applied to our scheduling problem,  $f^*(s)$  is the minimum schedule length of all possible schedules that can be constructed using the partial schedule represented by s. If the function f(s) fulfils  $f(s) \leq f^*(s)$  for every state s, it is called *admissible*. With an admissible f(s), A\* is guaranteed to find an optimal solution. The number of examined states depends on how accurate f(s) is, i.e. how close it is to  $f^*(s)$ . In general, the more accurate, the fewer states have to be examined and the faster is the algorithm.

## **1.9 Thesis Framework**

The rest of the thesis is organised as follows. Chapter 2 proposes two Integer Linear Programming formulations for the Multiprocessor Scheduling Problem with Communication Delays: ILP - Revised Boolean Logic and ILP - Transitivity Clause to speedup the time to find an optimal schedule. ILP - Revised Boolean Logic is designed for a fast solution when the number of processors the tasks are scheduled on is small and ILP - Transitivity Clause is designed to be efficient when tasks are scheduled on a larger number of processors. Each formulation uses a different linearisation of the Integer Bilinear Programming formulation and is tested on CPLEX using known benchmark graphs for task scheduling.

Chapter 3 proposes an optimal Integer Linear Programming formulation for the Multiprocessor Scheduling Problem with Communication Delays (MSPCD) using a variation to the definition of the task overlap variable and tests if this may help to speedup the formulation. The formulation uses an effective method to linearise the bi-linear forms arising out of communication delays and introduces new overlap constraints to ensure that no two tasks running on the same processor overlap in time and space. The proposed formulation is compared with the previously discussed formulation ILP - Transitivity Clause.

Chapter 4 proposes new MILP formulations for the task scheduling problem with communication delay. The main goal is to learn from and improve upon the formulations proposed in Chapter 2. The three proposed ILP formulations in this chapter are : SHD-BASIC, SHD-RELAXED and SHD-REDUCED. Each part of the formulation is motivated and discussed in detail, explaining its role and importance. A major feature of this formulation is the reduction of the number of variables and constraints by the effective linearisation of the bi-linear equation arising out of communication delays. Further, all variable indices in the MILP formulation are independent of the number of processors. As a result, the constraint complexity of the proposed MILP formulation was reduced to  $O(|V|^2)$ , which is significantly less than previous formulations as analysed in detail.

Chapter 5 proposes two memory limited algorithms, the depth first Iterative Deepening A<sup>\*</sup> (IDA<sup>\*</sup>) and the Branch and Bound A<sup>\*</sup> (BBA<sup>\*</sup>) algorithm. The applicability of known pruning techniques for the A<sup>\*</sup> scheduling algorithm is investigated and new pruning techniques for the memory limited algorithms are proposed. The IDA<sup>\*</sup> and BBA<sup>\*</sup> algorithms are combined to give solutions with a guaranteed quality when finding an optimal solution is not essential.

# 1.10 Contributions

The main contributions of this thesis are:

- Chapter 2: Proposed two new formulations: ILP RBL and ILP TC. The number of constraints formed by ILP-RBL is O(|E||P|<sup>2</sup>), where E is the number of edges in the task graph, V the number of vertices and P the number of processors. When scheduled over a fewer number of processors, the effect of |P<sup>2</sup>| towards the constraint complexity diminishes. The number of constraints formed by ILP TC is O(|V|<sup>3</sup>). The constraint complexity is independent of the number of processors for scheduling. Experimental results validate that their performance is consistent with their constraint complexity and runs faster than known ILP formulations that solve the task scheduling problem.

- Chapter 3: Proposed the formulation ILP DELTA. The definition of the task overlap variable is modified to test its impact on its runtime. By reformulating the ILP to accommodate the new overlap variable, experimental results indicates that ILP-DELTA has a performance similar to ILP-TC but is faster than other previously known ILP formulations.

- Chapter 4: Proposed the ILP formulations SHD-BASIC, SHD-RELAXED and SHD-REDUCED. For all the three proposed formulations, all variable indices in the MILP formulation are independent of the number of processors. As a result, the constraint complexity of the proposed MILP formulation is reduced to  $O(|V|^2)$ . The experimental results indicate a significant speedup over previously known ILP formulations.

- Chapter 5: Proposed memory limited task scheduling algorithms to overcome the memory shortcomings of the A\* scheduling algorithm. Additional pruning techniques are proposed to further speedup the algorithm(s). Experimental results indicates that the memory limited algorithms are able to return an optimal solutions for problem instances where A\* runs out of memory.

# 2 ILP formulations for Task Scheduling Solutions for MSPCD

This chapter is a precursor to the work in **Chapter 4**. It is common to use heuristics to find solutions for task scheduling problem instances. However, there is no guarantee that the heuristic solution is close to the optimal solution.

The contributions of the work in this chapter is to provide

- Optimal solutions for small and medium sized instances of the task scheduling problem.

- Propose two optimal scheduling formulations using Integer Linear Programming (ILP) for the Multiprocessor Scheduling Problem with Communication Delays: ILP-RevisedBoolean Logic (ILP-RBL) and ILP-Transitivity Clause (ILP-TC).

- The number of constraints formed by ILP-RBL is  $O(|E||P|^2)$ , where E is the number of edges in the task graph, V the number of vertices and P the number of processors. When scheduled over a fewer number of processors, the effect of  $|P^2|$  towards the constraint complexity diminishes. The number of constraints formed by ILP - TC is  $O(|V|^3)$ . The constraint complexity is made independent of the number of processors and is thus suitable where there is a larger availability of processors for scheduling. Experimental results validate that their performance is consistent with their constraint complexity and runs faster than known ILP formulations that solve the task scheduling problem.

- Simplified linearisation of the bi-linear forms in comparison to previously known methods.

#### Functionality

- ILP-RBL is designed to work efficiently when the number of processors available to be scheduled on are few.

- ILP-TC is efficient when the number of processors are available to be scheduled on are many.

#### Methodology

• Each formulation uses a different linearisation of the Integer Bilinear Programming formulation and is tested on CPLEX using known benchmark graphs for task scheduling.

#### Outcome

- Faster than previous ILP formulations used to solve this scheduling problem.

- Inline with the functionality expected.

#### Publication

Sarad Venugopalan and Oliver Sinnen. Optimal linear programming solutions for multiprocessor scheduling with communication delays. 12<sup>th</sup> International Conference, ICA3PP 2012. In Yang Xiang, Ivan Stojmenovic, BernadyO. Apduhan, Guojun Wang, Koji Nakano, and Albert Zomaya, editors, Algorithms and Architectures for Parallel Processing, volume 7439 of Lecture Notes in Computer Science, pages 129–138. Springer Berlin Heidelberg, 2012.

# 2.1 Abstract

Task parallelism does not automatically scale with the use of parallel processors. Optimised scheduling of tasks is necessary to maximise the utilisation of each available processor. It is common to use heuristics to find solutions for task scheduling problem instances. However, there is no guarantee that the heuristic solution is close to the optimal solution. The outcome of this work is to provide optimal solutions for small and medium sized instances of the task scheduling problem. Two optimal scheduling formulations using Integer Linear Programming (ILP) are proposed for the Multiprocessor Scheduling Problem with Communication Delays: ILP-REVISEDBOOLEAN LOGIC and ILP-TRANSITIVITYCLAUSE. ILP-REVISEDBOOLEANLOGIC is designed to work efficiently when the number of processors available to be scheduled on is small. ILP-TRANSITIVITYCLAUSE is efficient

when a larger number of processors are available to be scheduled on. Each formulation uses a different linearisation of the Integer Bilinear Programming formulation and is tested on CPLEX using known benchmark graphs for task scheduling.

# 2.2 Introduction

For the performance and efficiency of a parallel program, the scheduling of its (sub)tasks is crucial. Unfortunately, scheduling is a fundamental hard problem (an NP-hard optimisation problem[44]), as the time needed to solve it optimally grows exponentially with the number of tasks. Existing scheduling algorithms are therefore heuristics that try to produce good rather than optimal schedules, e.g.[31], [37], [21], [41], [48], [55], [58], [7], [23]. However, having optimal schedules can make a fundamental difference, e.g. for time critical systems or to enable the precise evaluation of scheduling heuristics. Optimal scheduling is central in minimising the task schedule length. An efficient parallelisation permits scheduling of a large number of tasks onto a large number of dedicated parallel processors to find solutions to generic and specialised problems. It is hence of enormous practical significance to be able to schedule small and medium sized task graphs optimally on parallel processors.

Many heuristics have been proposed for scheduling. While heuristics often provide good results, there is no guarantee that the solutions are close to optimal, especially for task graphs with high communication costs [47], [46]. Given the NP-hardness, finding an optimal solution requires an exhaustive search of the entire solution space. For scheduling, this solution space is spawned by all possible processor assignments combined with all possible task orderings. Clearly this search space grows exponentially with the number of tasks, thus it becomes impractical already for very small task graphs.

The objective is to develop a method that solves the scheduling problem optimally for small to medium sized problem instances using Integer Linear Programming. This will make the efficient parallelisation of more applications viable. To achieve this, two formulations for the Multiprocessor Scheduling Problem with Communication Delays are proposed: ILP-REVISEDBOOLEANLOGIC (ILP-RBL) and ILP-TRANSITIVITYCLAUSE (ILP-TC).

The rest of the chapter is organised as follows. Section 2.3 describes the task scheduling model. Section 2.4 discusses the related work in solving the task scheduling problem optimally. Section 2.5 details the proposed formulations and compares their complexities in terms of number of constraints generated, with previous approaches. Section 2.6 compares the computational results of the proposed formulation with the packing formulation. Section 2.7 concludes the chapter.

# 2.3 Task scheduling model

The tasks that are to be scheduled may or may not be dependent on each other and are represented as an acyclic directed graph. The nodes in the graph represent the tasks and the edges between the nodes, the communications. The node cost is the time required for the task to complete and the edge cost is the communication time between two tasks on different processors. We assume a connected network of processors with identical communication links. Further, there is no multitasking or parallelism within a task. Each processor may execute several tasks but no concurrent execution of tasks is permitted. The tasks are to be assigned in such a way as to minimise the makespan [11], [40]. This model fits the definition of the Multiprocessor Scheduling Problem with Communication Delays (MSPCD) defined as follows: tasks (or jobs) have to be executed on several processors; we have to find where and when each task will be executed, such that the total completion time is minimal. The duration of each task is known as well as precedence relations among tasks, i.e., which tasks should be completed before some others can begin. In addition, if dependent tasks are executed on different processors, data transfer times (or communication delays) that are given in advance are also considered.

More formally, the tasks to be scheduled are represented by a directed acyclic graph (DAG) defined by a 4-tuple G = (V, E, C, L) where  $i \in V$  denotes the set of tasks;  $(i, j) \in E$  represents the set of communications;  $C = \{c_{ij} : i, j \in V\}$  denotes the set of edge communication costs; and  $L = \{L_1, \ldots, L_n\}$  represents the set of task computation times (execution times length). The communication cost  $c_{ij} \in C$  denotes the amount of data transferred between tasks i and j if they are executed on different processors. If both tasks are scheduled to the same processor the communication cost equals zero. The set E defines precedence relation between tasks. A task cannot be executed unless all of its predecessors have completed their execution and all relevant data is available. If tasks i and j are executed on different processors  $h, k \in P, h \neq k$ , they incur a communication cost penalty  $\gamma_{ij}^{hk}$  dependent

on the distance  $d_{hk}$  between the processors and on the amount of exchanged data  $c_{ij}$  between tasks  $(\gamma_{ij}^{hk} = \Gamma c_{ij} d_{hk})$ , where  $\Gamma$  is a known constant). Let  $\delta^{-}(j)$  be the set of precedents of task j, that is  $\delta^{-}(j) = \{i \in V | (i, j) \in E\}$ . For a fully connected processor network  $\gamma_{ij}^{hk}$  is equivalent to  $\gamma_{ij}$  since the distance  $d_{hk}$  is unity. i.e.  $\gamma_{ij} = \Gamma c_{ij}$ .

## 2.4 Related work

Very few attempts have been made to solve the MSPCD optimally. There are two different approaches, one is based on an exhaustive search of the solution space and the other on an Integer Linear Programming formulation. For many problems, heuristics provide a best effort solution of the scheduling problem. It is possible to begin the search with a best guess and then refine it incrementally until it reaches the solution state. The A\* algorithm is one such search algorithm used to solve the MSPCD [28], [45]. A\* is a best-first search technique [14], [42] and also a popular Artificial Intelligence algorithm guided by a problem specific cost function f(s) for each solution state s, which underestimates the final cost of any solution based on s. The main drawback of A\* is that it keeps all the nodes in memory and it usually runs out of memory long before it runs out of time making it unusable for a medium and large sized problem instances.

We propose an optimal scheduling alternative for the solution of the MSPCD that makes use of Linear Programming [11]. It involves linearisation of the bilinear forms resulting from communication delays. The work in [11] discusses a classic formulation and a packing formulation of the MSPCD. Their results indicate that the packing formulation is about 5000 times faster than the classic formulation. In this chapter we propose two significantly improved Linear Programming formulations of the MSPCD and compare them with the packing formulation in [11].

# 2.5 Proposed formulations

The performance of the ILP formulations in [11] suffer from the need to linearise bilinear equations. Two formulations to solve the MSPCD are proposed here: ILP-RBL and ILP-TC. ILP-RBL uses a new technique to linearise the bilinear forms of the packing formulation in [11] resulting from communication delays by readjusting the Boolean logic. ILP-TC reworks the linearisation of the bilinear forms in the packing formulation using a transitivity clause in a manner that aids the elimination of over defined linear equations in ILP-RBL. The runtime complexity of each ILP formulation depends on the number of constraints generated and the number of variables per constraint. The packing formulation and its linearisations in [11] is briefly discussed and the proposed ILP formulations are compared with the packing formulation in terms of constraints generated and number of variables per constraint.

# 2.5.1 ILP-RevisedBooleanLogic

For each task  $i \in V$  let  $t_i \in \mathbf{R}$  be the start execution time and  $p_i \in \mathbf{N}$  be the ID of the processor on which task i is to be executed. Let W be the total makespan and |P| the number of processors available. Let  $x_{ik}$  be 1 if task i is assigned to processor k, and zero otherwise. In order to enforce non-overlapping constraints, define two sets of binary variables as in [11]:

$\begin{aligned} \forall i, j \in V \quad \sigma_{ij} &= \begin{cases} 1 & \text{task } i \text{ finishes before task } j \text{ starts} \\ 0 & \text{otherwise} \end{cases} \\ \forall i, j \in V \quad \epsilon_{ij} &= \begin{cases} 1 & \text{the processor index of task } i \text{ is strictly less than task } j \\ 0 & \text{otherwise} \end{cases} \end{aligned}$

where  $W_{max}$  is an upper bound on the makespan W.

$$W_{max} = \sum_{i \in V} L_i + \sum_{i,j \in V} c_{ij} \tag{A18}$$

The formulation is a min-max problem which involves minimising the maximum start execution times. This is achieved by minimising the makespan W and introducing A02. A03 defines the time order on the tasks in terms of the  $\sigma$  variables, i.e.

ensure  $t_i + L_i \leq t_j$  if  $\sigma_{ij}$  defines an order. The CPU ID order on the tasks in terms of the  $\epsilon$  variables in defined in A04. If the  $\epsilon_{ij}$  variable is set, it implies  $p_j > p_i$ . By A05, at least one or both of the following conditions must be true: task i must finish before task j starts and the processor index of task i must be strictly less than that of task j. By A06, a task cannot both be before and after another task; similarly, by A07 a task cannot be placed both on a higher and lower CPU ID than another task. A08 enforce the task precedences defined by the edges of the graph; A09 and A10 model the communication delays between task i on processor h and task j on processor k. Since  $x_{ih}$  and  $x_{jk}$  are both binary variables and to simulate a Boolean multiplication  $x_{ih} \cdot x_{jk}$ , we use  $x_{ih} + x_{jk} - 1$  in constraint A09. To compensate for the subtraction by 1 in A09 for the case that  $x_{ih}$  and  $x_{jk}$  both are 0, A10 is introduced, which must always be true (for local as well as remote communication). It is also clear from constraint A09 that the processor network need not be fully connected and can take up any connection configuration. All link the assignment variable xwith the CPU ID variables p and A12 ensures that any given task runs only on one processor.

The complexity of this ILP formulation, in terms of constraints and variables, is dominated by A09. For the entire graph, A09 generates |P|(|P| - 1) inequalities in terms of processor combinations for each edge of E and the number of variables per constraint is O(1). Therefore the number of constraints formed by ILP-RBL is  $O(|E||P|^2)$ . In the worst case there are |E| = |V|(|V| - 1)/2 edges, hence in terms on number of nodes ILP-RBL's complexity is  $O(|V|^2|P|^2)$ . However, for task graphs representing real applications, we usually have O(|E|) = O(|V|).

#### 2.5.2 ILP-TransitivityClause

The focus of this ILP formulation is to eliminate the x variables from the formulation, as the ILP is over defined in terms of variables. If we can reformulate A09 without x, we can drop A11, A12 and A16. We replace the x variables in A09 with  $\epsilon$  variables that enforce partial ordering of the processor indices with the help of an additional transitivity clause. A09 and A10 are replaced with A19 and A20. All other equations are retained.

$$\forall j \in V : i \in \delta^{-}(j) \qquad t_i + L_i + \gamma_{ij}(\epsilon_{ij} + \epsilon_{ji}) \le t_j \qquad (A19)$$

$$\forall i \neq j \neq k \in V \qquad \qquad \epsilon_{ij} + \epsilon_{jk} \ge \epsilon_{ik} \qquad (A20)$$