# Libraries and Learning Services

# University of Auckland Research Repository, ResearchSpace

# **Copyright Statement**

The digital copy of this thesis is protected by the Copyright Act 1994 (New Zealand).

This thesis may be consulted by you, provided you comply with the provisions of the Act and the following conditions of use:

- Any use you make of these documents or images must be for research or private study purposes only, and you may not make them available to any other person.

- Authors control the copyright of their thesis. You will recognize the author's right to be identified as the author of this thesis, and due acknowledgement will be made to the author where appropriate.

- You will obtain the author's permission before publishing any material from their thesis.

# General copyright and disclaimer

In addition to the above conditions, authors give their consent for the digital copy of their work to be used subject to the conditions specified on the <u>Library Thesis Consent Form</u> and <u>Deposit Licence</u>.

# Improving the Security of Multiprocessor-Based Embedded System Designs

Peng Seng Benjamin Tan

A thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy in Computer Systems Engineering,

The University of Auckland, 2018.

# **Abstract**

Designers are ambitious; we want to make embedded systems that are more capable, more connected, and ultimately, more complex. To tackle myriad design goals, the development of heterogeneous Multiprocessor System on Chips (MPSoCs) has emerged as a fashionable design paradigm. Embedded systems can be implemented more easily when various components, such as processors, memories, hardware accelerators, and other Intellectual Property (IP) blocks are integrated into a Network on Chip (NoC). This approach allows designers to better leverage parallelism and reduce costs through consolidation of many different functionalities into a single chip.

However, as embedded systems become more capable and Internet connected, so too are malicious entities—as we come to deploy embedded systems in more application domains, attackers have greater incentive to discover and exploit vulnerabilities for illicit gain. Where once security was handled as a secondary concern, or even worse, as an afterthought, designers acknowledge the value in treating security upfront. This thesis investigates strategies to introduce security into the design of multiprocessor-based systems from the very outset. The research we present is focussed on improving security, with the aim of reducing the impact of successful compromises.

After identifying the opportunities for hardware-based support for security mechanisms from a thorough examination of the literature, we begin by developing a conceptual model for describing the relationships between components in a MPSoC and the potential threats in a design. This leads us towards research into potential low-level mechanisms for improving security, and we present digital hardware for implementing decentralised and dynamic access controls in an MPSoC. One challenge in design for security is that design flows are often ad-hoc, so we propose a security-aware design process that systematically generates a security-enhanced MPSoC. Decentralised and dynamic access controls form the foundation for security improvement. Raising the abstraction level once more, we present

research on context-aware protections, where we re-frame memory accesses as service consumption, and enhance access controls with information about when an access should occur as part of a service. Our contributions are a system-level security-aware approach for MPSoC design, hardware support for decentralised and dynamic access controls, and systematic automated design methodologies.

To my family, for supporting my whims and encouraging me to do them as well as I can

# Acknowledgements

#### and words of gratitude

Doctoral-level study is a challenge. The years involved are filled with moments of confusion, doubt, and anxiety...and then, suddenly (and hopefully), moments of profound insight. My experience has been enjoyable and satisfying, and thankfully, moments of intellectual loneliness have been rare. This is in large part due to the people whose paths have intersected with mine for various reasons. I consider myself very fortunate, and these acknowledgements can only begin to reflect my utmost gratitude for the many different people in my life. Alas, this list is not exhaustive, but as I've come to discover, research work can never completely cover everything either.

To begin, I must acknowledge my supervisors. My main supervisor, Dr. Morteza Biglari-Abhari, has been a pivotal figure in my education thus far. Without the unexpected fortune of a summer research scholarship under his supervision (during my undergraduate study), I expect my life at this point would be very different. It was this first experience that really built our relationship, without which my path to research would not have been set. Since the beginning of my doctoral life, his everlasting encouragement has often allayed many of my fears, and our frequent detailed discussions about the research provoked many important strides. Sufficed to say, I have learned a lot under his guidance. I also have to express my gratitude for the teaching opportunities that he provided to me, for the counterbalance of teaching was instrumental in keeping my sanity in check.

Professor Zoran Salcic, my co-supervisor, has been a dependable source of wisdom throughout my studies. As my studies progressed (and his tenure as HOD wound down), the frequency of our interactions increased. He impressed upon me the importance of clarity (particularly when I became lost in a mire of my own ideas and terminology). I am grateful for his poignant and fair criticisms throughout the course of my research. I fondly recall an early meeting which preceded our first accepted publication; we went through page-by-page, and he highlighted all

the flaws and inconsistencies. In many respects, that exercise provided a launching pad for the main bulk of this work.

Outside of my supervisory team I have been privileged to interact with many inspiring academics in our department. Random day-to-day encounters are more valuable than one might expect! Dr. Kevin Wang was an encouraging voice; always sympathetic, and quite fun to chat with about all things University-related. At various times I had insightful and supportive discussions with Dr. HeeJong Park, Associate Professor Catherine Watson, Dr. Mark Andrews, Associate Professor Partha Roop, Dr. Avinash Malik, Dr. Oliver Sinnen, Dr. Bernard Guillemin, Professor Kevin Sowerby, Dr. Matthew Kuo... amongst others... not necessarily discussions about my research, but often about academia as a whole. I'd also like to acknowledge *all* of my past school teachers. Too many to name, but every single one has imparted some lesson, be it in knowledge, skills, or life itself. Thank you.

I have to express my gratitude also to the Embedded Systems lab technicians, first Sunita Bhide, then Hoda Najafi. Always eager to lend a hand, their expertise and support in getting whatever random item I might need was invaluable. I also want to thank the administrative support I received throughout my studies—Aruna Lal and John Lau. Efficient, understanding, and pleasant. Real superstars.

I'm incredibly lucky to have a fantastic group of friends, fellow doctoral candidates with whom to celebrate and commiserate. I've spent countless hours talking in depth with Andrew Chen, Ameer Ivoghlian, Hammond Pearce, Krystine Sherwin, Michael Orr, Nathan Allen, Nicholas Harvey-Lees-Green, Ryan Kurte, and Zac Roberts. We've all voiced our frustrations about silly undergrads, we've shared lunch sessions, and we've built things together. These fine folks have constantly broadened my horizons (largely so I can keep up with conversations), so I thank you all for that! There are also plenty of other fellow postgraduates who have made the overall experience so much richer, and I fear I'll run out of space if I name any more—so thank you to my colleagues too! We'll all get there.

My Mum (Patricia), Dad (Raymond), and my brothers, Benedict and Benett. Always there, always patient—what can I say? It's been a long journey. Mum and Dad have always supported me in whatsoever I desire, the only proviso being that I commit fully to the endeavour. Thank you for letting me do what I do, for all the many years. So, here we are. I can only hope that I've made everyone proud.

And finally, my thanks to Suraksha. You've been unconditionally supportive, of *all* my various enterprises. Always by my side, no matter the stresses and hurdles—so I hope you're proud too. Here's to whatever comes next. Thank you for everything.

AskAuckland Central Alfred Nathan House The University of Auckland Tel: +64 9 373 7599 ext 81321

Email: postgradinfo@auckland.ac.nz

# **Co-Authorship Form**

This form is to accompany the submission of any PhD that contains published or unpublished co-authored work. Please include one copy of this form for each co-authored work. Completed forms should be included in all copies of your thesis submitted for examination and library deposit (including digital deposit), following your thesis Acknowledgements. Co-authored works may be included in a thesis if the candidate has written all or the majority of the text and had their contribution confirmed by all co-authors as not less than 65%.

|                                             |              | pages of this thesis that are extracted from a co-authored work and give the title submission of the co-authored work.                                            |

|---------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Material in Chapter 3 and                   | d 4 is based | on work published in the following paper:                                                                                                                         |

|                                             | nce on Desi  | iri, and Zoran Salcic, "A system-level security approach for heterogeneous gn and Architectures for Signal and Image Processing (DASIP), Rennes, 2016, pp. 853800 |

| Nature of contribution by PhD candidate     | Problem f    | ormulation, experimental work, manuscript writing                                                                                                                 |

| Extent of contribution by PhD candidate (%) | 80           |                                                                                                                                                                   |

#### **CO-AUTHORS**

| Name                   | Nature of Contribution |  |

|------------------------|------------------------|--|

| Morteza Biglari-Abhari | Paper Review/Editing   |  |

| Zoran Salcic           | Paper Review/Editing   |  |

|                        |                        |  |

|                        |                        |  |

|                        |                        |  |

|                        |                        |  |

#### **Certification by Co-Authors**

- the above statement correctly reflects the nature and extent of the PhD candidate's contribution to this work, and the nature of the contribution of each of the co-authors; and

- that the candidate wrote all or the majority of the text.

| Name                   | Signature   | Date    |

|------------------------|-------------|---------|

| ZORAN SALCIC           | J. Salini   | 9/05/18 |

| Mosteza Biolari-Abhari | Nutu Abhini | 10/5/18 |

|                        | , , ,       |         |

|                        |             |         |

|                        |             |         |

|                        |             |         |

AskAuckland Central Alfred Nathan House The University of Auckland Tel: +64 9 373 7599 ext 81321

Tel: +64 9 373 7599 ext 81321 Email: postgradinfo@auckland.ac.nz

# **Co-Authorship Form**

This form is to accompany the submission of any PhD that contains published or unpublished co-authored work. Please include one copy of this form for each co-authored work. Completed forms should be included in all copies of your thesis submitted for examination and library deposit (including digital deposit), following your thesis Acknowledgements. Co-authored works may be included in a thesis if the candidate has written all or the majority of the text and had their contribution confirmed by all co-authors as not less than 65%.

|                                             |               | pages of this thesis that are extracted from a co-authored work and give the title submission of the co-authored work.                                         |

|---------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Material in Chapter 2, 3,                   | and 4 is ba   | sed on work published in the following paper:                                                                                                                  |

|                                             | ations", In J | iri, and Zoran Salcic, "Towards decentralized system-level security for MPSoC-<br>ournal of Systems Architecture, Volume 80, 2017, Pages 41-55, ISSN 1383-7621 |

| Nature of contribution by PhD candidate     | Problem f     | ormulation, experimental work, manuscript writing                                                                                                              |

| Extent of contribution by PhD candidate (%) | 80            |                                                                                                                                                                |

|                                             |               |                                                                                                                                                                |

#### **CO-AUTHORS**

| Name                   | Nature of Contribution |  |

|------------------------|------------------------|--|

| Morteza Biglari-Abhari | Paper Review/Editing   |  |

| Zoran Salcic           | Paper Review/Editing   |  |

|                        |                        |  |

|                        |                        |  |

|                        |                        |  |

|                        |                        |  |

#### **Certification by Co-Authors**

- the above statement correctly reflects the nature and extent of the PhD candidate's contribution to this work, and the nature of the contribution of each of the co-authors; and

- that the candidate wrote all or the majority of the text.

| Name                   | Signature   | Date    |

|------------------------|-------------|---------|

| ZORAN SALCIC           | Z-Salini    | 9/05/18 |

| Mosteza Biglavi-Abhavi | Musica Abhy | 10/5/18 |

|                        |             |         |

|                        |             |         |

|                        |             |         |

|                        |             |         |

AskAuckland Central Alfred Nathan House The University of Auckland Tel: +64 9 373 7599 ext 81321

Tel: +64 9 373 7599 ext 81321 Email: postgradinfo@auckland.ac.nz

# **Co-Authorship Form**

This form is to accompany the submission of any PhD that contains published or unpublished co-authored work. **Please include one copy of this form for each co-authored work**. Completed forms should be included in all copies of your thesis submitted for examination and library deposit (including digital deposit), following your thesis Acknowledgements. Co-authored works may be included in a thesis if the candidate has written all or the majority of the text and had their contribution confirmed by all co-authors as not less than 65%.

|                                             |             | pages of this thesis that are extracted from a co-authored work and give the title submission of the co-authored work.                                           |

|---------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Material in Chapter 5 is I                  | pased on wo | ork published in the following paper:                                                                                                                            |

|                                             |             | ri, and Zoran Salcic. 2017. "An Automated Security-Aware Approach for Design of<br>M Trans. Embed. Comput. Syst. 16, 5s, Article 143 (September 2017), 20 pages. |

| Nature of contribution by PhD candidate     | Problem fo  | ormulation, experimental work, manuscript writing                                                                                                                |

| Extent of contribution by PhD candidate (%) | 80          |                                                                                                                                                                  |

# Name Nature of Contribution Morteza Biglari-Abhari Paper Review/Editing Zoran Salcic Paper Review/Editing

#### **Certification by Co-Authors**

- the above statement correctly reflects the nature and extent of the PhD candidate's contribution to this work, and the nature of the contribution of each of the co-authors; and

- that the candidate wrote all or the majority of the text.

| Name                    | Signature   | Date    |

|-------------------------|-------------|---------|

| ZORAN SALCIC            | Z. Salin    | 9/05/18 |

| MoVieza Biglari-Abhari" | Mulho Abbry | 10/5/18 |

|                         |             |         |

|                         |             |         |

|                         |             |         |

|                         |             |         |

AskAuckland Central Alfred Nathan House The University of Auckland Tel: +64 9 373 7599 ext 81321

Tel: +64 9 373 7599 ext 81321 Email: postgradinfo@auckland.ac.nz

# **Co-Authorship Form**

This form is to accompany the submission of any PhD that contains published or unpublished co-authored work. Please include one copy of this form for each co-authored work. Completed forms should be included in all copies of your thesis submitted for examination and library deposit (including digital deposit), following your thesis Acknowledgements. Co-authored works may be included in a thesis if the candidate has written all or the majority of the text and had their contribution confirmed by all co-authors as not less than 65%.

|                                                  |             | pages of this thesis that are extracted from a co-authored work and give the title submission of the co-authored work. |

|--------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------|

| Material in Chapter 6 is I                       | pased on wo | ork published in the following paper:                                                                                  |

| Benjamin Tan, Morteza E<br>Heterogeneous MPSoCs" |             | ri, and Zoran Salcic, "Towards ContextAware Service Protection for NoC-based                                           |

| Nature of contribution by PhD candidate          | Problem fo  | ormulation, experimental work, manuscript writing                                                                      |

| Extent of contribution by PhD candidate (%)      | 80          |                                                                                                                        |

#### **CO-AUTHORS**

| Name                   | Nature of Contribution |  |

|------------------------|------------------------|--|

| Morteza Biglari-Abhari | Paper Review/Editing   |  |

| Zoran Salcic           | Paper Review/Editing   |  |

|                        |                        |  |

|                        |                        |  |

|                        |                        |  |

|                        |                        |  |

#### **Certification by Co-Authors**

- the above statement correctly reflects the nature and extent of the PhD candidate's contribution to this work, and the nature of the contribution of each of the co-authors; and

- that the candidate wrote all or the majority of the text.

| Name                   | Signature | Date    |

|------------------------|-----------|---------|

| ZORAKI SALCIC          | L-Salini  | 9/05/18 |

| Moltera Biglan - Abhan | My Abhry  | 10/5/18 |

|                        |           |         |

|                        |           |         |

|                        |           |         |

|                        |           |         |

# **Contents**

| Lı | ST OF | Figure | S                                                 | xvii |

|----|-------|--------|---------------------------------------------------|------|

| Lı | ST OF | Tables |                                                   | xix  |

| 1  | Inte  | RODUCT | ION                                               | 1    |

|    | 1.1   | Securi | ity: An Ongoing Battle                            | . 1  |

|    | 1.2   | Under  | estanding Security                                | . 4  |

|    |       | 1.2.1  | What is Security?                                 | . 4  |

|    |       | 1.2.2  | In Pursuit of Perfect Security                    | . 5  |

|    | 1.3   | Challe | enges for Embedded Systems Security               | . 7  |

|    |       | 1.3.1  | Multiprocessor Systems on Chip                    | . 7  |

|    |       | 1.3.2  | Integrating Security into the Design Flow         | . 8  |

|    |       | 1.3.3  | Heterogeneity in Embedded Systems Design          | . 9  |

|    | 1.4   | Aims   | and Contributions                                 | . 11 |

|    | 1.5   | Public | eations and Manuscripts                           | . 13 |

|    | 1.6   | Thesis | structure                                         | . 14 |

| 2  | BAC   | KGROUN | ID AND EXISTING APPROACHES FOR IMPROVING SECURITY | 15   |

|    | 2.1   | Backg  | round on Security Attacks                         | . 15 |

|    | 2.2   | Defen  | ces: Design Approaches and Software               | . 21 |

|    |       | 2.2.1  | Improving Implementation                          | . 23 |

|    |       | 2.2.2  | Supporting Security with Software                 | . 24 |

|    | 2.3   | Defen  | ces: Hardware Support                             | . 27 |

|    |       | 2.3.1  | Processor-centric Protections                     | . 28 |

|    |       | 2.3.2  | Moving Beyond the Processor to the Platform       | . 32 |

|    | 2.4   | Trend  | s and Opportunities                               | . 36 |

|    | 2.5   | Summ   | nary                                              | . 38 |

xiv

| 3 | Fou | ndations for a Security Approach for MPSoCs           | 39 |  |  |  |

|---|-----|-------------------------------------------------------|----|--|--|--|

|   | 3.1 | Motivating Scenario                                   | 39 |  |  |  |

|   |     | 3.1.1 Concurrent, Consolidated, and Complex           | 39 |  |  |  |

|   |     | 3.1.2 Characteristics of MPSoCs                       | 42 |  |  |  |

|   |     | 3.1.3 Threat/Attack Model                             | 43 |  |  |  |

|   |     | 3.1.4 Security aims and requirements                  | 45 |  |  |  |

|   | 3.2 | The Need for a Security Model                         | 47 |  |  |  |

|   |     | 3.2.1 Access Control Policies                         | 47 |  |  |  |

|   |     | 3.2.2 Implications of Sharing                         | 48 |  |  |  |

|   | 3.3 | Abstracting MPSoC components                          | 50 |  |  |  |

|   |     | 3.3.1 The Task/Resource Relationship abstraction      | 50 |  |  |  |

|   |     | 3.3.2 Gauging the Impact of an Attack                 | 53 |  |  |  |

|   |     | 3.3.3 Using the results of Impact Analysis            | 55 |  |  |  |

|   | 3.4 | Summary                                               | 57 |  |  |  |

| 4 | HW  | Support for Distributing Access Controls              | 59 |  |  |  |

|   | 4.1 | Overview                                              | 59 |  |  |  |

|   | 4.2 | Proposed Mechanisms                                   | 60 |  |  |  |

|   |     | 4.2.1 Permissions                                     | 60 |  |  |  |

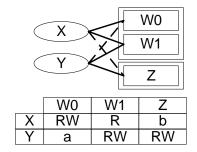

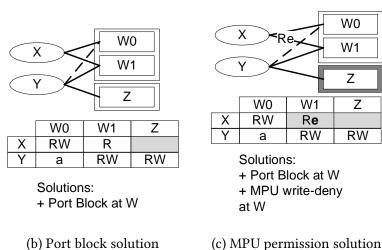

|   |     | 4.2.2 Implementing sharing                            | 63 |  |  |  |

|   |     | 4.2.3 Security Implications and Limitations           | 64 |  |  |  |

|   |     | 4.2.4 Architectural Support: Issues and Trade-offs    | 65 |  |  |  |

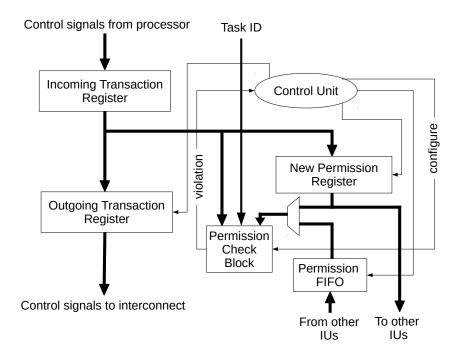

|   | 4.3 | The Isolation Unit                                    | 67 |  |  |  |

|   |     | 4.3.1 Original IU                                     | 68 |  |  |  |

|   |     | 4.3.2 Alternate IU                                    | 70 |  |  |  |

|   |     | 4.3.3 Permissions                                     | 70 |  |  |  |

|   |     | 4.3.4 Connecting IUs                                  | 71 |  |  |  |

|   |     | 4.3.5 IU Operation                                    | 72 |  |  |  |

|   |     | 4.3.6 Synthesis                                       | 74 |  |  |  |

|   |     | 4.3.7 Design Trade-offs                               | 75 |  |  |  |

|   | 4.4 | Experimental Characterisation and Discussion          | 76 |  |  |  |

|   | 4.5 | Related Works                                         |    |  |  |  |

|   | 4.6 | Summary                                               | 83 |  |  |  |

| 5 | Tow | vards Security-Aware Enhancement of an MPSoC Platform | 85 |  |  |  |

|   | 5.1 | Overview                                              | 85 |  |  |  |

|   | 5.2 |                                                       |    |  |  |  |

Contents xv

|   | 5.3        | Security-aware Design                                       | 87 |

|---|------------|-------------------------------------------------------------|----|

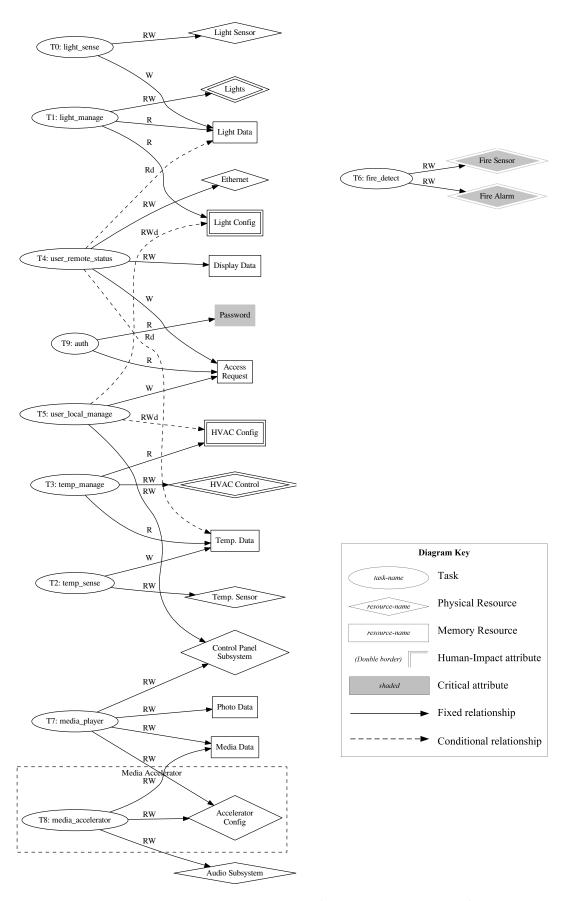

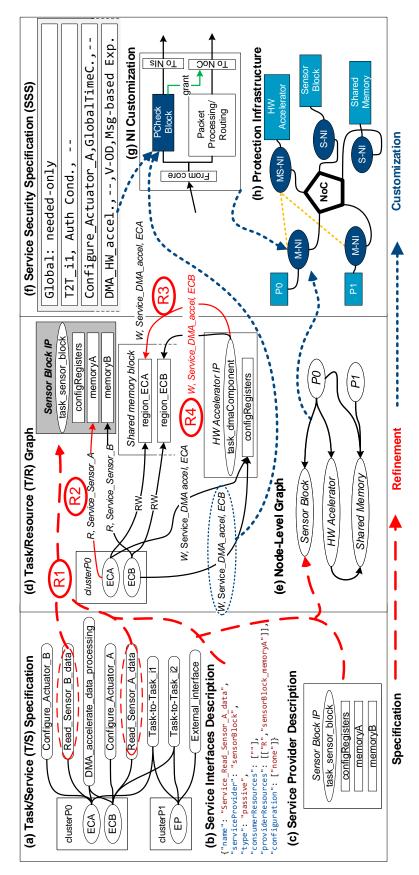

|   | 5.4        | Case Study                                                  | 90 |

|   |            | 5.4.1 The Smart Home Control System                         | 90 |

|   |            | 5.4.2 Execution platform building-blocks                    | 93 |

|   |            | 5.4.3 The Design Problem                                    | 96 |

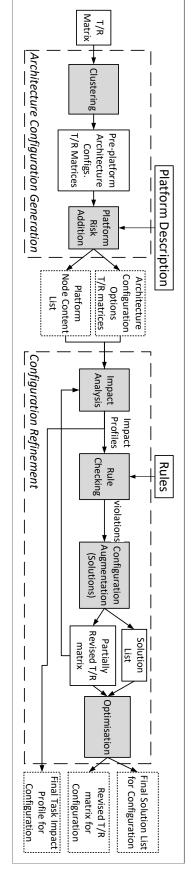

|   | 5.5        | Configuration Generation                                    | 97 |

|   |            | 5.5.1 Inputs                                                | 97 |

|   |            | 5.5.2 Clustering                                            | 98 |

|   |            | 5.5.3 Platform Risk Addition                                | 00 |

|   | 5.6        | Configuration Refinement                                    | )1 |

|   |            | 5.6.1 Rules                                                 | )1 |

|   |            | 5.6.2 Impact Analysis                                       | )3 |

|   |            | 5.6.3 Rule Checking                                         | )4 |

|   |            | 5.6.4 Configuration Augmentation                            | )5 |

|   |            | 5.6.5 Optimization                                          | )7 |

|   | 5.7        | Results and Discussion                                      | )7 |

|   | 5.8        | Summary                                                     | 11 |

| , | T          | MDC-C D 11                                                  |    |

| 6 |            | ODDUCING CONTEXT-AWARE PROTECTIONS TO THE MPSOC PLATFORM 11 |    |

|   | 6.1<br>6.2 | Overview                                                    |    |

|   | 0.2        | Motivation and Background                                   |    |

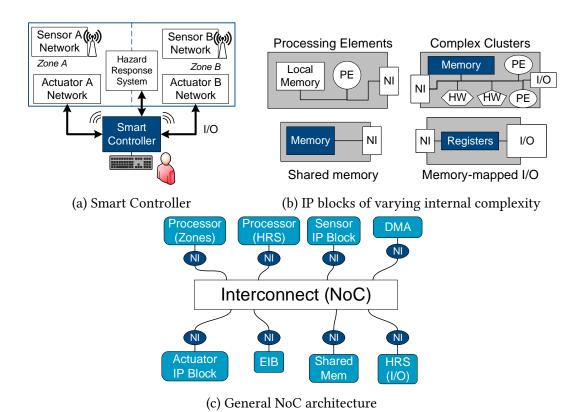

|   |            | 6.2.1 Smart Controller                                      |    |

|   |            |                                                             |    |

|   | 6.3        | 6.2.3 Security Design Challenges                            |    |

|   | 0.3        | Proposed Security Approach                                  |    |

|   |            | 6.3.2 Protecting Services                                   |    |

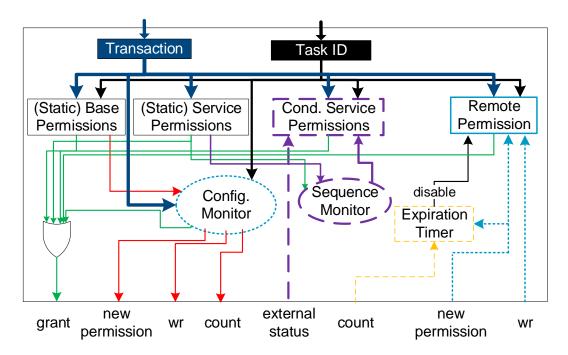

|   |            | 6.3.3 Hardware Support                                      |    |

|   | 6.4        | Integration and Customisation                               |    |

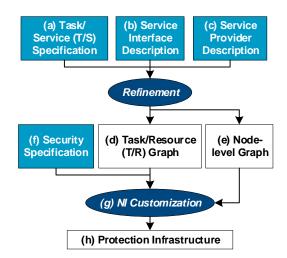

|   | 0.4        | 6.4.1 Approach Overview                                     |    |

|   |            | 6.4.2 Refinement                                            |    |

|   |            | 6.4.3 NI Customisation                                      |    |

|   | 6.5        | Experimental Evaluation and Discussion                      |    |

|   | 6.6        | Related Works                                               |    |

|   | 6.7        | Summary                                                     |    |

|   | 0.7        |                                                             | ,0 |

| 7 | Con        | CLUSIONS AND FUTURE WORK 13                                 | 39 |

|    | 7.1   | Summary and Contributions | 139 |

|----|-------|---------------------------|-----|

|    | 7.2   | Future Work               | 141 |

| A  | List  | of Publications           | 145 |

| В  | SHC   | S Representations         | 147 |

| С  | Exam  | aple Service Descriptions | 151 |

| RE | FEREN | ICES                      | 153 |

# **List of Figures**

| 1.1  | An embedded system for controlling a "smart" home                       | 6  |

|------|-------------------------------------------------------------------------|----|

| 1.2  | A Generalised MPSoC architecture                                        | 8  |

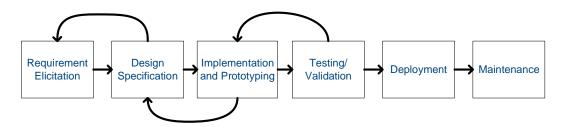

| 1.3  | A general embedded systems design flow                                  | 8  |

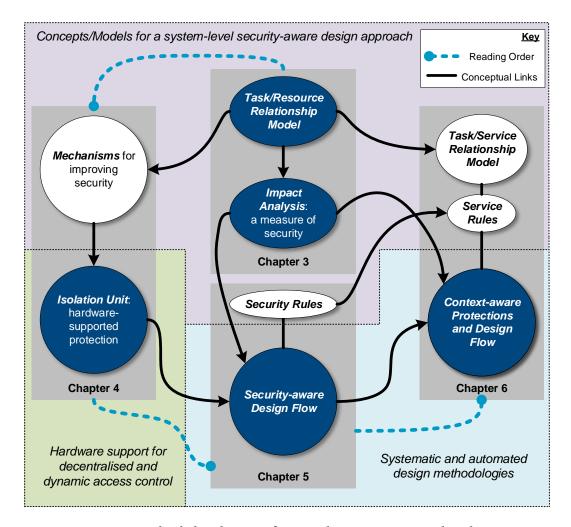

| 1.4  | A high-level view of research progression in this thesis                | 12 |

| 2.1  | Threats and Defences for a MPSoC                                        | 16 |

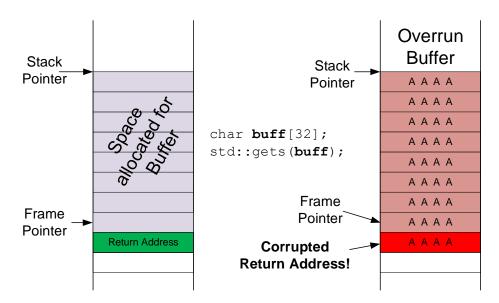

| 2.2  | An example of the quintessential overflow                               | 18 |

| 2.3  | Behaviour of a HW Trojan                                                | 20 |

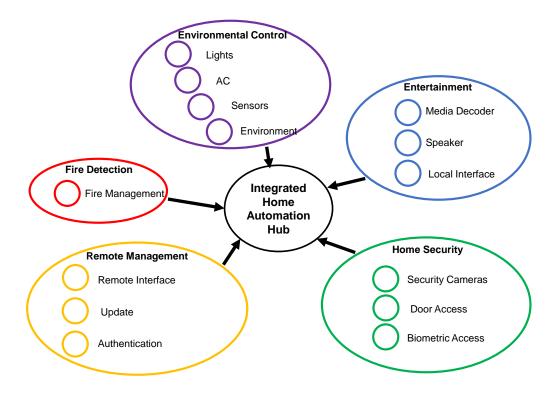

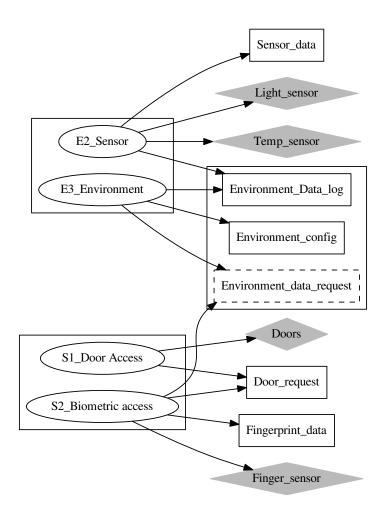

| 3.1  | The Integrated Home Automation Hub                                      | 41 |

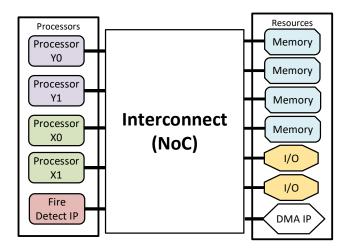

| 3.2  | A typical MPSoC for the Integrated Home Automation Hub                  | 42 |

| 3.3  | Exploiting the capabilities of the platform                             | 45 |

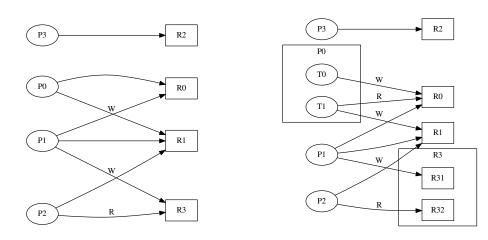

| 3.4  | Different levels of abstraction in a Task/Resource Relationship Graph . | 51 |

| 3.5  | A simplified T/R graph                                                  | 52 |

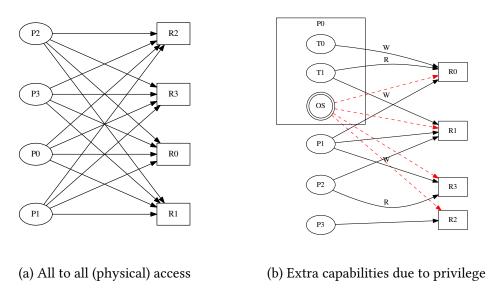

| 3.6  | Illustrating the implications of certain architectures                  | 53 |

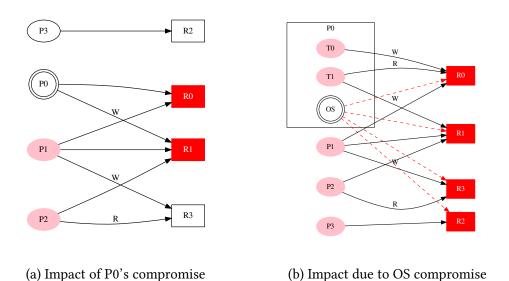

| 3.7  | Illustrating the potential impact of a compromised task                 | 55 |

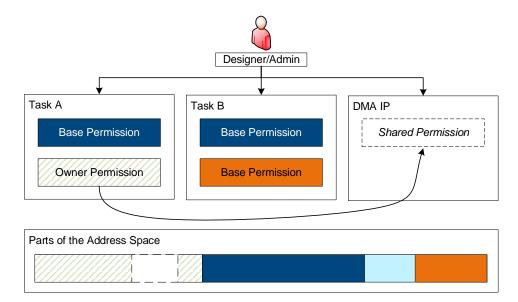

| 4.1  | Delegating authority with different types of permissions                | 61 |

| 4.2  | Illustrating a temporary relationship                                   | 62 |

| 4.3  | An example of temporary region access setup                             | 63 |

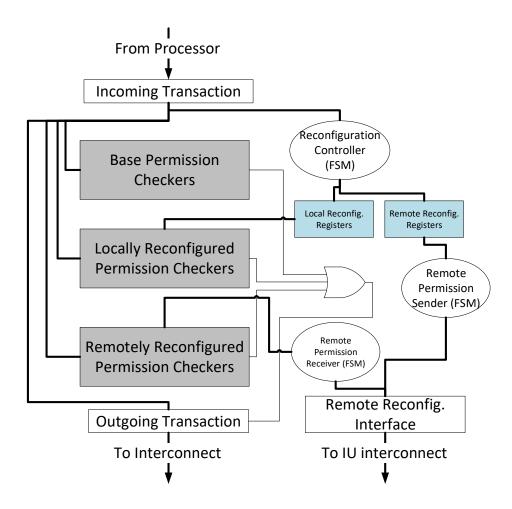

| 4.4  | Simplified view of the original IU internal design                      | 68 |

| 4.5  | Simplified view of the alternate IU internal design                     | 69 |

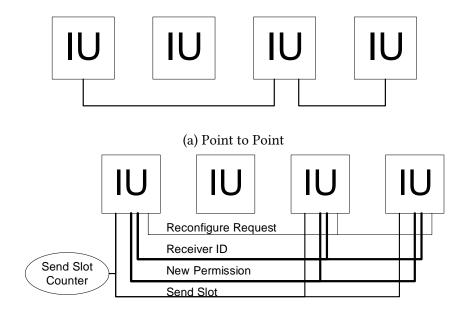

| 4.6  | IU interconnection variants                                             | 71 |

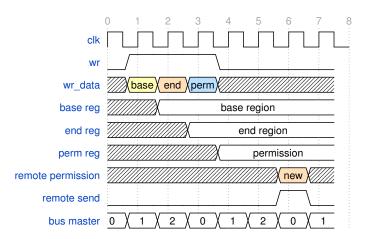

| 4.7  | Timing Diagram for Remote Permission Reconfiguration                    | 72 |

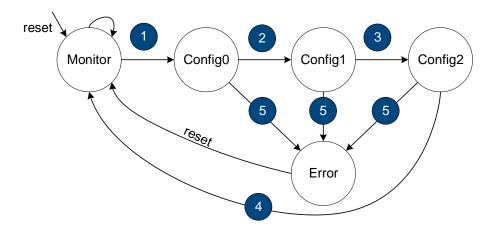

| 4.8  | IU reconfiguration state machine                                        | 73 |

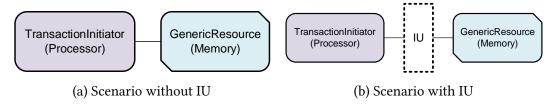

| 4.9  | Single core experiment set-up                                           | 77 |

| 4.10 | Performance penalty of fundamental operations                           | 78 |

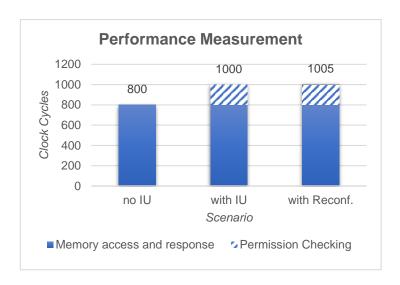

| 4.11 | A four-core subset of the Hub, without IUs                              | 79 |

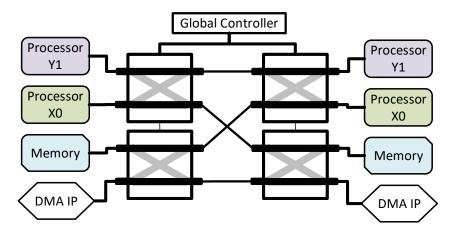

| 4.12 | Timing Diagrams for IUs in the TDMA-MIN NoC                             | 80 |

xviii List of Figures

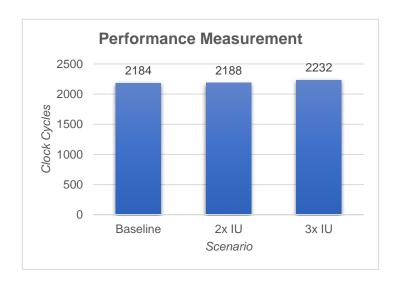

| 4.13 | Performance penalty of multiple IUs                              |

|------|------------------------------------------------------------------|

| 5.1  | Overview of the Proposed Approach                                |

| 5.2  | The Smart Home Control System as a T/R Graph                     |

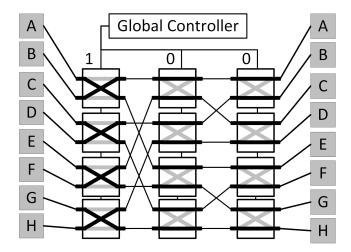

| 5.3  | TDMA-MIN NoC with 8 platform nodes                               |

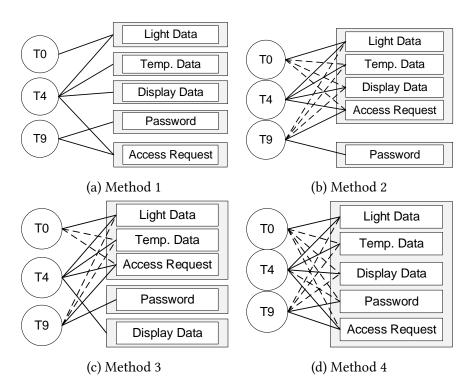

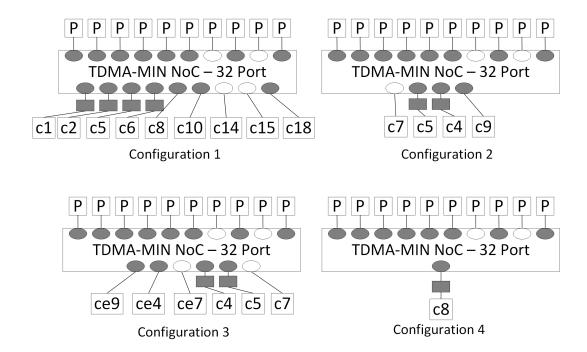

| 5.4  | Cluster Methods applied to SHCS                                  |

| 5.5  | Iterative Solution Addition                                      |

| 5.6  | Graphical representation of configurations                       |

| 6.1  | Motivating embedded system design scenario                       |

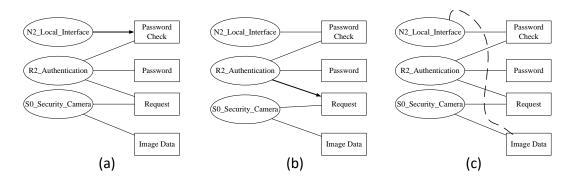

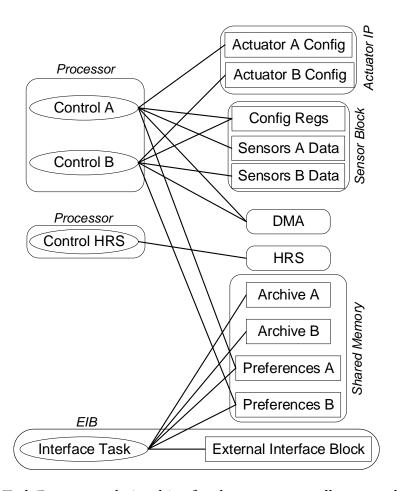

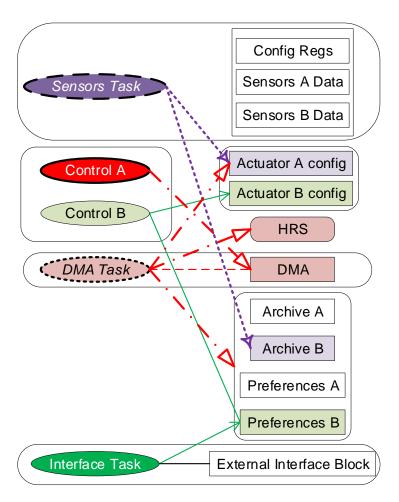

| 6.2  | Task/Resource relationships for the smart controller example 117 |

| 6.3  | Potential attacks in the MPSoC (simplified view)                 |

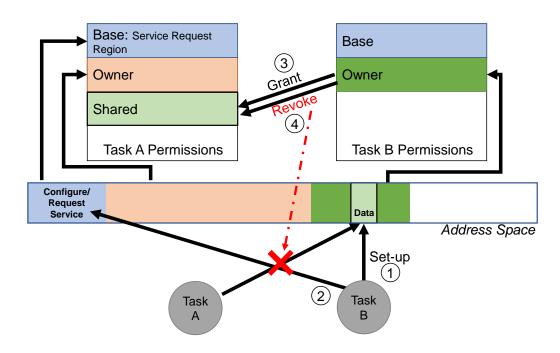

| 6.4  | Example service configuration: DMA block                         |

| 6.5  | Permission Checking Block (PCheck)                               |

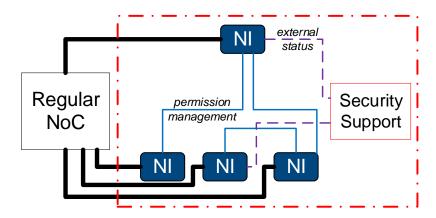

| 6.6  | Security Infrastructure                                          |

| 6.7  | Our proposed design flow                                         |

| 6.8  | A detailed overview of the service-level design flow             |

| B.1  | the SHCS example represented in a CSV file                       |

| B.2  | Optimistic Rules represented in a CSV file                       |

| B.3  | the SHCS example represented in the DOT language                 |

| C.1  | Examples of Service Interface Descriptions, in JSON              |

| C.2  | An Example Service Provider Description                          |

# **List of Tables**

| 3.1 | Task groups (subsystems) of the Integrated Home Automation Hub | 40  |

|-----|----------------------------------------------------------------|-----|

| 3.2 | Task/Resource Relationship Matrix for the four-core example    | 51  |

| 4.1 | Permission Format for the Original IU                          | 70  |

| 4.2 | Permission Format for the Alternate IU                         | 70  |

| 4.3 | IU Synthesis Results                                           | 74  |

| 5.1 | Initial Task/Resource Relationship Matrix for the SHCS         | 90  |

| 5.2 | Added relationships due to Cluster Method                      | 00  |

| 5.3 | Output of Configuration Generator                              | 08  |

| 5.4 | Solutions Added to Satisfy Optimistic rule-set                 | 09  |

| 5.5 | Solutions Added to Satisfy Pessimistic rule-set                | 09  |

| 5.6 | Resource overhead from MPU/IU additions                        | 10  |

| 6.1 | Synthesis Results for various components                       | .33 |

| 6.2 | Typical Overheads of Check/Reconfiguration Operations          | 34  |

CHAPTER 1

# Introduction

Computer systems are ubiquitous, and designs are becoming more complex as designers become more ambitious. This thesis begins with an introduction to the landscape of embedded system design, and highlights some motivations for research into techniques for improving security. After presenting some examples of security exploits and their significant impacts, we examine different facets of security. This leads us towards a discussion of important challenges and opportunities for embedded systems security with a specific focus on multiprocessor system on chip designs. From there we lay out the progression of research work presented in this thesis, and describe the contributions resulting from our efforts in this domain.

# 1.1 Security: An Ongoing Battle

Computers are everywhere. People use computers for work or pleasure, and the entire world is becoming more interconnected through the Internet. Alongside explicitly visible desktop and laptop computers, the number of computers *hidden* and *embedded* within specific application domains has risen exponentially. Embedded systems can be found in numerous sensing and actuating contexts [38], such as within automobiles, industrial automation, medical devices, smart homes, and robotics. Various reports estimate the number of embedded systems in the so-called *Internet of Things* (IoT) to swell to at least the *tens of billions* [81, 89] by 2020. Designs are becoming more complicated and feature-rich [103], and designers often need to create solutions that satisfy several competing requirements, such as resource cost, performance, safety, and timing [93]. The economic value of the IoT has been estimated to reach between \$3.9 trillion to \$11.1 trillion annually by 2025

[82]. The scale and rapid pace of technological developments in the embedded space is incredible.

Embedded systems are often a difficult class of computer systems to categorise, as their functionality can be wide and varied [128]; however, each design typically has an element of being application specific, performing a specialised role in a specific environment, for example:

- **Cyber-physical systems**, such as in automotives, robotics, customizable and reconfigurable manufacturing

- Financial systems, such as point-of-sale (POS) terminals, Automatic Teller Machines (ATMs)

- Medical systems, such as pacemakers, insulin pumps, wireless health monitoring

- **Infrastructure**, such as smart power grids, building condition sensors, intelligent transportation systems

- Consumer products, such as IoT-enabled appliances, wearables, and mobile devices

These types of applications often have sensitive or valuable components, such as private data (for example, financial data, or medical data), or safety-critical parts. In recent years, technology improvements have increased the performance of embedded systems, and ambitions for more efficient and smaller devices has created a shift from uniprocessor systems towards consolidation and integration of many functionalities into heterogeneous *multiprocessor systems on chip* (MPSoC) [103]. And yet, while there is great potential for new innovations and greater human conveniences in the design of new embedded systems, such designs may be deployed into a potentially dangerous and hostile environment. Malicious entities aim to reap financial benefit through illicit means, sneak and steal information to further political agendas, and disrupt or destroy valuable targets for some insidious gain. Designers should be vigilant; they need tools and strategies to prevent, detect, and mitigate security attacks.

Currently, devices ranging from cars to insulin pumps have all been demonstrated to contain critical vulnerabilities [134]. To get a sense of the current land-scape, consider a few examples of recently disclosed attacks<sup>1</sup>.

$<sup>^{1}</sup>$ Not all attacks or vulnerabilities are disclosed by victims in a timely fashion, and some may not even be disclosed at all. Even so, these *known* security breaches stir up plenty of anxiety about the present state of affairs by themselves

In 2010, the Stuxnet worm [65] was discovered and publicised, when it was found to have infected at least 14 industrial sites in Iran, including at least one uranium enrichment plant. In addition to being considered a prime example of state-sponsored cyberwarfare, the worm was especially noted for specifically targeting and subverting an *industrial* control system, upending the assumption that industrial systems are fundamentally robust by default, or obscure enough to be "immune" to security exploits. As discussed in [70], the developers of the worm had significant understanding of the target operating environment, and worked to undermine the system's performance over a period of time, instead of causing a single catastrophic failure.

In 2011, vulnerabilities in cars were reported [17], demonstrating that determined attackers with modest resources were able to exploit a variety of different physical channels for causing harm on modern vehicles. Subsequent research presented in 2014 [2] highlighted risks in "smart cars", where less-critical parts of the system (like the CD player) could be exploited to access and disrupt control functionality. The impact and reach of a successfully compromised part of the design was increased by the consolidation and interconnection of separate Electronic Control Units (ECUs) to improve performance and reduce costs. Modern cars provide a classic example of a mixed-critical embedded system, with a mixture of sensitive tasks for actuation, alongside less-critical tasks for things like infotainment.

In 2013, Target, a large consumer retail company in the United States of America, was attacked by malware known as BlackPOS [90]. Approximately 70-110 million people had credit card information, mailing and email addresses, phone numbers, and names stolen from Target's system, resulting in significant financial fraud and identity theft [41]. Point-of-sale systems are a type of embedded system, designed to facilitate financial transactions in stores. The BlackPOS malware operated by quietly installing itself in the device's operating system (OS) after which it monitored and scanned process memory to identify credit card information. The sensitive information was logged, and exfiltrated on a daily basis. This anomalous (and ultimately, malicious) behaviour was not immediately detected, resulting in losses for many ordinary citizens.

In 2016, a huge Denial-of-Service (DoS) attack was carried out on parts of the Internet's infrastructure, affecting the availability of many popular websites [117]. While DoS attacks are not new, the novelty in this particular instance was the malicious manipulation of millions of vulnerable IoT devices for generating the excessive and disruptive web traffic in the attack. The IoT devices were commandeered to do something they were not designed to do. The sheer volume of devices,

coupled with the immature state of IoT security meant that the attack had quite a significant impact.

Despite the disparate nature of these different attacks, several commonalities emerge. Security was either ignored, or not successfully incorporated into the design of each system. Attacks caused the embedded systems to behave in a way that was unintended by designers, and merely responding to security exploits is insufficient; simply reacting to threats can still lead to considerable losses. Because there can be huge motivation for malicious exploitation, attackers often have significant resources at their disposal. Hence, work needs to be done to improve the security of future devices—we need to develop strategies to add more hurdles for potential attackers. Security should be considered from the very start of the design process instead of being treated as an afterthought.

Consider a future where embedded systems perform many different functions. The design is composed of many different components, sourced from many different places, with many different parts working in parallel. How do we reduce the impact of a compromised part on the system as a whole? Is it possible to improve security such that critical parts of the system continue to operate, even in an attack? The best place to consider security is at design time, where security is treated as a first-class design requirement, as opposed to an after-thought, and with this challenge in front of us, this thesis proposes contributions for improving security. But first, before we proceed, we must first consider the fundamental question: what is security? What does it mean for something to be secure?

# 1.2 Understanding Security

#### 1.2.1 What is Security?

Intuitively, people want to protect their valuable "things" from being harmed or stolen by a malicious entity. Some things might be physical objects, like a favourite toy or electronic device, or even perhaps other people. Other things might be more abstract, such as private information, or *secrets*, such as intellectual property. We can refer to these valuable or sensitive things as *assets* [75]. Security is therefore a type of non-functional requirement which specifies that a given asset should be *protected*. In the literature, security is typically considered as the problem of managing the relationship between attackers (malicious entities that aim to disrupt, damage, or steal assets), and defenders (who are trying to make a system more secure by

introducing various mechanisms) [114, 122]. In an ideal case, there should be no relationship at all—a defender should be able to block all attackers.

However, security is itself a broad concept, which can have different meanings for different people in different contexts [3]. As such, security is often decomposed into several smaller properties [3, 10, 11, 75], which includes the properties of:

**Secrecy**—sensitive information is kept private/confidential, such that only a specific entity (or set of entities) can access said information

**Integrity**—specific assets are protected from unwarranted modification

**Availability**—resources in a system which need to be accessible are accessible, or that the system functions as expected when expected

By devising a design that can satisfy a specific mix of different security properties, we aim to make it *trustworthy*, and develop confidence that our system behaves exactly as we *intend*. The different security requirements indicate properties of the states that our system as a whole is allowed to be in (e.g. the house is always comfortable). If our system is always in one of the allowed states, our system is *secure* [10, 68]. On the other hand, if our system can be made to enter a disallowed state (e.g. the occupancy data is extracted by a malicious party), the system is *insecure*. Naturally, as designers, we should aspire towards the design of a *perfectly* secure system. However, in the next section, we will explore why development of *completely* secure systems proves to be an ongoing challenge.

#### 1.2.2 In Pursuit of Perfect Security

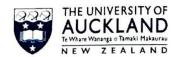

Consider the scenario where we are tasked with the design of an internet-accessible embedded system that is used in automation of a "smart" home (Figure 1.1). The embedded system interacts with various sensors and controls various actuators. As part of its functionality, this system should detect for the presence of occupants, and ensure that the environmental conditions are maintained based on the preferences set by the owners.

We want this design to be *secure*, and so at an informal level, we might want to define a few "high-level" security requirements:

1. We don't want an attacker to make the house uncomfortable (by misconfiguration of the actuators)

Figure 1.1: An embedded system for controlling a "smart" home—different threats from different potential adversaries provides a system-wide challenge

2. We don't want an attacker to know when we are in (or out) of the house (by stealing occupancy sensor data)

The first requirement relates to the *functional* operation of the embedded system; it deals with what the system *does*. The second requirement relates to *data* or *information flow* related aspects of the embedded system. However, this is not enough detail for trying to design a secure system. To accommodate these requirements, we need to consider where potential threats might come from, or try and determine the potential *attack surface*.

For one, the users might be worried about unknown external malicious actors; they may try to access the embedded system through the internet. Or perhaps within the group of legitimate users, some are more *trustworthy*, or have more *authority* than others, and one or more of these users might need to be prevented from misconfiguring the design.

How might we find ways to prevent malicious actions? If we want to ensure that the environment in the house is always comfortable, we may need to consider elements within the design; the software (SW) and hardware (HW) that constitutes the interface between the embedded device and the actual actuators in the house may need to be protected in some way. However, let's consider further potential risks. What if a designer that is involved in the production of the embedded system (either in-house or 3rd party) has malicious intentions? They might introduce bugs, or even deliberately incorrect functionality, which can trigger after the embedded system is deployed. Or perhaps consider issues outside the embedded system itself;

what happens if the physical sensors in the house are tampered with such that they give misleading (false) readings to the embedded system, thus triggering unwanted actuation? If an attacker wanted to really cause damage, they might even simply break in to the house and cut power to the device, or perhaps steal the embedded system itself!

As a means of addressing different security requirements, we need to design and apply an appropriate *security policy*, which specifies the details about how the system should operate, and the environment that it is in. A security policy aims to capture, in detail, the relationships between all the entities inside and outside a system. From our informal discussion thus far, it is clear that security, as a whole, is non-trivial. Security is a cross-system issue, where technical, logistical, and human aspects should be considered to better safeguard assets.

The key point here is that "high-level" security requirements may appear to be misleadingly "simple", and they often entail complex issues across many abstraction levels for real-world systems. One should appreciate that implementing and guaranteeing *complete* or *total* protection in the face of *all* potential adversaries and risks is a gargantuan undertaking. Obviously, the scope of research presented in a single doctoral thesis cannot address or solve *all* aspects of security, so in the next section we examine more closely some of the technical security challenges for embedded systems, with full acknowledgement that our contributions should be considered one part of a far larger picture.

# 1.3 Challenges for Embedded Systems Security

#### 1.3.1 Multiprocessor Systems on Chip

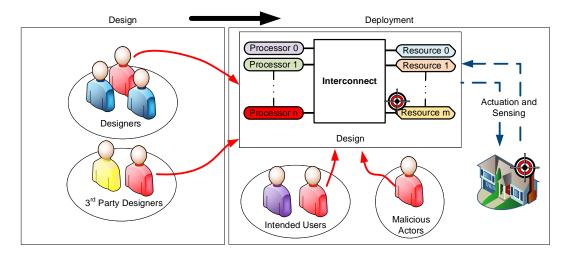

With the growing complexities of embedded system applications, heterogeneous MPSoCs have become a popular platform architecture paradigm. In this thesis, we explore issues related to MPSoC security. MPSoCs are an evolution of the System-on-Chip concept, where a fully fledged computing system is produced by combining a processor (or microcontroller), memories, peripherals, and accelerators into a single chip [108]. One of the key benefits is the adoption of pre-designed and pre-verified hardware and software components, also known as Intellectual Property (IP) blocks, which improves designer productivity, particularly when designers need to implement several different functionalities, with a multitude of various timing, safety, or security requirements [59, 93]. As the next logical progression, MPSoCs integrate more processors to leverage parallelism and further consolidate

Figure 1.2: A Generalised MPSoC architecture

Figure 1.3: A general embedded systems design flow, adapted from [116]

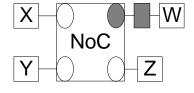

different parts of an application. Various heterogeneous blocks (with varying levels of complexity, as shown in Figure 1.2(a)) are interconnected using some common communication infrastructure, such as shared buses, or a Network on Chip (NoC) [22, 31, 36, 106], as shown in Figure 1.2(b). Designers increasingly use IP blocks sourced from different vendors for their MPSoC designs [77, 103].

#### 1.3.2 Integrating Security into the Design Flow

A general embedded system design flow is illustrated in Figure 1.3. First, designers must elicit and refine both functional and non-functional requirements for a given application. These requirements are then transformed into more detailed design specifications, which are used as the basis for prototyping/implementation of the design. This design process is often iterative, with further refinements to requirements and specifications as more information or gaps in knowledge are revealed, and trade-offs are made. The implementation is then tested, validated, and refined, before ultimately being deployed. In some applications, the final design may also undergo periodic maintenance, such as via firmware updates.

Throughout the design process, high level descriptions and requirements are progressively refined into lower level implementation details, either manually, or through the use of some sort of automated framework [96]. Various levels of abstraction (and automation techniques) are useful for designers, particularly to improve productivity, and to reduce errors from manual implementations. This also helps with design exploration, where different potential configurations can be explored to see how different design metrics are affected by different design decisions.

In order to improve the security of a design, security requirements should be introduced and managed throughout the entire design process [116]. The challenge is in selecting appropriate levels of abstraction throughout the design process, and how to design-for-security. Firstly, different abstraction levels can better model various threats and adversaries for a design, and so to achieve certain security requirements, we need to decide how we represent threats, and how to represent our mechanisms for mitigating those threats. The choice of abstraction affects how well a design "factors in" security issues, and describes the coverage of the chosen security approach. This is an important consideration if we aim for security to be built into the design. Essentially, we need to formulate a *security model* which is compatible with the design flow. Another challenge that exists is that it is difficult to *measure* security—there are different perspectives with which to reason about security, and thus challenges with respect to defining how security could fit in to an exploration/trade-off of different design requirements [94, 119].

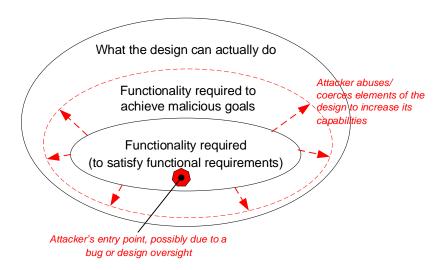

Furthermore, when describing complex behaviours, abstraction can help make aspects of the design process more manageable by hiding certain complexities. Abstractions are also useful when utilising 3rd party components where implementation details are obfuscated or unavailable, as designers can focus on an application's intended behaviour and functionality separately from work on underlying architecture or implementation. As part of the design flow, some assumptions and simplifications are made, and these need to be consolidated with the intended security approach. For example, we might assume that an IP block that is used for accelerating signal processing is used *only* for signal processing, but in reality, it may have the ability to access arbitrary regions of memory. This type of extrafunctional capability should be considered as part of our chosen design abstraction so it can be addressed at the same level of abstraction, particularly if we want to achieve the required protection against spurious accesses.

#### 1.3.3 Heterogeneity in Embedded Systems Design

Embedded systems are typically characterised as being tightly constrained (in terms of resource cost, form factor restrictions, computation capabilities, power

consumption etc.) [102, 128]. Applications often have real-time and reactivity requirements as they perform continuous sensing and actuating to control the environment in some way. Some systems generally operate autonomously (such as in certain control applications), while others (like IoT devices) feature human interfaces, either directly on the device, or remotely through an Internet-enabled interface. The design environment has rising time-to-market pressures, which encourages design re-use [48, 59, 101, 103], whereby general architectures are customised and tuned for specific applications, and deployed on execution platforms like Field Programmable Gate Arrays (FPGAs) [48]. As such, MPSoCs are becoming more heterogeneous, with many parallel and concurrent behaviours implemented in both hardware and software. Platform building blocks can be sourced from a variety of vendors, and different parts of an application can have differing levels of criticality and vulnerability.

These trends highlight a challenge for embedded system security; how do we integrate different functionalities and requirements, while also building security into the design? The challenge lies in creating security approaches that are usable in the context of heterogeneity, as well as in the context of many different concurrent and loosely-coupled functionalities.

In uniprocessor platforms, it is typical to employ a central privileged authority for managing security, usually an operating system (OS) (such as Linux [99]), or hypervisor (such as Xen [137]). This central authority then manages the security features provided by the execution platform. There is an explicit privilege hierarchy, where highly privileged entities (such as the OS) can control access, to all the resources in the system; hence, privilege escalation attacks can cause a significant negative impact. However, in heterogeneous systems, it may be challenging or inconvenient to deploy a single OS across the entire platform. Furthermore, some tasks may execute "bare-metal" for performance or timing reasons, and there may be multiple IP blocks (that implement some fixed functionality) with direct memory access (DMA) capabilities. These system components need to be managed properly to ensure that security restrictions that are defined by the designer are respected.

As will be explained later in this thesis, there are many different security mechanisms that could be used to better safeguard assets in a system. Development of new security approaches, especially for a multiprocessor context, remains an ongoing topic for exploration. However, it is challenging to select and integrate a given mechanism to address a given security requirement. For example, designers might identify memory protection [76] as a useful *general* approach for improving a

design's security. Part of the challenge is knowing where to deploy the memory protection mechanism, and how the specific parts of the mechanism can be mapped to entities within the specific application (or vice versa). In other words, which permissions should be created, and where should they be enforced—security mechanisms should be linked to specific security requirements. We need to develop a suitable protection infrastructure for the given application, even when components do not have a common software foundation, are not *security-aware* (i.e. without built-in security mechanisms), or even if their internal designs are not fully accessible by system designers. Moreover, designers should be able to quantify the implications of adding a mechanism into the design (for example, in terms of cost overhead), or understand the implications of omitting security additions in lieu of other design requirements. As such, the process for exploring and incorporating security features into an embedded system design should be systematic.

#### 1.4 Aims and Contributions

As a response to these various challenges in the arena of embedded system security, this thesis proposes and explores novel approaches for improving security of MPSoCs. Broadly, our primary aims are to:

- Reduce the impact of an initially successful incursion in a heterogeneous MPSoC

- Facilitate easier accommodation of security concerns into the design flow

- Provide frameworks for design space exploration which are security-aware

- Investigate the feasibility of customising MPSoC architectures to provide a hardware-supported security *foundation*

To achieve these aims, our research story begins at an abstract level, where we first develop a conceptual model for describing the relationships between components in a MPSoC and the potential threats in a design. This leads us towards development of low-level mechanisms for improving security; these are then used to influence the concrete design of digital hardware for supporting decentralised and dynamic access controls. To deal with the bigger problem of designing for security, we then create a security-aware design flow to systematically generate a security-enhanced platform. This thread culminates in our research on context-aware protections at

Figure 1.4: A high-level view of research progression in this thesis

a higher service-level abstraction. The progression of this research is illustrated in Figure 1.4. Overall, this thesis will present the following contributions:

• A system-level security-aware approach for MPSoC design: A security model provides the framework for formulating security requirements/specifications, capturing potential security risks, and management of potential security issues. At the system-level we want to reason about the design at a high level of abstraction. By considering several general approaches, alongside the specific context of heterogeneous MPSoC design, we propose a security approach and novel abstractions to incorporate security into the design flow. With this approach, we can define security rules to specify requirements for protecting parts of a design with different levels of criticality. The proposed approach serves as the foundation for novel system-level techniques and tools for improving security that are presented in this thesis.

- Hardware support for decentralised and dynamic access control: A security infrastructure as part of the MPSoC architecture is necessary for improving security. In this thesis we present prototype implementations of the *Isolation Unit* (IU), which are customisable hardware blocks that can be inserted into a MPSoC design to improve system security. These IUs are dedicated memory protection blocks that do not require an OS for run-time customisation. Two variations of the IU, implemented in VHDL, are described and characterised by their resource cost when synthesised for an FPGA-based execution platform. We also investigate the feasibility and utility of enhancing and integrating the functionality of the Isolation Unit into a Network-on-Chip (NoC) network interface. Access controls are also further enhanced with the notion of *context*, where the time of an access or sequence of operations is also checked for correctness.

- Systematic and automated design methodologies: To move away from ad-hoc design methodologies, we present some novel approaches to improve security as part of the design flow. We propose a systematic methodology for generating and exploring customised MPSoC architecture configurations, and analysing the specific realisation of the application to check for compliance with certain security rules. This presents groundwork for facilitating a more robust trade-off between security and other design metrics. We also present a novel top-down design flow for customizing a protection infrastructure to improve MPSoC security, even where components are heterogeneous or not security-aware. As part of this, we also describe a service-level abstraction to deal with complex IPs, to re-frame security as protection of services, and protection from service providers.

# 1.5 Publications and Manuscripts

This thesis features manuscripts that have been published:

- Benjamin Tan, Morteza Biglari-Abhari, and Zoran Salcic, "A system-level security approach for heterogeneous MPSoCs," 2016 Conference on Design and Architectures for Signal and Image Processing (DASIP), Rennes, 2016, pp. 74-81. doi: 10.1109/DASIP.2016.7853800

- Material from this paper can be found in Chapter 3 & 4

Benjamin Tan, Morteza Biglari-Abhari, and Zoran Salcic, "Towards decentralized system-level security for MPSoC-based embedded applications", In Journal of Systems Architecture, Volume 80, 2017, Pages 41-55, ISSN 1383-7621 doi: 10.1016/j.sysarc.2017.09.001.

- Material from this paper can be found in Chapter 2, 3 & 4

- Benjamin Tan, Morteza Biglari-Abhari, and Zoran Salcic. 2017. "An Automated Security-Aware Approach for Design of Embedded Systems on MP-SoC". ACM Trans. Embed. Comput. Syst. 16, 5s, Article 143 (September 2017), 20 pages. doi: 10.1145/3126553

- Material from this paper can be found in Chapter 5

as well as manuscripts that are under preparation/under review:

- Benjamin Tan, Morteza Biglari-Abhari, and Zoran Salcic, "Towards Context-Aware Service Protection for NoC-based Heterogeneous MPSoCs"

- Material from this paper can be found in Chapter 6

#### 1.6 Thesis structure

The remainder of this thesis is as follows. In Chapter 2 we provide a critical discussion of the state-of-the-art for embedded systems security, with a particular focus on mechanisms and frameworks for MPSoC design. In Chapter 3 we explore a variety of security models, examining the utility of each in the context of MPSoC design. We present a threat model that underpins and motivates our research contributions, and propose a design abstraction for security analysis. In Chapter 4 we apply our MPSoC security model, and discuss various mechanisms needed to provide a more secure foundation. This leads us to the development of the Isolation Unit. In Chapter 5 we propose a systematic and automated approach for designing embedded systems on MPSoCs, where Isolation Units are customised and inserted into the platform to address designer-specified security rules. In Chapter 6 we present a novel service-oriented approach to MPSoC design, and move Isolation Unit functionality into network interfaces, while also providing transparent permission management as part of a service consumption paradigm. Finally, in Chapter 7 we make some concluding remarks, and contemplate potential future directions for this research.

# Background and Existing Approaches for Improving Security

Researchers have tried to consider and manage security issues for a long time. In this chapter we discuss some background concepts on security issues, such as examples of mechanisms used in attacks, and then critically examine various techniques for improving SoC security, with particular interest at the implications when we consider the multiprocessor context. In looking at different types of attacks, and different types of defences, we present a view of the state-of-the-art for computer security, examining both more established techniques for computers generally, followed by some emerging approaches for MPSoCs. We identify common themes and opportunities within existing literature for improving computer system security, and this provides the context for the research contributions presented in this thesis. Our story begins by looking at attacks in a general sense (§2.1), before moving into a discussion of defences (§2.2 and §2.3).

# 2.1 Background on Security Attacks

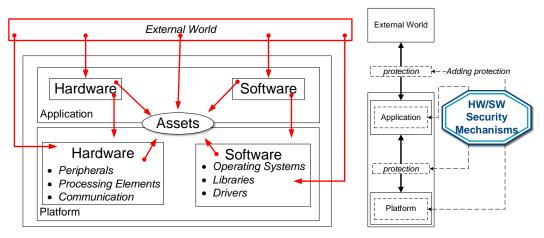

Security is about protection of *assets* which are specific to an application. Consider Figure 2.1, which represents an MPSoC as logically partitioned in two: hardware/software components related to implementation of the application's *functionality*, and the hardware/software components that form the underlying *platform*. The application level contains the "logic" that designers implement, such as control algorithms, user interface behaviours, and data processing operations. The platform consists of components that we can consider to be the infrastructure, such as processing elements and memories that application software executes on, as well as other hardware, such as I/O interfaces, accelerators, peripherals, and on-chip

- (a) Internal and external threats/attack vectors to a MPSoC

- (b) Different possible protection boundaries

Figure 2.1: Threats and Defences for a MPSoC

buses/networks. In addition, we consider system software, like operating systems, shared libraries, and drivers as part of the platform, as they support the application's execution. Security exploits occur as attackers attempt to take advantage of inadvertent (or deliberate) flaws, or vulnerabilities, within the application or platform. Various attack strategies might target the application (exploiting issues in application logic, or implementation), target the hardware/software in the platform, or employ a combination of attack *vectors* in the mission to compromise an asset.

In 1994, Landwehr et al. formulated and presented a useful taxonomy for categorising computer security program flaws [69]. Their taxonomy provides three dimensions of classification regarding *how* a flaw is introduced, *when* the flaw is introduced, and *where* in a system it appears, referred to as *genesis*, *time of introduction*, and *location* respectively. Several key points are raised in their discussion, reflecting issues in the design practices of the day, and their view of the "terrain of computer program security flaws":

- flaws can be introduced *intentionally*, where malicious parties directly add

malicious code to systems, or where flaws are introduced by functionalities

that are added non-maliciously by legitimate designers that can later be exploited (for example, debugging interfaces for making the design process easier)

- flaws can also be introduced *inadvertently*, especially as a result of designs that are "composed of many modules, and involving many programmers", as

issues such as under-resourcing might result in insufficient oversight (leading to bugs which are missed in reviews), or inadequate documentation (leading to implementation mistakes)

- the system life-cycle can be abstracted to three phases of *development*, *mainte-nance*, and *operation*—flaws introduced during development may appear during requirement/specification design, in source code, or object code

- security issues are likely to arise due to "competition between security requirements and other functional requirements", or where solutions are "not deemed to be cost effective"—which implies design trade-off

- risk from flaws introduced by hardware, while not prevalent at the time, still

warranted a discussion, with the view that there will be an increasing need

to consider the impacts of hardware-based exploits

Since [69] was published, the nature of fundamental flaws used in security attacks have persisted; the same grievances regarding validation errors, privilege escalation, and exploitation of poorly documented (or undocumented) "features" are present in recently disclosed vulnerabilities. Despite decades of work in computer security, our current state of affairs is still hamstrung by the prevalence of applications that are fraught with vulnerabilities resulting from poor implementation. In short, poor **software**. In an analysis of vulnerability trends from 2008-2016 [64], Kuhn et al. discovered that simple coding errors continue to be widespread. Such errors, like omitting a bounds check (resulting in buffer overflows) are trivial, yet continue to have drastic impacts on overall security. It should be unsurprising then, that the literature often features technical mechanisms and strategies to bolster security at the platform level, accepting that applications are likely to be vulnerable, or already compromised.

Research in improving security is typically contextualised as a response to security attacks. To better understand the trends and opportunities in security research, we will now look at some exemplary attack types, particularly as we shift focus from single to multiprocessor systems.

#### An example attack vector: Buffer Overflows

A common aim for attackers is to seize control of a computer by controlling a processor's execution. One example of a common attack vector is the targeting of software flaws that deal with memory buffers. Useful programs usually receive data

Figure 2.2: An example of the quintessential overflow

from the external world, and this data needs to be stored in memory. When using lower level programming languages, such as C [54], care must be taken to manage memory appropriately; after all, a processor will blindly execute whatever instructions it is given. Consider Figure 2.2, which illustrates a stack, the memory structure used as temporary storage in a program's execution. The stack holds data for the currently executing function, as well as other critical data such as the return address. Space on the stack is allocated for a buffer, buff, into which user input is stored. However, the C standard library function gets() does not perform any input validation or checks, simply copying the input data into memory—input data that exceeds the allocated size simply overflows, over-writing whatever was in the memory. This means that attackers can cause program crashes (by causing the function return to redirect to some random address), or hijack the program (and then perform some nefarious actions by injecting their own code). In fact, the memory compromise might only be the starting point of a multi-vector attack, where other flaws may be exploited to circumvent security mechanisms. The specific case illustrated here is trivial, but many variations of this sort of attack mechanism continue to exist "in the wild" [122].

Where do we start if we want to improve security? It might be useful to think in terms of the taxonomy discussed earlier: how is the flaw introduced, when is it introduced, and where is it located? Memory overflow flaws are inadvertent, stemming from an omission of boundary condition checking. It is a flaw that is introduced during software development, and might be located in the application, operating system, or other supporting utility programs. Understanding the *how*,

when, where of a flaw provides a good starting point for researchers and designers to improve security by flaw elimination or mitigation.

We might want to tackle potential overflows from the perspective of *when* the flaw is introduced, for example, during development of the application. One option is to mandate that designers use higher level languages with automatic memory management. Alternatively, we might mandate more frequent and thorough code reviews, or adoption of a standardised development guidelines [84]. But what if we are still uncertain about the assurance level of the software? We can turn to technical solutions, perhaps introducing new mechanisms for run-time monitoring [92] to instead *detect* if a violation occurs, and then perform some corrective action, instead of preventing the incursion outright. Each approach for improving security, be it in changing development principles, or deploying technical mechanisms, carries some element of cost, and therefore trade-off.

In single processor contexts, existing approaches often focus on execution of a single thread; in the case of overflows, we are interested to know how the control flow can be manipulated. Often, the focus is on software issues, with execution assumed to be on commodity architectures. Other issues that have been examined include the concept of privilege, where a single processor, which has control of the entire system (such as in a System on Chip context), might need to coordinate different concurrent behaviours safely, usually by some means of hardware-supported privilege level enforcement. As we will discuss in Section 2.2 of this chapter, classical exploits in the context of single processor systems, like buffer overflows, are well-studied in the literature, with different security mechanisms aiming to improve different parts of the system life-cycle.

#### An example emerging issue: Hardware Trojans

Research in the context of multiprocessor security is less mature, particularly as design environments evolve and embedded systems become more complex. Single processor embedded systems can obviously harbour the same risks and vulnerabilities of well-studied flaws such as memory overflows in vulnerable software, but the impact of a successful exploit can potentially have a greater scope once many other processors, memories, and peripherals all come into play. Insights from research in more traditional single processor contexts are useful, but also need to be considered alongside additional issues that are introduced in the design and use of multiprocessor systems. MPSoC design brings many of its own new emerging challenges, such as *hardware* Trojans, where a malicious IP block is included into a MPSoC

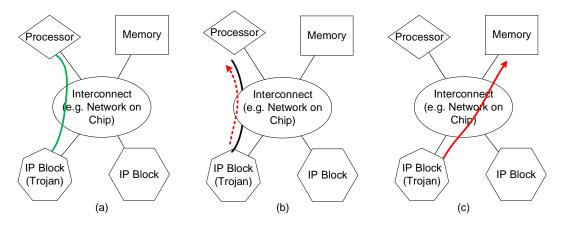

design, as shown in Figure 2.3. As design processes become more distributed and decentralised with design re-use strategies, malicious IP blocks that masquerade as legitimate and useful can be introduced into the supply chain.

Ordinarily, IP blocks are used to accelerate parts of an application, often operating at the request of a processor (Figure 2.3(a)). During system operation, a hardware Trojan can cause trouble in various ways after being activated (after some time, or after a specific trigger); it might start misbehaving, either denying service, or providing spurious data (Figure 2.3(b)), or surreptitiously try to retrieve or corrupt data from elsewhere in the system (Figure 2.3(c)).