# EFFICIENT BUILDING BLOCKS FOR HARDWARE NEURAL NETWORKS

#### ADEDAMOLA WURAOLA

DEPARTMENT OF ELECTRICAL, COMPUTER AND SOFTWARE ENGINEERING

THE UNIVERSITY OF AUCKLAND

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL,

COMPUTER AND SOFTWARE ENGINEERING IN PARTIAL FULFILMENT OF THE

REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

NOVEMBER 2020

# **Contents**

| Al | ostrac | e <b>t</b>                                                         | vi   |

|----|--------|--------------------------------------------------------------------|------|

| A  | cknow  | vledgement                                                         | vii  |

| A  | crony  | ms                                                                 | viii |

| Pι | ıblica | tions                                                              | ix   |

| Pa | itents |                                                                    | X    |

| Li | sts of | Figures                                                            | XV   |

| Li | sts of | Tables                                                             | xxi  |

| 1  | Intr   | oduction                                                           | 1    |

|    | 1.1    | Neural Network Building Blocks                                     | 1    |

|    |        | 1.1.1 Activation Function                                          | 2    |

|    |        | 1.1.2 Multiplication                                               | 3    |

|    |        | 1.1.3 Data Representation                                          | 4    |

|    | 1.2    | Motivation                                                         | 4    |

|    | 1.3    | The Proposed Square Law Solutions                                  | 5    |

|    | 1.4    | Research Contributions                                             | 5    |

|    | 1.5    | Thesis Outline                                                     | 8    |

| 2  | Squ    | uare Nonlinearity: A Computationally Efficient Activation Function | 10   |

|    | 2.1    | Introduction                                                       | 10   |

|    | 2.2    | Concepts                                                           | 12   |

|    | 2.3    | Analysis                                                           | 10   |

|   |       | 2.3.1    | Computational Footprint on Intel CPUs                   | 21 |

|---|-------|----------|---------------------------------------------------------|----|

|   |       | 2.3.2    | Computational Footprint on the ARM M3 Processor         | 23 |

|   |       | 2.3.3    | Decision Boundary and Activation Over Time              | 24 |

|   | 2.4   | Perform  | nance Comparison                                        | 25 |

|   |       | 2.4.1    | SQNL for Shallow Supervised Learning                    | 25 |

|   |       | 2.4.2    | Log_SQNL for Binary Logistic Regression                 | 32 |

|   |       | 2.4.3    | SQNL and Log_SQNL for Recurrent Neural Network          | 33 |

|   | 2.5   | Conclu   | sion                                                    | 34 |

| 3 | Effic | cient Ha | rdware Calculator for SQNL Function                     | 36 |

|   | 3.1   | Introdu  | action                                                  | 36 |

|   | 3.2   | Conce    | pts                                                     | 38 |

|   |       | 3.2.1    | Counter-based SQNL                                      | 39 |

|   |       | 3.2.2    | Multiplier-based SQNL                                   | 42 |

|   | 3.3   | Hardwa   | are Implementation                                      | 43 |

|   |       | 3.3.1    | Multi-clock/Counter Solution                            | 43 |

|   |       | 3.3.2    | Single-clock Solution                                   | 44 |

|   |       | 3.3.3    | Multiplier Solution                                     | 45 |

|   | 3.4   | Resour   | ce Utilisation                                          | 45 |

|   |       | 3.4.1    | Counter-based Implementation                            | 46 |

|   |       | 3.4.2    | Multiplier-based Implementation                         | 47 |

|   |       | 3.4.3    | Lookup Table-based Implementation                       | 47 |

|   |       | 3.4.4    | Single-clock Solution Implementation                    | 48 |

|   |       | 3.4.5    | Discussion                                              | 48 |

|   | 3.5   | Inferen  | ce Performance Accuracy                                 | 50 |

|   |       | 3.5.1    | Performance Accuracy on UCI datasets                    | 50 |

|   |       | 3.5.2    | Performance Accuracy on Experimental Rotational Dataset | 53 |

|   |       | 3.5.3    | Performance Accuracy on MNIST Dataset                   | 53 |

|   | 3.6   | Conclu   | sion                                                    | 54 |

| 4 | Asyı  | mmetric  | Square-based Activation Functions for Deep Learning     | 56 |

|   | 4.1   | Introdu  | action                                                  | 56 |

|   | 4.2   | Novel    | Activation Functions                                    | 58 |

|   |      | 4.2.1    | Smooth Square-based Asymmetric Activation Functions            | 59 |

|---|------|----------|----------------------------------------------------------------|----|

|   |      | 4.2.2    | Square-based Output Layer Activation Function                  | 62 |

|   | 4.3  | Analys   | is                                                             | 62 |

|   |      | 4.3.1    | Computational Footprint on Intel CPUs                          | 62 |

|   |      | 4.3.2    | Computational Footprint on the ARM M3 Processor                | 63 |

|   | 4.4  | Experi   | mental Results                                                 | 64 |

|   |      | 4.4.1    | Activation Over Time and Inference Time                        | 65 |

|   |      | 4.4.2    | Experiments using SQLU                                         | 66 |

|   |      | 4.4.3    | Experiments using Sqish for Very Deep Networks                 | 69 |

|   |      | 4.4.4    | Experiments using SqREU                                        | 70 |

|   |      | 4.4.5    | Experiments using SQ_Softplus for Restricted Boltzmann Machine | 70 |

|   |      | 4.4.6    | Experiments using SQMAX                                        | 71 |

|   | 4.5  | Conclu   | sion                                                           | 72 |

| 5 | Resc | ource Ef | ficient Asymmetric Activation Functions Generator              | 73 |

|   | 5.1  | Introdu  | ction                                                          | 73 |

|   | 5.2  | Concep   | ots                                                            | 76 |

|   | 5.3  | Analys   | is                                                             | 79 |

|   |      | 5.3.1    | Computational Footprint on Embedded NIOS II Processor          | 79 |

|   |      | 5.3.2    | Resource Footprint: Arithmetic Logic Unit Implementation       | 80 |

|   | 5.4  | Hardwa   | are Implementation                                             | 81 |

|   | 5.5  | Results  | and Discussion                                                 | 82 |

|   |      | 5.5.1    | Resource Utilisation of Asymmetric Function Generator          | 83 |

|   |      | 5.5.2    | Resource Utilisation of SQ-GEN                                 | 84 |

|   | 5.6  | Conclu   | sion                                                           | 85 |

| 6 | Con  | putatio  | nally Efficient Radial Basis Function                          | 86 |

|   | 6.1  | Introdu  | ction                                                          | 87 |

|   | 6.2  | RBF N    | Networks and RBF Kernels                                       | 88 |

|   | 6.3  | Nonlin   | ear Support Vector Machine and RBF Kernels                     | 89 |

|   | 6.4  | Novel    | Square Nonlinear Radial Basis Function (SQ-RBF)                | 90 |

|   | 6.5  | Merce    | r's Theorem Proof for SQ-RBF Kernel                            | 91 |

|   | 6.6  | Hardy    | ara Implementation of Square based Gaussian PRF                | 02 |

|   | 6.7  | Software Experimental Results                                           | 93  |

|---|------|-------------------------------------------------------------------------|-----|

|   |      | 6.7.1 SQ-RBF on RBFNN Problems                                          | 93  |

|   |      | 6.7.2 SQ-RBF Kernel on SVM Classification Problems                      | 98  |

|   | 6.8  | Hardware Experimental Results and Discussion                            | 98  |

|   | 6.9  | Conclusion                                                              | 100 |

| 7 | Reso | ource Efficient Implementation of Machine Learning Models               | 101 |

|   | 7.1  | Introduction                                                            | 102 |

|   |      | 7.1.1 Recurrent Neural Networks                                         | 102 |

|   |      | 7.1.2 Feed Forward Neural Networks                                      | 104 |

|   | 7.2  | Concepts                                                                | 106 |

|   |      | 7.2.1 Gated Activation                                                  | 106 |

|   |      | 7.2.2 Quantised Scaling Unit (QSU)                                      | 112 |

|   | 7.3  | Hardware Implementation                                                 | 114 |

|   |      | 7.3.1 Hardware Implementation of Gated Activation                       | 115 |

|   |      | 7.3.2 Hardware Implementation of QSU                                    | 116 |

|   | 7.4  | Experimental Results                                                    | 116 |

|   |      | 7.4.1 LSTM Software Experimental Results                                | 117 |

|   |      | 7.4.2 GRU Software Experimental Results                                 | 119 |

|   |      | 7.4.3 FNN Software Experimental Results                                 | 119 |

|   |      | 7.4.4 Resource Utilisation of QSU and Standard Multiplier               | 120 |

|   |      | 7.4.5 LSTM Hardware Experimental Results and Discussion                 | 120 |

|   |      | 7.4.6 GRU Hardware Experimental Results and Discussion                  | 123 |

|   |      | 7.4.7 FNN Hardware Experimental Results and Discussion                  | 123 |

|   | 7.5  | Conclusion                                                              | 124 |

| 8 | Eval | lluation of Learnable Asymmetric Activation Functions for Deep Learning | 125 |

|   | 8.1  | Introduction                                                            | 126 |

|   | 8.2  | Related Work                                                            | 127 |

|   |      | 8.2.1 Single Learnable Functions                                        | 127 |

|   |      | 8.2.2 Multiple Learnable Functions                                      | 127 |

|   |      | 8.2.3 Others                                                            | 128 |

|   | 8 3  | Parametric Square-based Asymmetric Activation Functions                 | 129 |

| Bi | hlingi | raphy 1                    | 42 |

|----|--------|----------------------------|----|

|    | 9.2    | Future Work                | 41 |

|    | 9.1    | Conclusions                | 39 |

| 9  | Con    | clusions and Future Work 1 | 39 |

|    | 8.6    | Conclusion                 | 38 |

|    |        | 8.5.3 SVHN                 | 35 |

|    |        | 8.5.2 CIFAR-100            | 35 |

|    |        | 8.5.1 CIFAR-10             | 33 |

|    | 8.5    | Experiments                | 31 |

|    | 8.4    | Multiple Square Units      | 30 |

## **Abstract**

The field of artificial intelligence and its paradigms continue to achieve state-of-the-art accuracy in various tasks. The future of artificial intelligence-based solutions will be populated with smart devices that require low computational power and inexpensive hardware platforms. Typically, the machine learning algorithms are complex, iterative, time-consuming, and hence are usually executed on general-purpose or high-performance computers. The computational engine for inferencing is significantly less complex than machine learning algorithms. While standard computers can incorporate sophisticated floatingpoint units (FPU), this is not the case with embedded processors that may host a simplified FPU. On dedicated inference engines, FPUs may not be possible due to cost (space, power, and speed). To solve this problem, we focus on efficient algorithms for various building blocks of neural networks. Our approach starts by introducing the square law that significantly reduces the computation requirements of machine learning models by eliminating the need for mathematical operators such as exponent, floatingpoint division, square root, and logarithm. The square law algorithm can reduce computation time on CPU by 1.3x to 4.3x and on ARM processors by 4x to 169x without hurting the prediction accuracy. We also discovered that square law can be applied across a wide variety of machine learning building blocks. We propose distinct technologies to make a complete neural network on a chip. The square law-based solutions use standard digital building blocks and can be implemented on ASICs or FPGAs. On ASIC platform, our algorithm records area efficiency (throughput per gate) of 1.79x to 3.75x over baselines without hurting the prediction accuracy.

# Acknowledgement

The biggest gratitude to my supervisor for not only being a supervisor but a mentor, thank you for believing in me, enduring all my naivety, and making me a better researcher. Your time and guidance have been indispensable to my graduate career, and your imagination is truly inspiring. Thank you for exposing me to everything - grant writing, supervision, and patents.

I would like to acknowledge the financial support received from the Faculty of Engineering, the University of Auckland in the form of the Faculty of Engineering Doctoral Scholarship Award.

I would like to express my deepest gratitude and special thanks to Harry She and Emily Melhuish at Halter for giving me the opportunity to explore during my internship within the company. For me, it was a unique experience to be at Halter and to do the research on data engineering.

Thank you to the numerous anonymous reviewers of my articles that provided valuable feedback and broke me until there was nothing left to break.

Thank you to the following groups of people and organisations who helped make my doctoral education more rounded by giving me opportunities outside the scope of my main degree, including those at the Center for Innovation and Entrepreneurship, UniServices, Nokia, The University of Auckland Human Participants Ethics Committee (UAHPEC), and the Postgraduate Students Association.

I thank my family for all the encouragement, prayer, and love through which they kept me going. I thank my parents for their motivation, support, and example, who often reminded me that God is always in control. Thank you Lola, Lolade, and Ife for being the best siblings anyone can ask for. Thank you to Busayo and Lamide.

Words are not enough to say how grateful I am to Matt, thank you for always listening to my rants and supporting me throughout this journey, I only can wish to be half as caring and loving as you.

To the friends I made and lost during these last few years, I say thank you, you each played an important role physically and emotionally.

Finally, I thank my great God and Saviour, Jesus Christ, without whom none of this would have been possible.

# **Acronyms**

ALM Adaptive Logic Module

ALU Arithmetic Logic Unit

ANN Artificial Neural Network

ASIC Application Specific Integrated Circuit

CNN Convolution Neural Network

CORDIC Coordinate Rotation Digital Computer

CPU Central Processing Unit

DNN Deep Neural Network

DSP Digital Signal Processor

FF Flip Flops

FPGA Field Programmable Gate Array

GEMM General Matrix Multiply

GPU Graphical Processing Unit

LSTM Long Short Term Memory

LUT LookUp Table

MLP Multilayer Perceptron

RBF Radial Basis Function

RNN Recurrent Neural Network

SLFNN Single Layer Feed-Forward Neural Network

SQLU Square Linear Units

SQNL Square Nonlinearity

SVM Support Vector Machine

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

# **Publications**

- 1. Wuraola, A., Patel, N., & Nguang, S.K., Efficient Activation Functions for Embedded Inference Engines (2021), *Elsevier Neurocomputing*, vol. 442, pp 73-88.

- 2. Wuraola, A., & Patel, N., SQNL: A new computationally efficient activation function (2018), Proceedings of the *IEEE International Joint Conference on Neural Networks (IJCNN)*.

- 3. Wuraola, A., & Patel, N., Computationally Efficient Radial Basis Function (2018), In *International Conference on Neural Information Processing*. Springer, Cham.

- 4. Wuraola, A., & Patel, N., Stochasticity-Assisted Training in Artificial Neural Network (2018), In *International Conference on Neural Information Processing*. Springer, Cham.

- 5. Wuraola, A., Patel, N., & Nguang, S.K., Resource Efficient Activation Functions for Neural Network Accelerator, *Elsevier Neural Networks* (Under Review).

# **Patent**

Patel, N., Wuraola, A. inventors; Nokia, Inc, assignee. Activation Function Implementation. United Kingdom Patent Application No. GB2007934.9, 2020, January 3.

# **List of Figures**

| 1.1  | Different Variant of RELU with Increasing Computational Complexity.(LReLU [1],                      |    |

|------|-----------------------------------------------------------------------------------------------------|----|

|      | APLU [2],ELU [3], GELU [4], SELU [5], dSiLU [6], ELISH [7], SRS [8]). Square                        |    |

|      | Law is the algorithm proposed in this thesis for simple symmetric and asymmetric acti-              |    |

|      | vation functions                                                                                    | 3  |

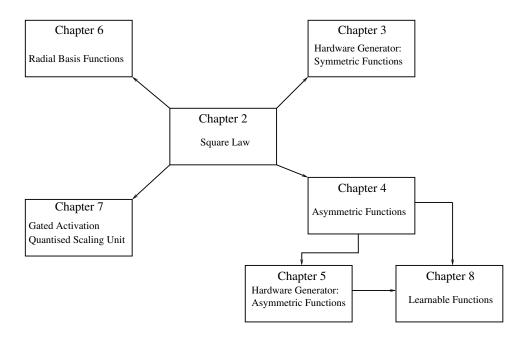

| 1.2  | Thesis Outline                                                                                      | 6  |

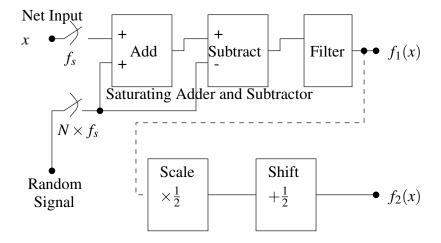

| 2.1  | Potential ASIC Implementation Block Schematic of Proposed Nonlinear Activation Func-                |    |

|      | tion                                                                                                | 13 |

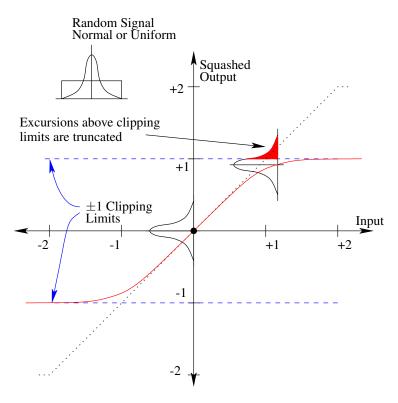

| 2.2  | Pictorial Description of Transfer Characteristics of the Proposed Method                            | 14 |

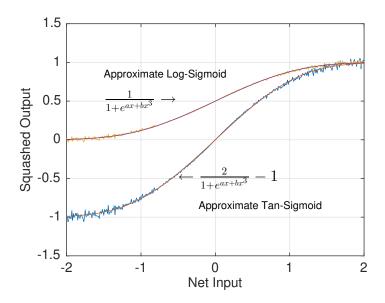

| 2.3  | Simulated Activation Functions Showing Approximate TanSig and LogSig Behaviour.                     |    |

|      | The traces with the jitter are the outputs of the simulated activation function while the           |    |

|      | solid trace is a plot of Equation 2.1 with the fitted parameters                                    | 14 |

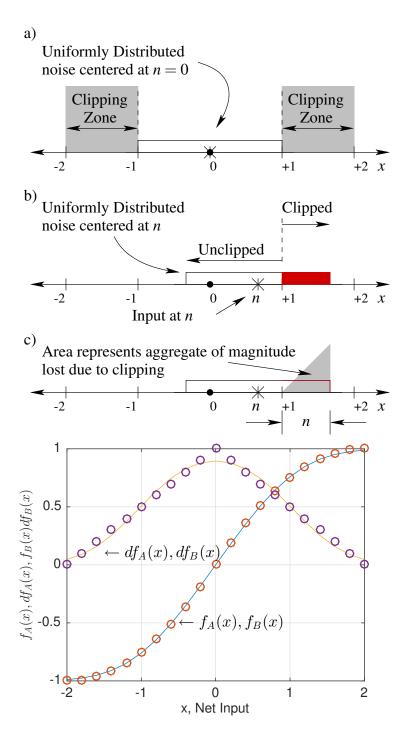

| 2.4  | Top - Pictorial Analysis of Nonlinear Action. Bottom - Comparison of fitted model and               |    |

|      | closed form model                                                                                   | 16 |

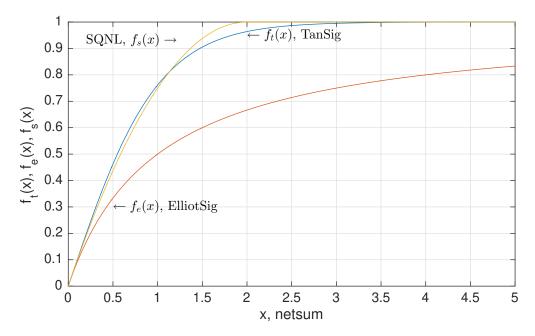

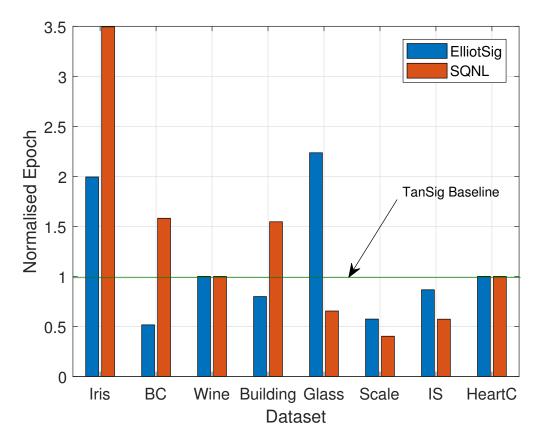

| 2.5  | Forward mappings - TanSig $(f_t(x))$ , ElliotSig $(f_e(x))$ , and Proposed SQNL Function $(f_s(x))$ | 20 |

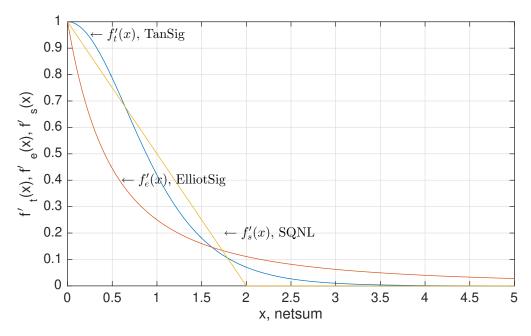

| 2.6  | Derivative mappings - TanSig $(f'_t(x))$ , ElliotSig $(f'_s(x))$ , and Proposed SQNL Function       |    |

|      | $(f_s'(x))$                                                                                         | 20 |

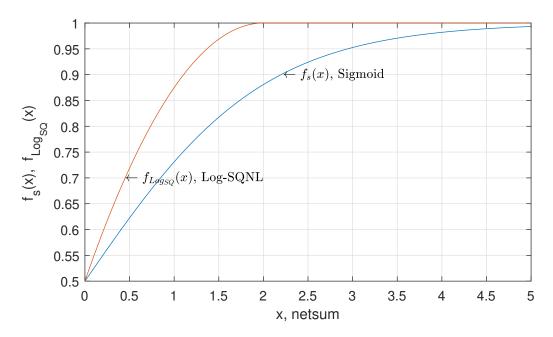

| 2.7  | Forward mappings - Sigmoid $(f_s(x))$ and Proposed Log_SQNL Function $(f_{LogSQ}(x))$               | 21 |

| 2.8  | Derivative mappings - Sigmoid $(f_s'(x))$ and Proposed Log_SQNL Function $(f_{LogSQ}'(x))$          | 21 |

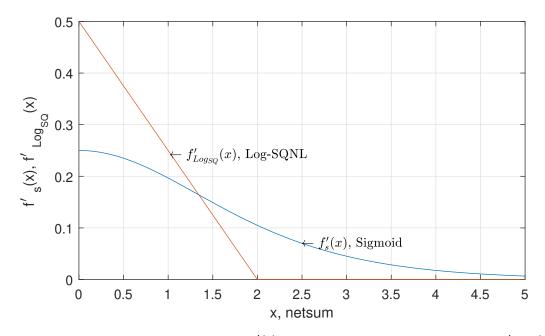

| 2.9  | a) Toy dataset: TanSig decision boundary b) Toy dataset: SQNL decision boundary                     |    |

|      | c) MNIST dataset: TanSig hidden layer activations during training d) MNIST dataset:                 |    |

|      | SQNL hidden layer activations during training e) MNIST dataset: TanSig histogram                    |    |

|      | distribution of activations f) MNIST dataset: SQNL histogram distribution of activations.           | 24 |

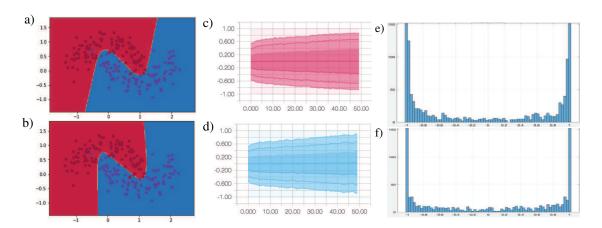

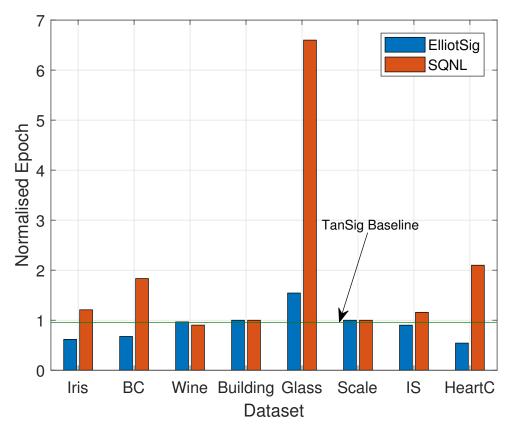

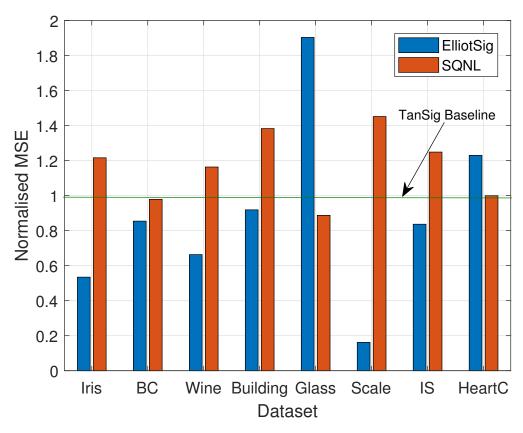

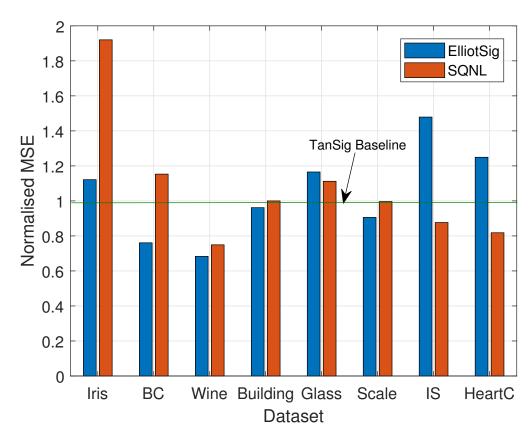

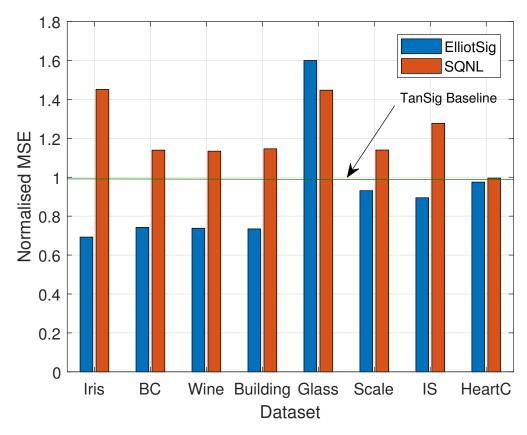

| 2.10 | Results of Experiment 1 For Traditional Backpropagation - BC:Breast Cancer, IS: Iono-               |    |

|      | sphere                                                                                              | 27 |

| 2.11 | Results of Experiment 1 For Levenberg Macquardt Backpropagation - BC. Breast Can-                                         |    |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

|      | cer, IS: Ionosphere                                                                                                       | 27 |

| 2.12 | Results of Experiment 1 For Resilient Backpropagation - BC:Breast Cancer, IS: Ionosphere                                  | 28 |

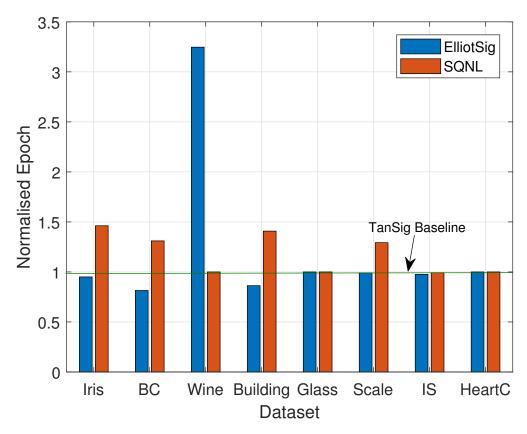

| 2.13 | Results of Experiment 2 For Traditional Backpropagation - BC:Breast Cancer, IS: Iono-                                     |    |

|      | sphere                                                                                                                    | 28 |

| 2.14 | Results of Experiment 2 For Levenberg Macquardt Backpropagation - BC:Breast Can-                                          |    |

|      | cer, IS: Ionosphere                                                                                                       | 29 |

| 2.15 | Results of Experiment 2 For Resilient Backpropagation - BC:Breast Cancer, IS: Ionosphere                                  | 29 |

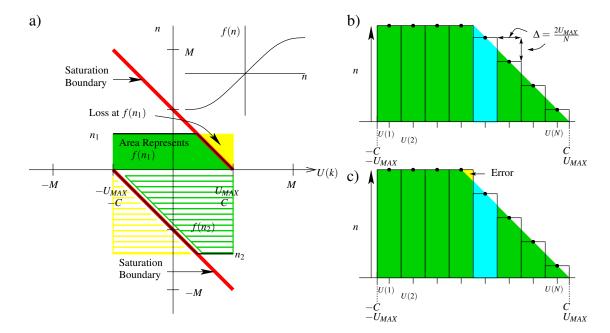

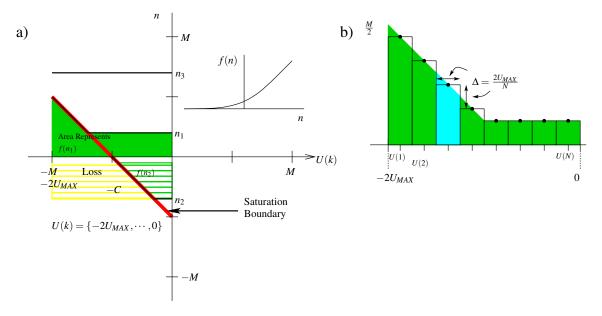

| 3.1  | SQNL - A Symmetric Activation Function. a) The conceptual impact of Equation 3.1 is                                       |    |

|      | shown for symmetric activation function realization. $U(k)$ is plotted on the x-axis and $n$ ,                            |    |

|      | the netsum, along the y-axis. The area enclosed in green represents the output mapping                                    |    |

|      | $f(n_1)$ . The inset shows the form of the mapping for $-M \le n < M$ b) When $n = \pm i \times \Delta$                   |    |

|      | i.e. midway between any two contiguous $U(k)$ , the $f(n)$ mapping is exact. c) When                                      |    |

|      | $n = \pm (\frac{\Delta}{2} + i \times \Delta)$ i.e. exactly equal to any element of $U(k)$ , the deviation from the ideal |    |

|      | is a maximum                                                                                                              | 40 |

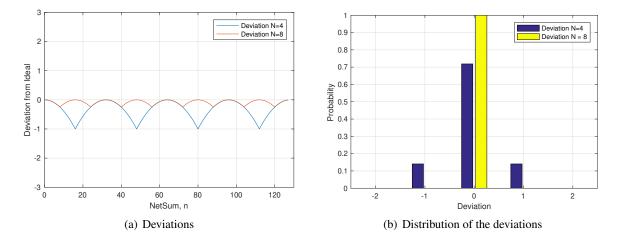

| 3.2  | Profile of deviation from ideal for $R=8$ when $N$ is reduced to 4 and 8. a) Plots the                                    |    |

|      | deviation for the positive input range for different values of $C$ . b) Plots the frequency                               |    |

|      | distribution of the deviation as a probablity                                                                             | 42 |

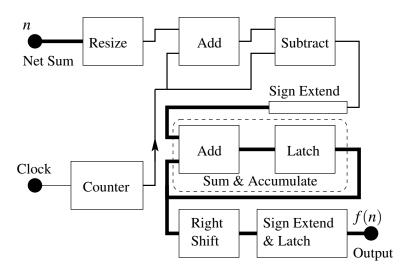

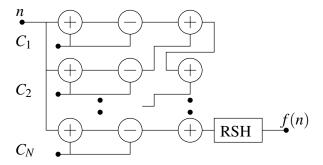

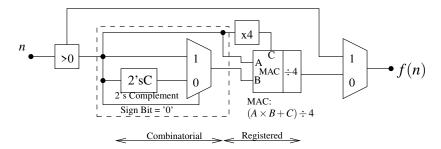

| 3.3  | Schematic of SQNL Activation Function using Multi-clock Methodology                                                       | 43 |

| 3.4  | Schematic of SQNL Activation Function using Single-clock Methodology. (RSH is                                             |    |

|      | Right Shift Operation)                                                                                                    | 44 |

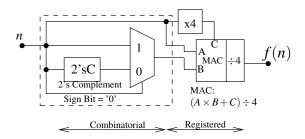

| 3.5  | Hardware Implementation of SQNL using the custom multiplier (special square opera-                                        |    |

|      | tor). The $\div 4, \times 4$ operations are right and left shift operations respectively, hence, have                     |    |

|      | no impact on the computational or resource footprint                                                                      | 45 |

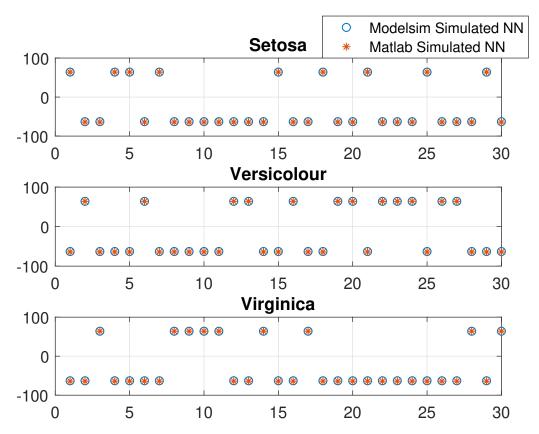

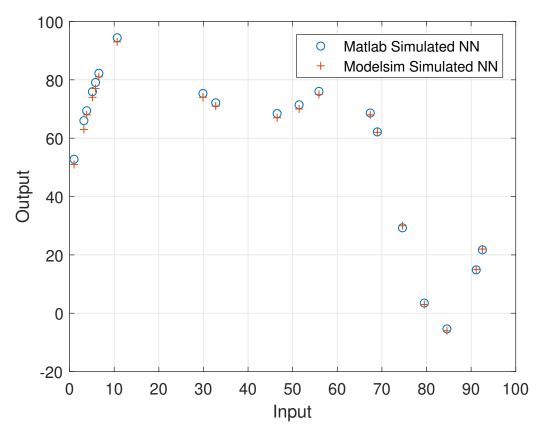

| 3.6  | Fisher's Iris Classification Dataset - Experimental Result (Modelsim code is synthesisable)                               | 51 |

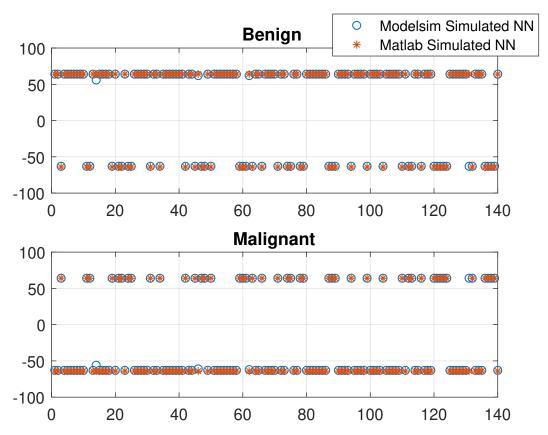

| 3.7  | Breast Cancer Classification Dataset - Experimental Result (Modelsim code is synthe-                                      |    |

|      | sisable)                                                                                                                  | 52 |

| 3.8  | Simple Fit Regression Dataset - Experimental Result (Modelsim code is synthesisable) .                                    | 52 |

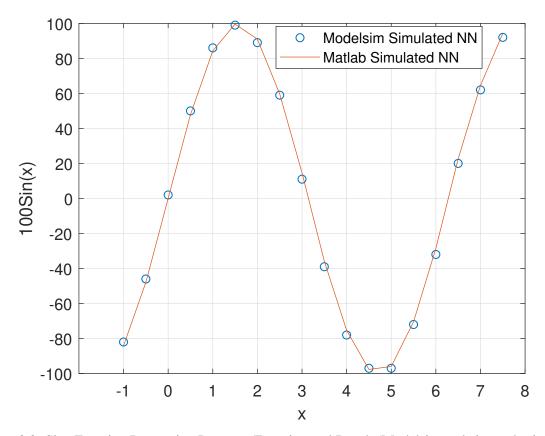

| 3.9  | Sine Function Regression Dataset - Experimental Result (Modelsim code is synthesisable)                                   | 53 |

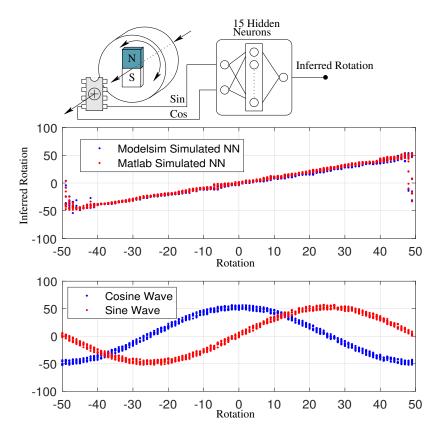

| 3.10 | Cosine Sine Function Regression Dataset - Experimental Result (Modelsim code is syn-                                      |    |

|      | thesisable)                                                                                                               | 54 |

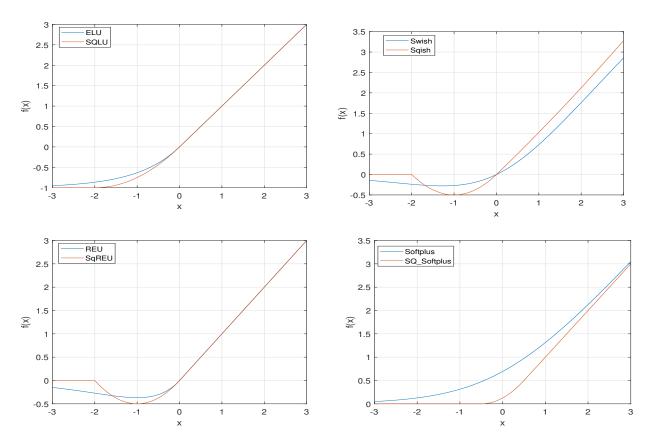

| 4.1 | Activation Functions: All the proposed square-based against their corresponding complex-            |    |

|-----|-----------------------------------------------------------------------------------------------------|----|

|     | based functions                                                                                     | 59 |

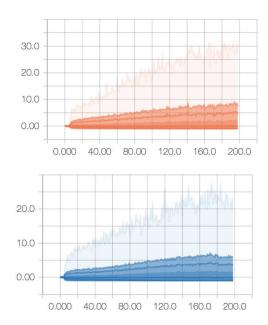

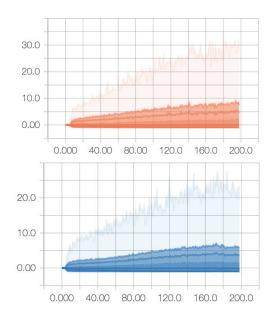

| 4.2 | Top: First hidden layer activations during training with ELU Function, Bottom: First                |    |

|     | hidden layer activations during training with SQLU Function                                         | 65 |

| 4.3 | Top: Last hidden layer activations during training with ELU Function, Bottom: Last                  |    |

|     | hidden layer activations during training with SQLU Function                                         | 66 |

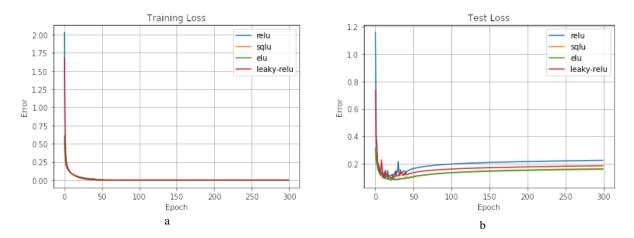

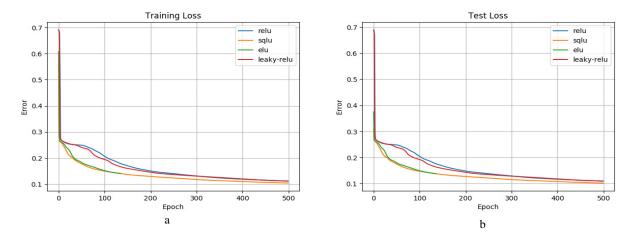

| 4.4 | SQLU networks evaluated on MNIST. a) Training set cross entropy loss for different                  |    |

|     | activation functions. b) Validation set cross entropy loss for different activation func-           |    |

|     | tions.(Best viewed in colour)                                                                       | 67 |

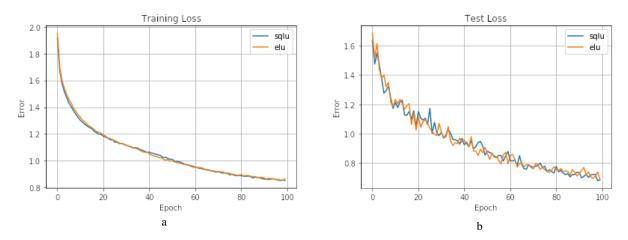

| 4.5 | SQLU and ELU networks evaluated on CIFAR10 with Data Augmentation to show that                      |    |

|     | SQLU is not inferior to ELU. a) Training set cross entropy loss for SQLU and ELU                    |    |

|     | functions. b) Validation set cross entropy loss for SQLU and ELU functions. (Best                   |    |

|     | viewed in colour)                                                                                   | 67 |

| 4.6 | Autoencoder training on MNIST: a) Training reconstruction error using different acti-               |    |

|     | vation functions. b) Test reconstruction error using different activation functions.(Best           |    |

|     | viewed in colour)                                                                                   | 68 |

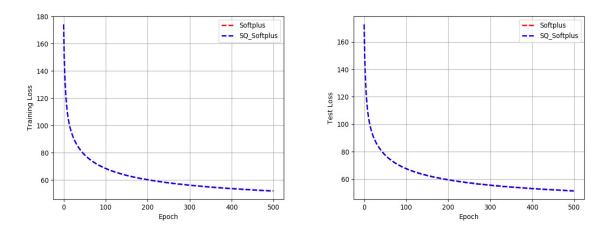

| 4.7 | Comparison of Conventional softplus and SQ_softplus: Left: Training loss, Right: Test               |    |

|     | error                                                                                               | 71 |

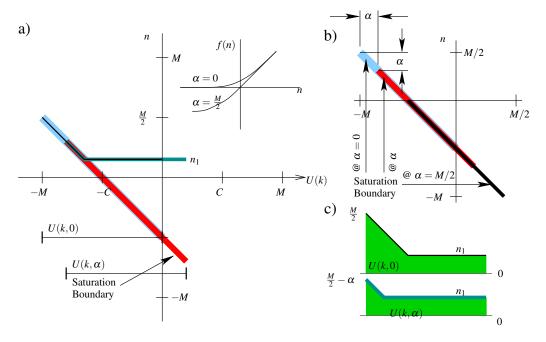

| 5.1 | An Asymmetric SQNL Activation Function                                                              | 76 |

| 5.2 | A Parameterised Asymmetric SQNL Activation Function                                                 | 78 |

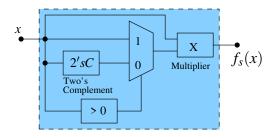

| 5.3 | Hardware Implementation of SQLU using the custom multiplier (special square opera-                  |    |

|     | tor). The $\div 4, \times 4$ operations are right shift operations and hence, have no impact on the |    |

|     | computational or resource footprint. Slight modification will result in other asymmetric            |    |

|     | functions                                                                                           | 80 |

| 5.4 | The implementation of a custom square operator $(f_s(n) = n \times - n )$ using a multiplier        | 81 |

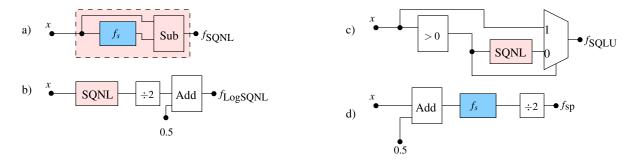

| 5.5 | SQNL family implementation schematics: a) SQNL using the custom multiplier $f_s(x) =$               |    |

|     | $x \times - x $ . b) Log_SQNL. c) SQLU d) SQ_Softplus. Note: The $\div 2$ and $\div 4$ operations   |    |

|     | are right shift operations and hence, have no impact on the computational or resource               |    |

|     | footprint                                                                                           | 81 |

| 5.6 | Schematics Asymmetric Activation Function Generator using multi-clock methodology.                  | 82 |

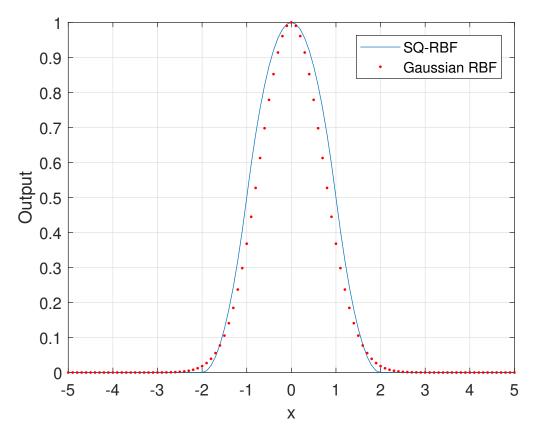

| 6.1 | The SO DRE and Gaussian DRE Karnels                                                                 | 01 |

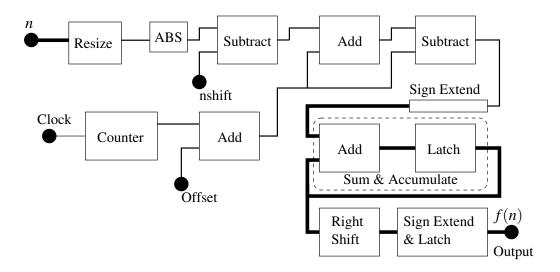

| 6.2  | Schematic of SQ-RBF Activation Function using Multi-clock Solution                                                  |

|------|---------------------------------------------------------------------------------------------------------------------|

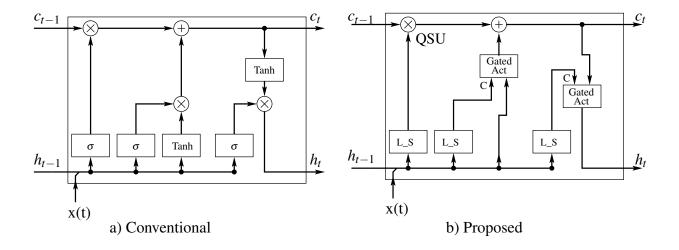

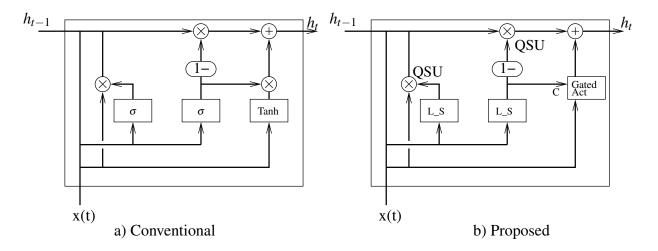

| 7.1  | Difference between conventional and proposed LSTM cell with the elimination of element-                             |

|      | wise multiplication. (QSU: Quantised Scaling Unit, L_S: Log_SQNL, Gated Act: Gated                                  |

|      | Activation)                                                                                                         |

| 7.2  | Difference between conventional and proposed GRU cell with the elimination of element-                              |

|      | wise multiplication. (QSU: Quantised Scaling Unit, L_S: Log_SQNL, Gated Act: Gated                                  |

|      | Activation)                                                                                                         |

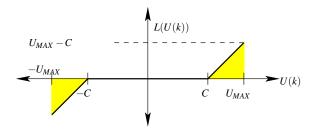

| 7.3  | Gated Activation: loss evaluated at $n = 0$                                                                         |

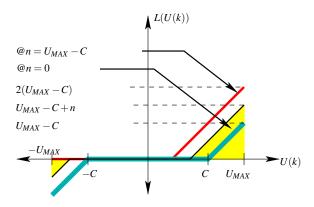

| 7.4  | Gated Activation: loss evaluated at $0 \le n \le U_{MAX} - C$                                                       |

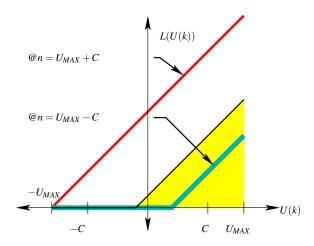

| 7.5  | Gated Activation: loss evaluated at $U_{MAX} - C \le n \le U_{MAX} + C$                                             |

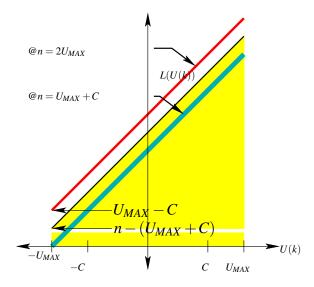

| 7.6  | Gated Activation: loss evaluated at $U_{MAX} + C \le n \le 2U_{MAX}$                                                |

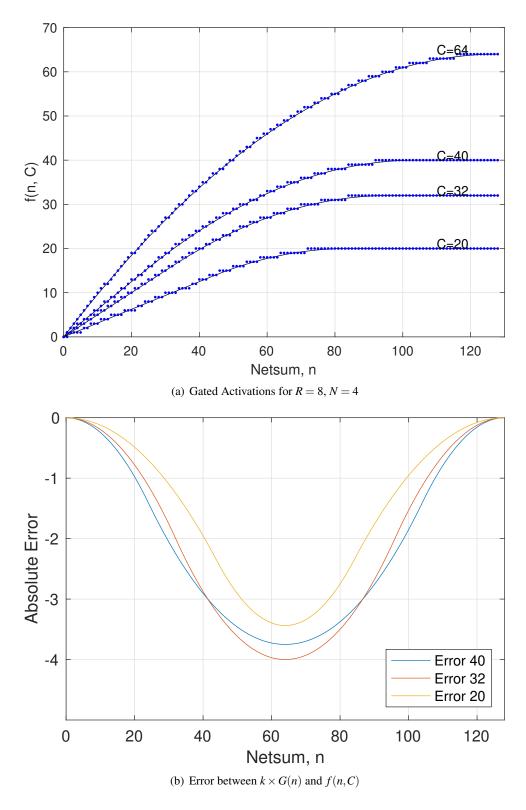

| 7.7  | a) Gated Activation, $R = 8$ , $N = 8$ : It shows that at a constant input, say netsum = 40 and                     |

|      | $C = 64$ , the output is $f(40,64) = 33.75$ . Thus, $f(40,40) = 24 \approx \frac{40}{64} \times f(40,64) = 21.09$ . |

|      | b) This shows the error varies with both $n$ and $C$ . The maximum error is always at                               |

|      | $n = 2^{R-2}$ , and $C = 2^{R-3}$ , With $R = 8$ , the maximum error is binary value of 4 111                       |

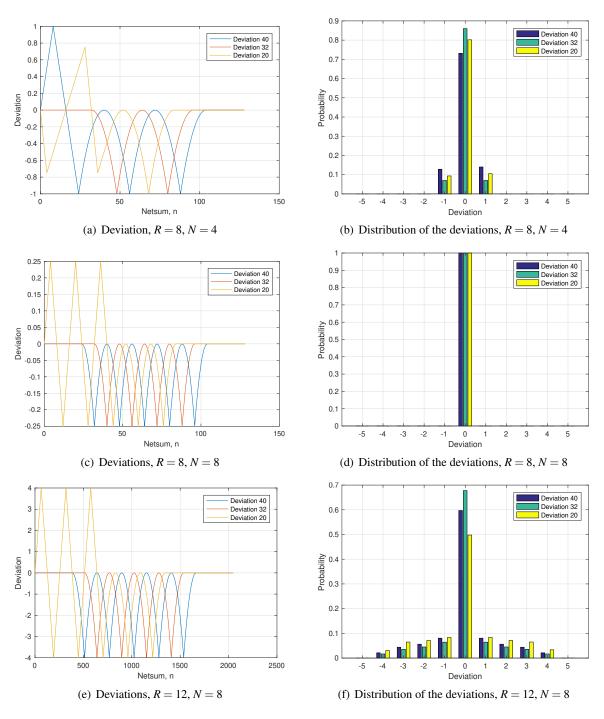

| 7.8  | Profile of deviation from ideal $f(n,C)$ a) Plots the deviation for the positive input range                        |

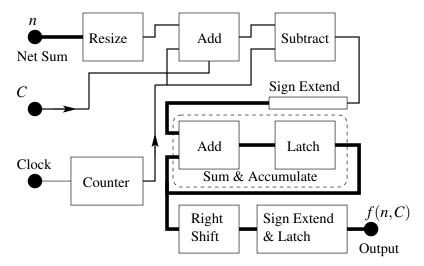

|      | for different values of C. b) Plots the frequency distribution of the deviation as a probablity. 113                |

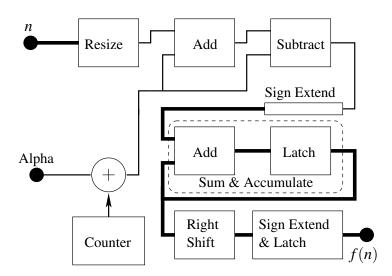

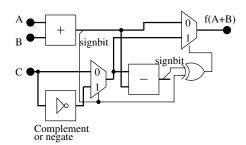

| 7.9  | Gated Activation Implementation                                                                                     |

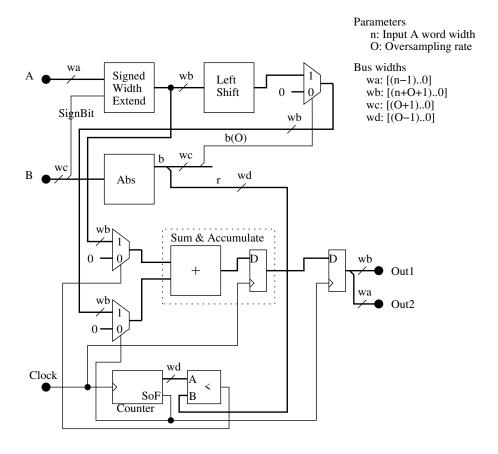

| 7.10 | Schematic of Quantised Scaling Unit Hardware Implementation                                                         |

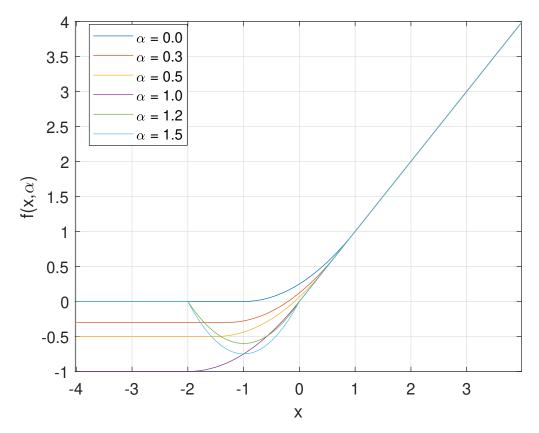

| 8.1  | A visualisation of Multiple Square Units, varying $\alpha$ . The closer $\alpha$ is to 0, the more it is            |

|      | like SQ_Softplus, $\alpha$ greater than 1, shows SqREU and $\alpha = 1.0$ is SQLU                                   |

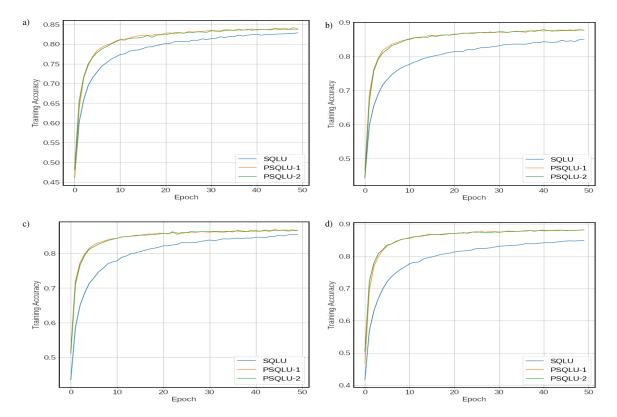

| 8.2  | CIFAR10: Convergence curves for training sets of fixed and learnable activation func-                               |

|      | tions on different WRN architectures. a) WRN-40-1 b) WRN-40-4 c) WRN-16-4 d)                                        |

|      | WRN-16-8. The parametric SQLU (PSQLU-1 and PSQLU-2) converges fastest than                                          |

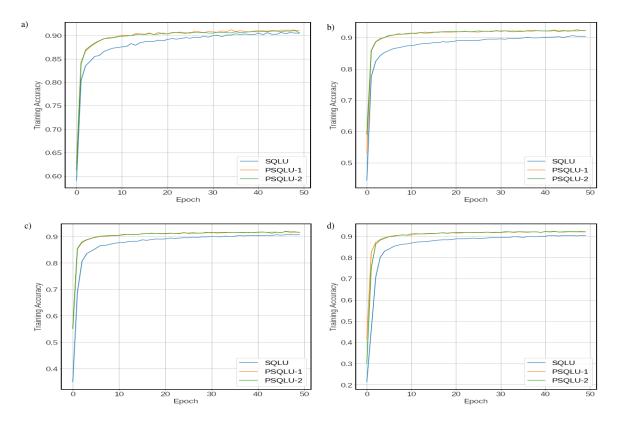

|      | the fixed SQLU activation function for all architecture depths and widths                                           |

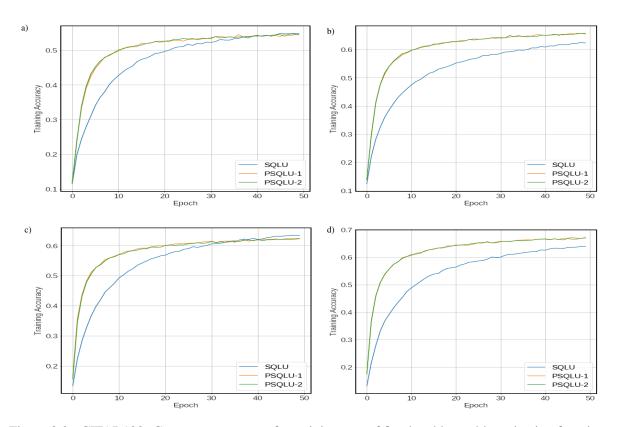

| 8.3  | CIFAR100: Convergence curves for training sets of fixed and learnable activation func-                              |

|      | tions on different WRN architectures. a) WRN-40-1 b) WRN-40-4 c) WRN-16-4 d)                                        |

|      | WRN-16-8. The parametric SQLU (PSQLU-1 and PSQLU-2) converges fastest than                                          |

|      | the fixed SQLU activation function for all architecture depths and widths                                           |

| 8.4 | SVHN: Convergence curves for training sets of fixed and learnable activation functions |

|-----|----------------------------------------------------------------------------------------|

|     | on different WRN architectures. a) WRN-40-1 b) WRN-40-4 c) WRN-16-4 d) WRN-            |

|     | 16-8. The parametric SQLU (PSQLU-1 and PSQLU-2) converges fastest than the fixed       |

|     | SQLU activation function for all architecture depths and widths                        |

# **List of Tables**

| 2.1  | CPU Performance of Commonly used Mathematics Function and the Activation Func-        |    |

|------|---------------------------------------------------------------------------------------|----|

|      | tions. EP: Enhanced Performance.                                                      | 22 |

| 2.2  | Speedups: CPU Performance of Symmetric Activation Functions. EP: Enhanced Per-        |    |

|      | formance                                                                              | 22 |

| 2.3  | Computational time of Tanh, ElliotSig, SQNL, and ISRU functions and their derivatives |    |

|      | using ARM M3 processor. This is an average of 1000 calculations                       | 23 |

| 2.4  | Speedups: Computational time of Tanh, SQNL, ElliotSig, ISRU function and their        |    |

|      | derivative using ARM M3 processor. This is an average of 1000 calculations            | 24 |

| 2.5  | Sensitivity and Specificity on Classification Dataset                                 | 31 |

| 2.6  | Accuracy and G-mean on Classification Dataset                                         | 31 |

| 2.7  | Convergence Speed On MNIST Dataset                                                    | 32 |

| 2.8  | Performance Accuracy of Sigmoid/LogSig Vs SQNL based Logistic Regression. A           |    |

|      | comparable result between Sigmoid and Log_SQNL is achieved                            | 33 |

| 2.9  | Performance Accuracy using square-based LSTM network. Changing the activation         |    |

|      | function to SQNL yielded about 3% for the Kaggle Model and 1% for the IMDB dataset    |    |

|      | improvement in performance accuracy. Use of Hardtanh and Hardsig performs worse       |    |

|      | than TanSig and sigmoid functions. (SQNL and log_SQNL to replace TanSig and sig-      |    |

|      | moid respectively)(Results are average of 5 runs, and an estimated mean of accuracy   |    |

|      | with the confidence of 95% is recorded)                                               | 34 |

| 2.10 | Performance Accuracy using square-based GRU network. (Results are average of 5        |    |

|      | runs, and an estimated mean of accuracy with the confidence of $95\%$ is recorded)    | 34 |

| 3.1  | Indicative Gate Usage                                                                 | 46 |

| 3.2  | Estimated Counter Based SQNL Gate Usage (GU) with Various <i>N</i>                    | 46 |

| 3.3 | Resource Offisation Summary of SQNL implementation using direct (D_SQNL) method,           |    |

|-----|--------------------------------------------------------------------------------------------|----|

|     | LUT (L_SQNL ) method and counter-based (C_SQNL )                                           | 48 |

| 3.4 | Resource utilisation of single-clock solution, LUT and multiplier-based solution           | 48 |

| 3.5 | Ratio of Gates Usage for Normalised Throughput                                             | 49 |

| 4.1 | Speedups: CPU Performance of asymmetric activation functions. Run on Intel Xeon            |    |

|     | with Vector Function Data.                                                                 | 63 |

| 4.2 | Computational time of ELU, SQLU, Softplus (Softp) and SQ_Softplus (SQ_Softp) ,             |    |

|     | SqREU, REU, Swish and Sqish functions and their derivatives using ARM M3 pro-              |    |

|     | cessor. This is an average of 1000 calculations.                                           | 64 |

| 4.3 | Speed ups: Computational time of asymmetric functions and their derivatives using          |    |

|     | ARM M3 processor. This is an average of 1000 calculations                                  | 64 |

| 4.4 | MNIST preliminary analysis showing: training time, inference time in seconds, and per-     |    |

|     | centage performance accuracy. Here SQLU consistently performs better than ELU.(Average     | ;  |

|     | of five runs)                                                                              | 65 |

| 4.5 | Performance Accuracy on CIFAR - 10 using ReLU, ELU and SQLU activation functions           |    |

|     | on already defined architecture. We used the ResNet20 (20 layer ResNet) Version 1          |    |

|     | [9]. The results show that SQLU is not inferior to ELU and hence, can replace ELU          |    |

|     | whenever the computational time and resource-efficient Inference block is essential. *     |    |

|     | ELU diverges. (Results are average of five runs, and an estimated mean of accuracy with    |    |

|     | the confidence of 95% is recorded).                                                        | 68 |

| 4.6 | Performance Accuracy on CIFAR - 100 using ReLU, ELU and SQLU activation func-              |    |

|     | tions on already defined architecture. We used the ResNet20 (20 layer ResNet) Version      |    |

|     | 2 [10]. * ELU diverges. (Results are average of five runs, and an estimated mean of        |    |

|     | accuracy with the confidence of 95% is recorded)                                           | 68 |

| 4.7 | Performance Accuracy on SVHN using ReLU, ELU and SQLU activation functions on              |    |

|     | already defined architecture. We used the Convnet ([11]). The results show that SQLU       |    |

|     | is not inferior to ELU and hence, can replace ELU whenever the computational time and      |    |

|     | resource-efficient Inference block is essential. (Results are average of five runs, and an |    |

|     | estimated mean of accuracy with the confidence of 95% is recorded)                         | 69 |

| 4.8  | Performance Accuracy on Tiny ImageNet using ReLU, ELU and SQLU activation func-              |    |

|------|----------------------------------------------------------------------------------------------|----|

|      | tions on already defined architecture. We used the DenseNet and model parameters             |    |

|      | defined in [12]. We use the ResNet50 (50 layer ResNet) [10] and model parameters             |    |

|      | defined in [13]                                                                              | 69 |

| 4.9  | Sqish: Performance Accuracy on CIFAR - 10 using activation functions on already de-          |    |

|      | fined architecture. The results show that Sqish is not inferior to swish and hence, can      |    |

|      | replace swish whenever the computational time and resource-efficient Inference block         |    |

|      | is essential. (Results are average of five runs, and an estimated mean of accuracy with      |    |

|      | the confidence of 95% is recorded).                                                          | 70 |

| 4.10 | Sqish: Performance Accuracy on CIFAR - 100 using activation functions on already             |    |

|      | defined architecture. The results show that Sqish is not inferior to swish and hence can     |    |

|      | replace swish whenever the computational time and resource-efficient Inference block         |    |

|      | is essential. (Results are average of 5 runs, and an estimated mean of accuracy with the     |    |

|      | confidence of 95% is recorded)                                                               | 70 |

| 4.11 | SqREU: Performance Accuracy on Fashion MNIST (FMNIST), CIFAR-10 and CIFAR-                   |    |

|      | 100 using activation functions on already defined architecture. The results show that        |    |

|      | SqREU is not inferior to REU and hence, can replace REU whenever the computational           |    |

|      | time and resource-efficient Inference block is essential. (Results are average of five runs, |    |

|      | and an estimated mean of accuracy with the confidence of 95% is recorded)                    | 70 |

| 4.12 | Performance Accuracy on SVHN CIFAR-10 and CIFAR-100 using softmax and SQ-                    |    |

|      | MAX as the output layer activation function. The hidden layer function is left as ReLU.      |    |

|      | We changed the flatten layer to the Global Averaging Pooling for the VGG-19 architec-        |    |

|      | ture. The results show that SQMAX is not inferior to Softmax and hence, can replace          |    |

|      | softmax whenever the computational time and resource-efficient inference block is es-        |    |

|      | sential                                                                                      | 71 |

| 4.13 |                                                                                              | 72 |

| 5.1  | The optimised values of different activation functions for hardware implementation (         |    |

|      |                                                                                              | 82 |

|      |                                                                                              |    |

| 5.2 | Resource utilisation of asymmetric activation function implementation using a custom     |    |

|-----|------------------------------------------------------------------------------------------|----|

|     | Booths Radix-4 multiplier (mult), multi-clock (counter, $N=8$ ), and LUT solution. As    |    |

|     | displayed the counter based method for the asymmetric activation function consistently   |    |

|     | outperform the multiplier solution on both ASIC and FPGA platforms. At a lower reso-     |    |

|     | lution, the LUT performs slightly better than the counter solution on FPGA but worse on  |    |

|     | ASIC when compared with the counter solution. The LUT on the other hand is only bet-     |    |

|     | ter for lower resolution and can not accommodate applications where higher resolution    |    |

|     | is required. The counter solution scales well across different resolutions               | 83 |

| 5.3 | The ratio of gates usage for normalised throughput. The counter-based solution per-      |    |

|     | forms better than the multiplier and LUT solutions both at a lower resolution and higher |    |

|     | resolution. At higher resolution, the counter-based solution achieves extremely high     |    |

|     | throughput when compared to the LUT                                                      | 84 |

| 5.4 | Resource Utilisation of SQNL,SQLU,SQ_Softplus Combination Implementation using           |    |

|     | custom implementation                                                                    | 84 |

| 6.1 | Common and Approximate RBF Kernels                                                       | 89 |

| 6.2 | Experiment 1: Performance Comparison on SinE Function. The best result is shown in       |    |

|     | bold                                                                                     | 94 |

| 6.3 | Experiment 2: Performance Comparison on SinE Function. The best result is shown in       |    |

|     | bold                                                                                     | 94 |

| 6.4 | Experiment 1: Performance Comparison on Nonlinear Dynamic System Identification.         |    |

|     | The best result is shown in bold                                                         | 95 |

| 6.5 | Experiment 2: Performance Comparison on Nonlinear Dynamic System Identification.         |    |

|     | The best result is shown in bold.                                                        | 96 |

| 6.6 | Experiment 1: Performance Comparison on Mackey-Glass Time Series Prediction. The         |    |

|     | best result is shown in bold                                                             | 96 |

| 6.7 | Experiment 2: Performance Comparison on Mackey-Glass Time Series Prediction. The         |    |

|     | best result is shown in bold                                                             | 97 |

| 6.8 | Experiment 1: Performance Comparison on Triangular Function Approximation. The           |    |

|     | best result is shown in bold                                                             | 97 |

| 6.9 | Experiment 2: Performance Comparison on Triangular Function Approximation. The           |    |

|     | hast result is shown in hold                                                             | 07 |

| 6.10 | Test Error and Training Time (in Seconds) of Gaussian Vs. SQ-RBF based SVM. The             |

|------|---------------------------------------------------------------------------------------------|

|      | best result is shown in bold                                                                |

| 6.11 | FPGA logic utilisation of the proposed designs in relation to previous works using vari-    |

|      | ous activation function block array configurations                                          |

| 6.12 | Resource Utilisation on SinE dataset                                                        |

| 7.1  | LSTM Equations for the Conventional and proposed method                                     |

| 7.2  | GRU Equations for the Conventional and proposed method                                      |

| 7.3  | Character-level perplexity on the US baby name dataset. There is no difference in per-      |

|      | plexity when using the baseline model and Gated Activation method (small is better) 117     |

| 7.4  | Word-level perplexity on the Penn Tree Bank dataset. Using Gated Activation shows a         |

|      | negligible increase in the perplexity on this task (small is better)                        |

| 7.5  | Word-level perplexity on the WikiText-2. Using Gated Activation shows a negligible          |

|      | increase in the perplexity on this task (small is better)                                   |

| 7.6  | Test error rate of LSTM on MNIST and Fashion MNIST. By eliminating the element-             |

|      | wise multiplication, there is a negligible performance degradation between conventional     |

|      | and proposed LSTM models validating the usability of our approach. (Results are aver-       |

|      | age of five runs, and an estimated mean of accuracy with confidence of 95% is recorded) 119 |

| 7.7  | Character-level Accuracy. There is no difference in accuracy when using the baseline        |

|      | model and Gated Activation method                                                           |

| 7.8  | Accuracy using floating point full precision and INT5 quantisation                          |

| 7.9  | Resource utilisation of QSU and Standard Booth's Multiplier ( for an 8-bit system: input    |

|      | A is 8 bits, input B is 6 bits)                                                             |

| 7.10 | Resource utilisation of LSTM cell                                                           |

| 7.11 | Resource utilisation of LSTM cell (Replacing DSP with Booth's Algorithm) 122                |

| 7.12 | Resource utilisation of GRU cell                                                            |

| 7.13 | Resource utilisation of GRU cell (Replacing DSP with Booth's Algorithm)                     |

| 7.14 | Resource utilisation of Quantised Neural network models with QSU and Booth multiplier 124   |

| 8.1  | Computation: Mathematical Operator of commonly used learnable activation functions.(        |

|      | LMA: Linear Mixed Activation, NGA: Nonlinear Gated Activation)                              |

| 8.2 | The structure of wide residual network topology [14] used in our experiments. Hy-           |       |

|-----|---------------------------------------------------------------------------------------------|-------|

|     | perparameter $k$ controls the width of the network and $d$ controls the depth. Groups of    |       |

|     | convolutions are shown in brackets. Number is how many blocks of layers are used in         |       |

|     | succession. $N = \frac{d-4}{6}$                                                             | . 132 |

| 8.3 | CIFAR-10: The performance accuracy for each activation/topology pair tested in our          |       |

|     | first experiment. Results are average of five runs, and an estimated mean of the perfor-    |       |

|     | mance accuracy is recorded. The best activation for each topology is shown in <b>bold</b> . |       |

|     | The parametric functions achieve higher accuracy, at very small margin, than their non-     |       |

|     | parametric baselines                                                                        | . 134 |

| 8.4 | CIFAR-100: The performance accuracy for each activation/topology pair tested in our         |       |

|     | first experiment. Results are average of five runs, and an estimated mean of the perfor-    |       |

|     | mance accuracy is recorded. The best activation for each topology is shown in <b>bold</b> . |       |

|     | The parametric functions achieve higher accuracy, at very small margin, than their non-     |       |

|     | parametric baselines                                                                        | . 135 |

| 8.5 | SVHN: The performance accuracy for each activation/topology pair tested in our first        |       |

|     | experiment. Results are average of five runs, and an estimated mean of the perfor-          |       |

|     | mance accuracy is recorded. The best activation for each topology is shown in <b>bold</b> . |       |

|     | The parametric functions achieve higher accuracy, at very small margin, than their non-     |       |

|     | narametric haselines                                                                        | 137   |

School of Graduate Studies

AskAuckland Central

Alfred Nathan House

The University of Auckland

Tel: +64 9 373 7599 ext 81321 Email: <a href="mailto:postgradinfo@auckland.ac.nz">postgradinfo@auckland.ac.nz</a>

This form is to accompany the submission of any PhD that contains published or unpublished co-authored work. Please include one copy of this form for each co-authored work. Completed forms should be included in all copies of your thesis submitted for examination and library deposit (including digital deposit), following your thesis Acknowledgements. Co-authored works may be included in a thesis if the candidate has written all or the majority of the text and had their contribution confirmed by all co-authors as not less than 65%.

| Please indicate the chapter/section/pages of this thesis that are extracted from a co-authored work and give the title and publication details or details of submission of the co-authored work. |                                                                                                                                                                                                                  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Chapter 2                                                                                                                                                                                        | Chapter 2                                                                                                                                                                                                        |  |  |  |

|                                                                                                                                                                                                  | Wuraola Adedamola, and Nitish Patel. "SQNL: A new computationally efficient activation function." 2018<br>International Joint Conference on Neural Networks (IJCNN). IEEE, 2018. DOI: 10.1109/IJCNN.2018.8489043 |  |  |  |

| Nature of contribution by PhD candidate                                                                                                                                                          | Il concentualization, experiments and analysis drafting the original paper                                                                                                                                       |  |  |  |

| Extent of contribution by PhD candidate (%) 90                                                                                                                                                   |                                                                                                                                                                                                                  |  |  |  |

#### **CO-AUTHORS**

| Name         | Nature of Contribution                                                                 |

|--------------|----------------------------------------------------------------------------------------|

| Nitish Patel | Main Supervisor: research advise , developing the work, proofreading of the manuscript |

|              |                                                                                        |

|              |                                                                                        |

|              |                                                                                        |

|              |                                                                                        |

|              |                                                                                        |

#### **Certification by Co-Authors**

- the above statement correctly reflects the nature and extent of the PhD candidate's contribution to this work, and the nature of the contribution of each of the co-authors; and

- that the candidate wrote all or the majority of the text.

| Name         | Signature | Date       |

|--------------|-----------|------------|

| Nitish Patel | With.     | 2020/10/28 |

|              |           |            |

|              |           |            |

|              |           |            |

|              |           |            |

|              |           |            |

School of Graduate Studies

AskAuckland Central

Alfred Nathan House

The University of Auckland

Tel: +64 9 373 7599 ext 81321 Email: postgradinfo@auckland.ac.nz

This form is to accompany the submission of any PhD that contains published or unpublished co-authored work. Please include one copy of this form for each co-authored work. Completed forms should be included in all copies of your thesis submitted for examination and library deposit (including digital deposit), following your thesis Acknowledgements. Co-authored works may be included in a thesis if the candidate has written all or the majority of the text and had their contribution confirmed by all co-authors as not less than 65%.

| •                                                                                                                | Please indicate the chapter/section/pages of this thesis that are extracted from a co-authored work and give the title and publication details or details of submission of the co-authored work. |  |  |  |

|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Chapter 6: sections 6.2,                                                                                         | Chapter 6: sections 6.2, 6.4, 6.7.1                                                                                                                                                              |  |  |  |

|                                                                                                                  | Wuraola, Adedamola, and Nitish Patel. "Computationally Efficient Radial Basis Function." International Conference on Neural Information Processing. Springer, Cham, 2018.                        |  |  |  |

| Nature of contribution by PhD candidate conceptualization, experiments and analysis, drafting the original paper |                                                                                                                                                                                                  |  |  |  |

| Extent of contribution by PhD candidate (%)                                                                      |                                                                                                                                                                                                  |  |  |  |

#### **CO-AUTHORS**

| Name         | Nature of Contribution                                           |

|--------------|------------------------------------------------------------------|

| Nitish Patel | Main Supervisor: research advise, proofreading of the manuscript |

|              |                                                                  |

|              |                                                                  |

|              |                                                                  |

|              |                                                                  |

|              |                                                                  |

#### **Certification by Co-Authors**

- the above statement correctly reflects the nature and extent of the PhD candidate's contribution to this work, and the nature of the contribution of each of the co-authors; and

- that the candidate wrote all or the majority of the text.

| Name         | Signature | Date       |

|--------------|-----------|------------|

| Nitish Patel | · ·       | 2020/10/28 |

|              |           |            |

|              |           |            |

|              |           |            |

|              |           |            |

|              |           |            |

**School of Graduate Studies**AskAuckland Central

Alfred Nathan House

The University of Auckland

Tel: +64 9 373 7599 ext 81321 Email: postgradinfo@auckland.ac.nz

This form is to accompany the submission of any PhD that contains published or unpublished co-authored work. Please include one copy of this form for each co-authored work. Completed forms should be included in all copies of your thesis submitted for examination and library deposit (including digital deposit), following your thesis Acknowledgements. Co-authored works may be included in a thesis if the candidate has written all or the majority of the text and had their contribution confirmed by all co-authors as not less than 65%.

| Please indicate the chapter/section/pages of this thesis that are extracted from a co-authored work and give the title and publication details or details of submission of the co-authored work. |                                                                                  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|

| Chapter 4: Sections 4.2, 4.3, 4.4                                                                                                                                                                |                                                                                  |  |  |

| "Efficient Activation Fun                                                                                                                                                                        | "Efficient Activation Functions for Embedded Inference Engines" (Neurocomputing) |  |  |

| Nature of contribution by PhD candidate                                                                                                                                                          | conceptualization, experiments and analysis drafting the original paper          |  |  |

| Extent of contribution by PhD candidate (%)                                                                                                                                                      | 90                                                                               |  |  |

#### **CO-AUTHORS**

| Name              | Nature of Contribution                                           |

|-------------------|------------------------------------------------------------------|

| Nitish Patel      | Main Supervisor: research advise, proofreading of the manuscript |

| Sing Kiong Nguang | Co-supervisor: advice and discussion                             |

|                   |                                                                  |

|                   |                                                                  |

|                   |                                                                  |

|                   |                                                                  |

#### **Certification by Co-Authors**

- the above statement correctly reflects the nature and extent of the PhD candidate's contribution to this work, and the nature of the contribution of each of the co-authors; and

- that the candidate wrote all or the majority of the text.

| Name              | Signature | Date       |

|-------------------|-----------|------------|

| Nitish Patel      | Visit .   | 2020/10/28 |

| Sing Kiong Nguang | Deceased  | 2020/10/28 |

|                   |           |            |

|                   |           |            |

|                   |           |            |

|                   |           |            |

**School of Graduate Studies**AskAuckland Central

Alfred Nathan House

The University of Auckland

Tel: +64 9 373 7599 ext 81321

Email: postgradinfo@auckland.ac.nz

This form is to accompany the submission of any PhD that contains published or unpublished co-authored work. Please include one copy of this form for each co-authored work. Completed forms should be included in all copies of your thesis submitted for examination and library deposit (including digital deposit), following your thesis Acknowledgements. Co-authored works may be included in a thesis if the candidate has written all or the majority of the text and had their contribution confirmed by all co-authors as not less than 65%.

| Please indicate the chapter/section/pages of this thesis that are extracted from a co-authored work and give the title and publication details or details of submission of the co-authored work. |                                                                         |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|

| Chapter 3 and 5 Sections 3.2, 3.3, 3.4, 5.2, 5.3, 5.4 and 5.5                                                                                                                                    |                                                                         |  |  |  |

| "Resource Efficient Activation Functions for Neural Network Accelerator" (Neural Networks)                                                                                                       |                                                                         |  |  |  |

| Nature of contribution by PhD candidate                                                                                                                                                          | conceptualization, experiments and analysis drafting the original paper |  |  |  |

| Extent of contribution by PhD candidate (%)                                                                                                                                                      | 90                                                                      |  |  |  |

#### **CO-AUTHORS**

| Name              | Nature of Contribution                                                              |  |

|-------------------|-------------------------------------------------------------------------------------|--|

| Nitish Patel      | Main Supervisor: research advise, conceptualization, proofreading of the manuscript |  |

| Sing Kiong Nguang | Co-supervisor: discussion and advise                                                |  |

|                   |                                                                                     |  |

|                   |                                                                                     |  |

|                   |                                                                                     |  |

|                   |                                                                                     |  |

#### **Certification by Co-Authors**

- the above statement correctly reflects the nature and extent of the PhD candidate's contribution to this work, and the nature of the contribution of each of the co-authors; and

- that the candidate wrote all or the majority of the text.

| Name              | Signature | Date       |

|-------------------|-----------|------------|

| Nitish Patel      | VIII.     | 2020/10/28 |

| Sing Kiong Nguang | Deceased  | 2020/10/28 |

|                   |           |            |

|                   |           |            |

|                   |           |            |

|                   |           |            |

### Chapter 1

### Introduction

The field of artificial intelligence and its paradigms continue to achieve state-of-the-art accuracy in image recognition [15], language processing [16], autonomous vehicle [17], and other domains [18]. One of the successes of artificial intelligence and its paradigms is due to the availability of high computing hardware platforms. There is a growing interest in underlying hardware platforms for computing neural network operations. Distributed computing infrastructure using several Central Processing Unit (CPU) cores [19] or the use of high-end power-hungry Graphical Processing Units (GPUs) [15] are the two major platforms. Other commonly used platforms of choice are the Field Programmable Gate Arrays (FPGAs) and Application Specific Integrated Circuits (ASICs). Hardware implementation of machine learning models exhibits several challenges due to finite hardware resources, memory constraints, power, and latency. Current neural network models are computationally expensive and memory intensive. The associated computational complexity is highly undesirable from a real-time operation and low power consumption perspective, leading to considerable problems for constrained computing platforms (e.g. mobile devices) that suffer from limitations such as low computational power, low memory capacity, short battery life, strict miniaturisation requirements, and in some cases, lack of necessary support for floating-point arithmetic [20]. Current research [21-23] in the hardware implementation of neural network results in custom hardware-based neural network accelerators surpassing general-purpose processors in terms of energy efficiency and throughput.

### 1.1 Neural Network Building Blocks

The current trend in neural networks empowered Internet of Things (IoT), autonomous vehicles, and embedded applications to result in advancements in hardware and embedded platforms. However, un-

like CPU and GPU, FPGAs and ASIC are resource and memory constrained. The two fundamental operations of any neural network architecture are the General Matrix Multiply (GEMM) and activation functions. The following are the commonly used elementary functions in the field of machine learning: multiplication (matrix multiplication, convolution, element-wise multiplication), exponentials, logarithms, adders, and floating-point division [22, 24]. The elementary functions can be implemented using lookup tables [21], direct computations such as polynomial power series evaluations [25], hybrid approaches [26], iterative approaches [27] and piecewise approximations [22, 28].

#### 1.1.1 Activation Function

At the heart of every machine learning architecture lies a linear transformation followed by an activation function f(). The nonlinear activation function is an important building block of any artificial neural network architecture. Activation functions lie at the core of machine learning architectures allowing them to learn arbitrarily complex mappings and perform complex tasks. Without the activation function, a neural network is a linear regression model. Over the years, activation functions have been shown to increase performance accuracy [3], make it possible to create deeper layers [29], speed up training [3] among others. Many neural network applications can benefit from accurate, scalable, and low-power calculation of nonlinear activation functions. Accurate lookup tables (LUTs) require very large real estate on ANN chips and floating-point engines consume a lot of power and take time to process.

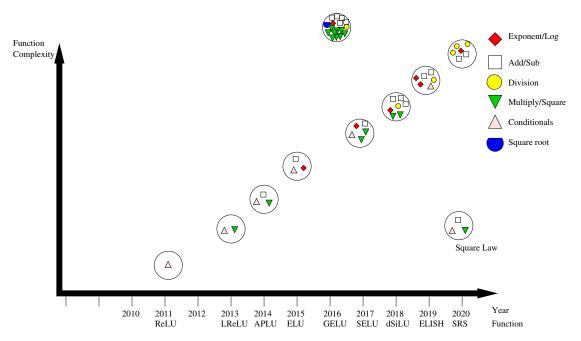

There are several types of machine learning models, each with their own characteristics and applications. Some activation functions are only useful in some machine learning models. For example, deep neural networks are characterised by using asymmetric non-saturating activation functions like ReLU and its variants. Long Short Term Memory (LSTM), a variant of recurrent neural networks, uses symmetric saturating activation functions for its gating mechanism. A normalising function, such as softmax, found use in multiclass classification problems. Sigmoid found use in generative adversarial networks, attention models, and binary classification problems. Sigmoid has significance in terms of its interpretability as probability; it is intuitive to use it for gating or binary classification problems [30]. The study of the optimal activation function is an active area of research. Over the years, researchers have proposed several activation functions to improve network performance (ability to train deeper layers, faster convergence, better accuracy, and others). There is a constant rise in the computational complexity in formulating these activation functions. Figure 1.1 shows the increasing complexity of some popular activation functions found in the literature for the last decade. Apart from the computationally simple ReLU, all other activation functions are expensive with increasing computation.

Figure 1.1: Different Variant of RELU with Increasing Computational Complexity.(LReLU [1], APLU [2], ELU [3], GELU [4], SELU [5], dSiLU [6], ELISH [7], SRS [8]). Square Law is the algorithm proposed in this thesis for simple symmetric and asymmetric activation functions.

#### 1.1.2 Multiplication

Multipliers are the most area and power-intensive arithmetic operators of the hardware implementation of any neural network architecture. The cost of a multiplier varies as the square of the precision for small width operands while the cost of adders and accumulators varies as a linear function of the precision [31]. As discussed in [32], multiplication and accumulation operations are directly related to the computation requirements of the neural network. Therefore, solving the high computation requirements of neural networks is equivalent to reducing the multiplication and accumulation operations. On software-based platforms, techniques such as pruning [33, 34] and compact architectural designs [35, 36] have been shown to reduce the multiplication requirements of network architecture. Furthermore, hardware and software platforms can benefit from the reduction of operands and operations precision, resulting in energy and power efficiency.

Reduction of weights and activations to binary [37] or ternary [20] results in the elimination of multiplications. Multiplications are replaced in binary and ternary networks with a shift operation, XNOR [38], and population count operation. On certain datasets and neural network models, reducing the precision of multipliers (which results in a reduction in area and power) does not affect the performance accuracy [24].

#### 1.1.3 Data Representation

Floating point, fixed point (full precision or quantised) are commonly used to represent neural network operation data. Data representation and precision for the neural network have a direct impact on memory, latency, and resource utilisation on software and hardware platforms. Quantisation [39] shifts values from floating-point continuous values to reduced bit discrete values (fixed-point). A 32-bit floating-point and integer multiplication consume 3.7pJ and 0.2pJ respectively on a 45nm ASIC technology [40]. A lot of work is being done on reducing the data precision during training and inferencing operation of machine learning applications.

The arithmetic operations of neural networks can be truncated down to an 8-bit fixed-point without significant deterioration in inference performance [41–44]. To make neural networks practical on embedded systems, many researchers have focused on training networks with quantised weights and activations. For example, weights may be constrained to take on integer, binary or ternary values, or maybe represented using low-precision (8 bits or less) fixed-point numbers. Extensive experiments performed in [45] show that lower precision (e.g., binary or ternary) requires a lot more training time/epoch to achieve the same accuracy level as higher bits such as 3-8 bits precision.

#### 1.2 Motivation

In recent years, Artificial Intelligence and its paradigms have seen a great spike in both academics and the commercial environment. Several existing software implementations of machine learning models provide high classification accuracy. However, these implementations cannot be used in embedded systems and applications because of the intensive computations required by the individual building blocks of machine learning architectures. In addition, embedded systems development requires meeting challenging constraints such as low cost, limited resources, and low power consumption. Devices that make use of machine learning paradigms are becoming more common. The use of machine learning involves a learning phase, an implementation engine, and an algorithm to match the problem. The implementation engine and inference engine could be a standard computer system or an embedded processor as in mobile phones. Processor chips in mobile phones are now equipped with an artificial neural network engine that can be configured to execute the outcome of a machine learning algorithm. Two important and integral parts of a machine learning implementation is the matrix multiplication and computation of a nonlinear function called the activation function. The GEMM operation is the most computational workload in deep learning. Several optimisations and parallelisation techniques have been introduced in the literature