# Towards a New Design and Execution Framework for SystemGALS

Ziming Xie

A thesis submitted in partial fulfilment of the requirements for the degree of Master of Engineering, The University of Auckland, 2022.

## Abstracts

Industry 4.0 depicts a vision of intelligent and agile production manufacturing processes that can achieve product customisation rapidly and economically. It encourages the manufacturing systems to comprise a group of interconnected and configurable subsystems rather than a unitary product line with fixed procedures. These agile production systems further require an agile design and deployment methodology that has dramatically facilitated the prosper of software applications. Different from traditional software development, the scope of industrial system design ranges from programming languages that focus on system-level behaviours to execution platforms and physical plant manufacturing. These form an extensive design exploration space for agile system development. This thesis starts with an example of an intelligent Sorter System and leverages SystemGALS, a system-level programming language, to design its control system. In addition, we employ Chipyard, an agile RISC-V SoC framework, to build two execution platforms for the control programs. The main contribution of our research can be summarised in three folds. The first one is to evaluate the pros and cons of current tools for industrial control system design by implementing a smart Sorter System. Secondly, we demonstrate a software and hardware co-design example in SystemGALS. The last one is to present a new potential execution framework for SystemGALS programs that will allow the design of hardware/software customised controllers, including both software/runtime systems and hardware parts of the final design.

## Acknowledgements

I would first like to express my special thanks to my supervisor, Professor Zoran Salcic. I have received a great deal of assistance and support from you. Your invaluable expertise and insight feedback help me sharpen my thoughts and lead me out of confusion.

I would also like to acknowledge Hamish Lonergan, my tutor in COMPSYS 704. He nicely organised the learning sources of RISC-V and generously provided them to us.

In addition, I would like to think my parents and my wife for their selfless support, especially during the Covid-19 pandemic. Their help makes it easy for me to get through those tough times.

## **Table of Contents**

| Abstractsii                                             |

|---------------------------------------------------------|

| Acknowledgementsiii                                     |

| List of Figures vii                                     |

| List of Tablesx                                         |

| Chapter 1. Introduction1                                |

| 1.1. The Vision of Industry 4.01                        |

| 1.2. System-Level Programming Language2                 |

| 1.3. Execution Architecture                             |

| 1.4. Agile Hardware Design4                             |

| 1.5. Thesis Contributions and Outline5                  |

| Chapter 2. Related Work & Background7                   |

| 2.1. SystemJ7                                           |

| 2.2. SystemGALS                                         |

| 2.3. RISC-V                                             |

| 2.4. Chisel/FIRRTL12                                    |

| 2.5. Chipyard                                           |

| 2.5.1 Components                                        |

| 2.5.2 Parameter System15                                |

| 2.5.3 Diplomacy                                         |

| 2.6. TDMA-MIN NoC                                       |

| Chapter 3. Motivating Example21                         |

| 3.1. Sorter System                                      |

| 3.2. Model of The System22                              |

| 3.3. SystemGALS Program Design                          |

| 3.3.1 Loader Controller                                 |

| 3.3.2 Conveyor Controller                               |

| 3.3.3 Arm Controller                                    |

| 3.4. Image Recognition Algorithm and C Implementation32 |

| 3.4.1 Algorithm Overview                             |    |

|------------------------------------------------------|----|

| 3.4.2 Binarization                                   |    |

| 3.4.3 Characteristic Vector Extraction               |    |

| 3.4.4 Item Recognition                               |    |

| Chapter 4. SystemGALS Execution                      |    |

| 4.1. Model of Time                                   |    |

| 4.2. Model of Execution                              | 40 |

| 4.3. Communication                                   | 42 |

| 4.4. Runtime Support System                          | 43 |

| Chapter 5. Mapping SystemGALS Programs to C Programs |    |

| 5.1. Schedule                                        | 44 |

| 5.2. Signal and CFV                                  | 45 |

| 5.3. Channel                                         | 47 |

| 5.4. Control Flow                                    | 51 |

| 5.4.1 Statements                                     | 51 |

| 5.4.2 Execution Logic                                | 51 |

| 5.5. Runtime Support System                          | 53 |

| Chapter 6. Single-core Execution Platform            | 55 |

| 6.1. Chipyard SoC Structure                          | 55 |

| 6.1.1 BaseSubsystem                                  | 55 |

| 6.1.2 ChipyardSubsystem                              | 56 |

| 6.1.3 ChipyardSystem                                 | 58 |

| 6.1.4 DigitalTop and ChipTop                         | 58 |

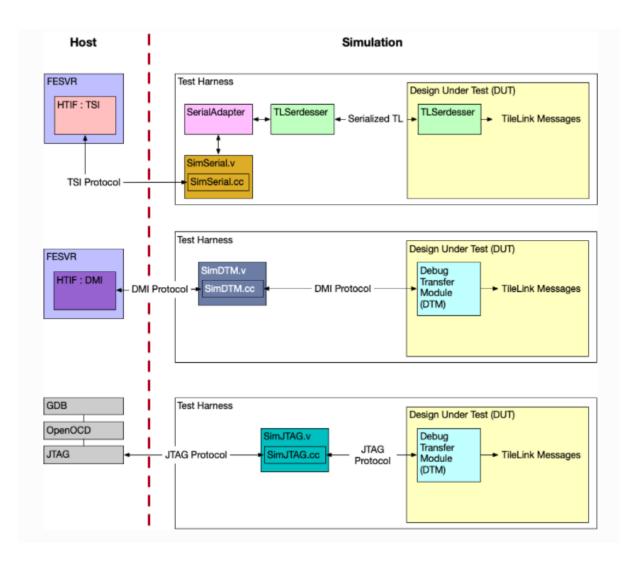

| 6.1.5 Testharness and Testdriver                     | 59 |

| 6.2. SoC Bring-up Method                             | 60 |

| 6.3. SoC Configuration                               | 62 |

| 6.3.1 Configuration Example                          | 62 |

| 6.3.2 Single-core Execution Platform Configuration   | 65 |

| 6.4. Simulator Building Process                      | 66 |

| Chapter 7. Multi-core Execution Platform             | 68 |

| 7.1. Architecture Overview                           | 68 |

| 7.2. 4-Port TDMA-MIN NoC and Network Interface       | 70 |

| 7.2.1 NoC Implementation                             | 71 |

| 7.2.2 Network Interface Implementation                           | 74  |

|------------------------------------------------------------------|-----|

| 7.3. Application-Specific Processors                             | 76  |

| 7.3.1 Characteristic Vector Extraction ASP Implementation        | 76  |

| 7.3.2 Item Recognition ASP Implementation                        | 81  |

| 7.4. DMA Device                                                  | 84  |

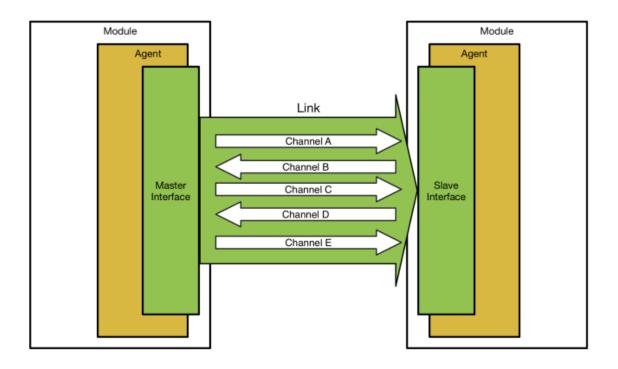

| 7.4.1 TileLink Overview                                          | 85  |

| 7.4.2 DMA Controller                                             | 87  |

| 7.4.3 DMA Reader                                                 | 89  |

| 7.4.4 DMA Writer                                                 | 92  |

| 7.5. System Integration                                          | 92  |

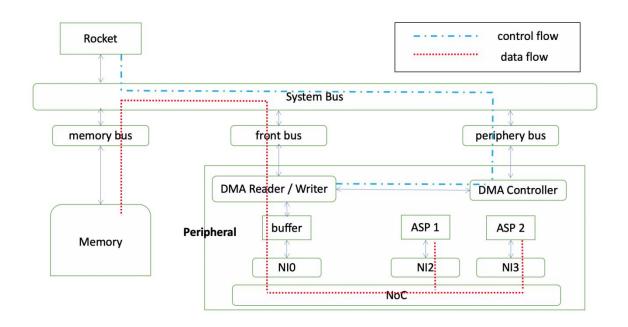

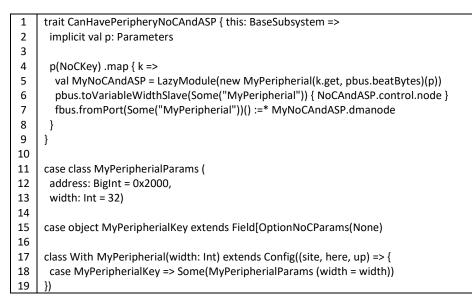

| 7.5.1 Peripheral Module                                          | 93  |

| 7.5.2 System Composition                                         | 94  |

| Chapter 8. Experiment & Results                                  | 96  |

| 8.1. Training                                                    |     |

| 8.1.1 Image Conversion                                           |     |

| 8.1.2 Neighbours Characteristic Vector                           |     |

| 8.2. Peripheral Software Interface                               |     |

| 8.3. Program Compilation                                         |     |

| 8.4. Boot Process                                                |     |

| 8.5. Experiment Result                                           |     |

| Chapter 9. Discussion and Future Work                            |     |

| 9.1. Evaluation                                                  | 102 |

| 9.1.1 SystemGALS Evaluation                                      |     |

| 9.1.2 Chipyard Evaluation                                        |     |

| 9.1.2 Chipyard Evaluation<br>9.2. SystemGALS Execution Framework |     |

|                                                                  |     |

| 9.3. Expectation                                                 |     |

| References                                                       |     |

## List of Figures

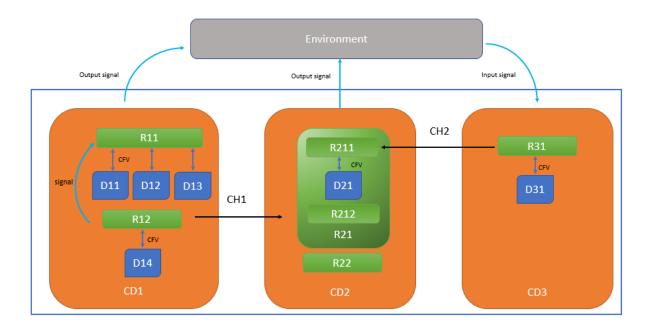

| Figure 2-1. An illustration of an example SystemGALS system. [29]                                                                                       | 11             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

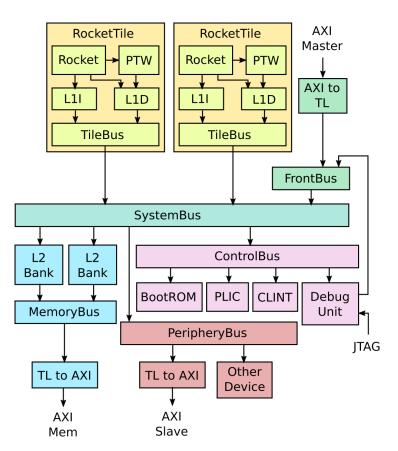

| Figure 2-2. Rocket chip generator components. [60]                                                                                                      | 14             |

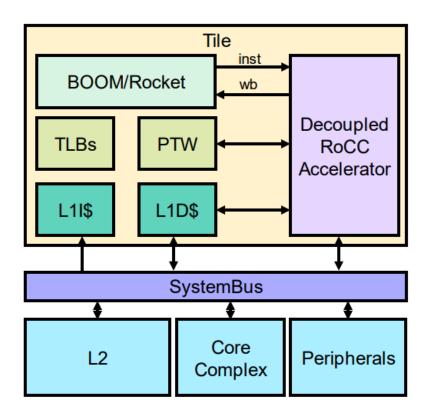

| Figure 2-3. RoCC accelerator connection. [60]                                                                                                           | 15             |

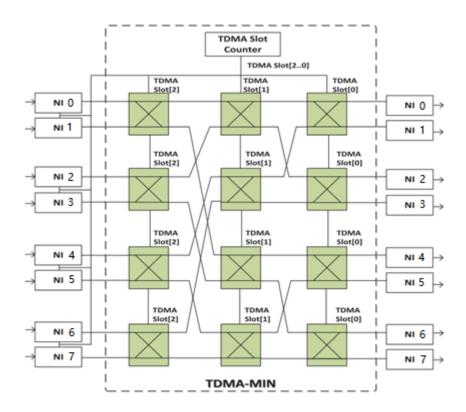

| Figure 2-4. 8-port TDMA-MIN NoC with Network Interfaces. [33]                                                                                           |                |

| Figure 2-5. Design of Network Interface. [33]                                                                                                           | 20             |

| Figure 3-2. Sorter System. [56]                                                                                                                         | 22             |

| Figure 3-2. Sorter System controller model                                                                                                              | 23             |

| Figure 3-3. Loader controller SystemGALS implementation.                                                                                                | 25             |

| Figure 3-4. Conveyor controller SystemGALS implementation (1)                                                                                           | 28             |

| Figure 3-5. Conveyor controller SystemGALS implementation (2)                                                                                           | 29             |

| Figure 3-6. Conveyor controller SystemGALS implementation (3)                                                                                           |                |

| Figure 3-7. Arm Controller SystemGALS implementation.                                                                                                   |                |

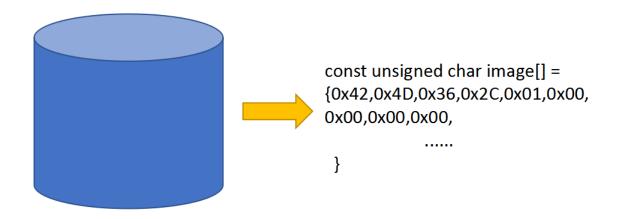

| Figure 3-8. Convert the image to an unsigned char array                                                                                                 |                |

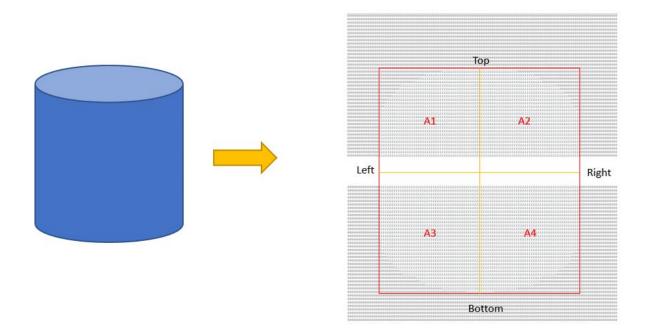

| Figure 3-9. Image Binarization.                                                                                                                         |                |

| Figure 3-10. Binarization C implementation.                                                                                                             |                |

| Figure 3-11. Edge detection C implementation.                                                                                                           |                |

| Figure 3-12. Item recognition C implementation.                                                                                                         |                |

| Figure 4.4. Schedule on one DISC V cons                                                                                                                 | 40             |

| Figure 4-1. Schedule on one RISC-V core                                                                                                                 |                |

| Figure 4-1. Schedule on one RISC-V core                                                                                                                 | 41             |

|                                                                                                                                                         |                |

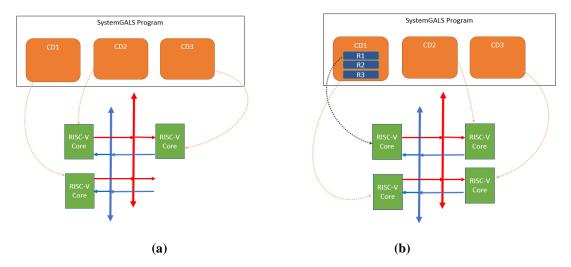

| Figure 4-2. Map clock domains and reactions to multiple cores.                                                                                          | 42             |

| Figure 4-2. Map clock domains and reactions to multiple cores                                                                                           | 42             |

| Figure 4-2. Map clock domains and reactions to multiple cores<br>Figure 4-3. Mapping on software and hardware co-design<br>Figure 5-1. Schedule mapping | 42<br>45<br>46 |

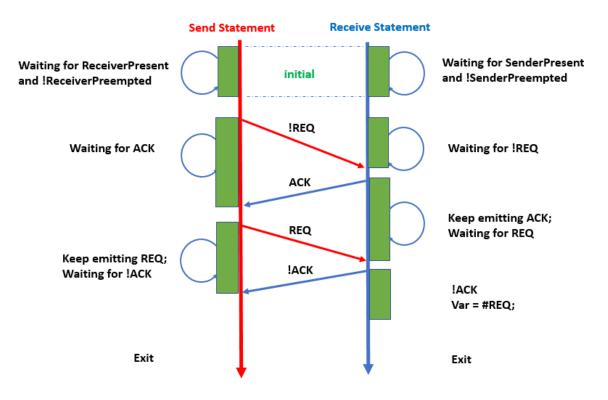

| Figure 5-5. Channel handshake flow                                  | 48 |

|---------------------------------------------------------------------|----|

| Figure 5-6. Send function                                           | 50 |

| Figure 5-7. Loader controller execution logic.                      | 53 |

| Figure 6-1. ChipyardSubsystem. [60]                                 | 56 |

| Figure 6-2. ChipyardSystem. [60]                                    | 58 |

| Figure 6-3. DigitalTop. [60]                                        | 59 |

| Figure 6-4. Communication between the Host and the Simulation. [60] | 61 |

| Figure 6-5. InitZero configuration. [60]                            | 63 |

| Figure 6-6. Up and here view. [60]                                  | 65 |

| Figure 6-7. Single-core platform configuration. [60]                | 65 |

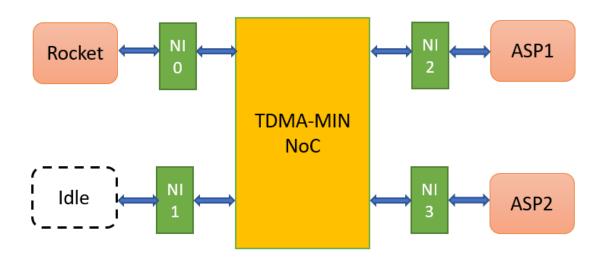

| Figure 7-1. Multi-core execution platform architecture overview     | 69 |

| Figure 7-2. TDMA-MIN NoC connections                                | 70 |

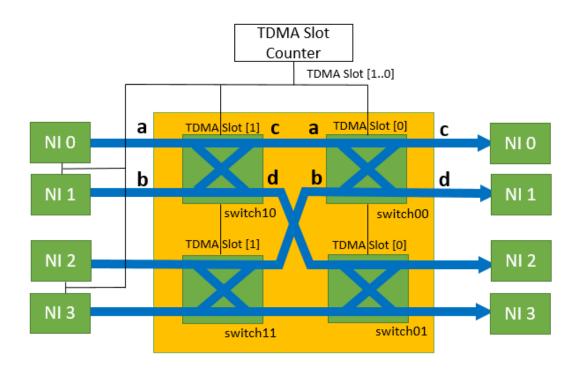

| Figure 7-3. 4-port TDMA-MIN NoC with Network Interfaces.            | 71 |

| Figure 7-4. 4-port TDMA-MIN NoC Chisel implementation               | 72 |

| Figure 7-5. Network Interface Chisel implementation.                | 75 |

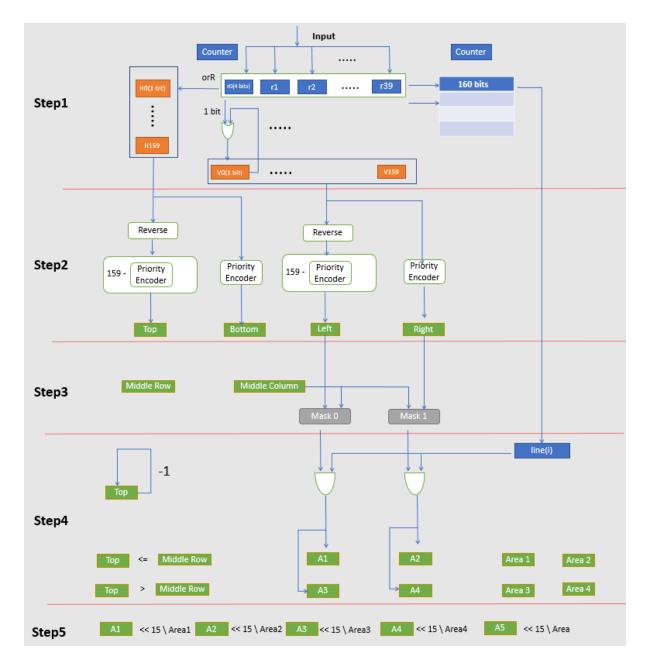

| Figure 7-6. Main data processing procedures in ASP1                 | 78 |

| Figure 7-7. ASP1 Chisel implementation                              | 80 |

| Figure 7-8. ASP2 Chisel implementation                              | 82 |

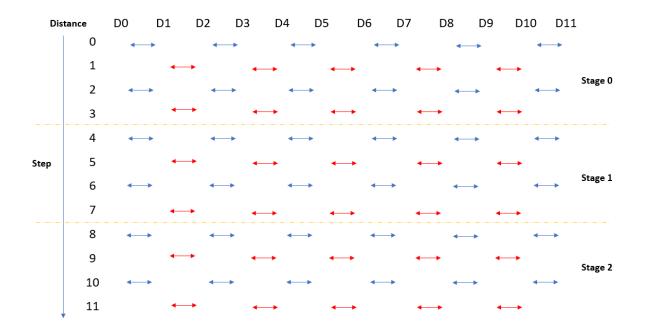

| Figure 7-9. Sorting distances with Odd-Even Transposition Sort.     | 84 |

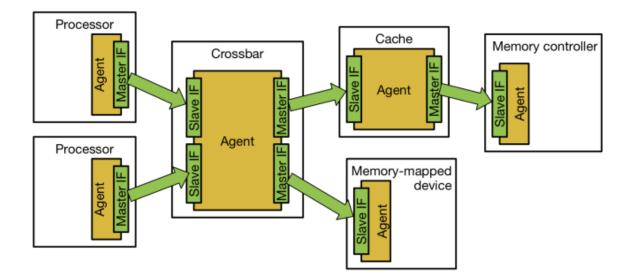

| Figure 7-10. Example of a TileLink network topology.[62]            | 85 |

| Figure 7-11. The five channels that comprise a TileLink link. [62]  | 86 |

| Figure 7-12. DMA controller Chisel implementation.                  | 88 |

| Figure 7-13. DMA reader Chisel implementation.                      | 90 |

| Figure 7-14. Peripheral module Chisel implementation                | 93 |

| Figure 7-15. Peripheral Lazy module trait and config fragment       | 95 |

| Figure 8-1. Sample item images                                      | 97 |

| Figure 8-2. Peripheral software interface implementation            |    |

| Figure 8-3. Program compilation. | 99 |

|----------------------------------|----|

|----------------------------------|----|

## List of Tables

| Table 2-1. SystemJ Kernel Constructs. [33]              | 9  |

|---------------------------------------------------------|----|

| Table 2-2. Data Modules and Interface Functions. [29]   | 10 |

| Table 2-3. Simultaneous Connections in TDMA Slots. [33] | 19 |

| Table 7-1. Channel A signal description. [62]           | 91 |

| Table 7-2. Channel D signal description. [62]           | 91 |

Introduction

## **Chapter 1. Introduction**

Nowadays, the increasingly rapid changing of market requirements resulting from the development of globalisation and the prevailing of Consumerism is promoting a new revolution in manufacturing [1]-[5]. It requires not only flexible production of products [6]-[8] but also agile development of product lines that perform production processes [9]-[11]. Compared with pure software development, the development of IoT (Internet of Things) and IIoT (Industrial Internet of Things) applications involves both software and its execution platform. In this chapter, we first discuss the specific requirements in industry 4.0 [12]-[16] and then explore how to achieve the agile development of IIoT applications, especially the industrial control systems.

## 1.1. The Vision of Industry 4.0

With three industrial revolutions, industrial production is gradually gaining higher productivity and more robust capability to produce complicated products by introducing revolutionary technologies into production processes: the machine and steam power in the first revolution, the electromechanical machine in the second revolution, and the information and communication technology in the third revolution [17], [18]. Currently, there is a new increasing requirement for industrial production, which is neither higher productivity nor higher complexity. That is customisation [6]-[8]. The increasingly rapid change of market requirements has made manufacturers more and more aware that "they can no longer capture market share and gain higher profits by producing large volumes of a standard product for a mass market" [19]. In 2013, the German government published a report that depicts a vision of the fourth industrial revolution (industry 4.0) [13] to satisfy the product customisation in even a small amount and, in the meanwhile, maintain the cost at the mass-production level.

Industry 4.0 describes an intelligent manufacturing paradigm to combine the consumer and the manufacturer much more tightly [20]. A consumer can directly send his/her special requirements for a product to the factory, which then accordingly adjust the manufacturing process and start the manufacturing quickly. The same product line may dynamically employ hundreds of manufacturing processes to produce different customised products. This vision

encourages the manufacturing systems to comprise a group of interconnected and configurable subsystems rather than a unitary product line with fixed procedures [21]. Industry 4.0 also encourages the interconnections among various systems ranging from the custom order system to the logistic system, enabling customers to track the orders during their whole lifecycle [22], [23]. This kind of smart factory introduced in industry 4.0 is more and more like a software application, requiring rapid development, static and dynamic adaptability, flexibility, variety, and fault tolerance.

Undoubtedly, the achievement of the vision of industry 4.0 demands advancement in every part of building up the manufacturing process, especially the design of control systems. Generally, it mainly involves the design paradigm, programming languages, compilers, and execution platforms.

### 1.2. System-Level Programming Language

The kernel of the smart factory is the control systems, which are more intelligent, more flexible and involve more communication between internal subsystems and between the systems and the environment. With the complexity of the systems significantly increasing, the system designer should put more emphasis on system-level behaviour rather than the behaviour of usual programs, thus requiring system-level design languages [24]-[28]. Concretely, a systemlevel programming language should promote the modularity of control systems design, facilitate the composition of the components into larger systems, and simplify the concurrent programming design. Furthermore, it should encourage compatibility with existing programming languages due to the difficulty of bringing up all of the facilities for a new language from scratch.

SystemGALS [29], on the basis of its predecessor SystemJ [27], [28], are developed toward this goal. It was promoted Embedded Systems Research Group of the University of Auckland in 2019 and inherited from SystemJ language the Globally Asynchronous Locally Synchronous (GALS) model of computation [30]. And it also keeps the model of time, kernel statements, and the hierarchy of design units, clock domains and reactions in SystemJ. SystemJ programs have JAVA as the host language and must be executed on platforms supporting JVM. In contrast, SystemGALS can target various software programming languages, including C, as well as hardware description languages, which broadly extend the application domain and

potential execution platforms that include the combination of traditional general-purpose processors and application-specific (hardware) processors. Furthermore, SystemGALS completely separates complex data computation from control flow by introducing a new design unit, called the data module.

In this thesis, we leverage SystemGALS to design the controllers for three components in a smart Sorter System. And the controller applications involve an image recognition algorithm to detect the type of an item processed during the system runtime. This algorithm has been implemented in two versions: pure C programs and C programs with two hardware accelerators, promoting the capabilities of SystemGALS to support the specification of systems that are implemented in combinations of hardware and software.

## **1.3. Execution Architecture**

Any control system involves programs and their execution platforms. On the one hand, apparently, with the rapidly increasing diversity of industrial applications, it is almost impossible to design a general-purpose architecture for execution platforms suitable for all applications. On the other hand, accompanied by the gradual invalidation of Moore's law, programmers cannot expect to promote programs execution efficiency by the improvement of the fabrication process of integrated circuits, which also stimulate the exploration of computer systems architecture. John Hennessy and David Patterson, the recipients of the Turing Award (2017), describe the following decades as "a new golden age for computer architecture" [31]. And, the multi-core processor architecture with dedicated accelerators implemented on a single chip tends to be a solution to cope with these problems.

For the controller applications of the Sorter System, we create a multi-core processor architecture with a RISC-V [32] processor, two accelerators and a TDMA-MIN [33] network to demonstrate a potential execution architecture for the software and hardware co-design of SystemGALS specifications.

## 1.4. Agile Hardware Design

The vigorous exploration of execution architectures further encourages the revolution of hardware design [34], which is inefficient and cumbersome compared to current software application designs. In the last decades, software programming languages have undergone enormous changes by continually adopting new features and new paradigms such as object-orientated programming and functional programming, which significantly facilitate code reuse and thus enable rapid and agile software development [35], [36]. In addition, the prevalence of the philosophy of open-source [37] in software projects broadly promotes the vitality of software development.

In contrast, current dominant hardware description languages (HDL) experience almost no little change from the introduction of VHDL and Verilog in1980s. SystemVerilog, the successor of Verilog, contributes more in hardware verification than in design paradigms. On the other hand, the digital systems tend to be more and more complex, involve more interaction, require a higher degree of customisation and at the same time should provide and lead towards a shorter time of design, test, and fabrication. The pure register-transfer level (RTL) design abstraction in VDHL and Verilog is more and more struggling to cope with all of these requirements.

VHDL and Verilog are powerful to describe a hardware block performing a specific function by declaring registers and using if-then-else and arithmetic statements to describe the combinational logic. However, the procedure-oriented paradigm, which focuses on the flow of signals between registers, is not beneficial for code reuse, which is critical for customisation and agile development. And, the close coupling between the front end and the back end in traditional HDL languages further harms the reuse of existing code. Designers may need to rewrite the programs of the same functions when targeting different FPGAs, ASIC toolchains and VLSI technologies.

Another important factor that hinders the progress of agile hardware design is the scarcity of open-source hardware projects, especially mature commercial projects. Unlike the software designs, the hardware design for an ASIC needs to experience the tape-out and manufacturing process before the products are shipped to the customers. These processes generally cost a large amount of money, ranging from millions to billions of dollars. Moreover, the expected results from experience or simulation experiments in aspects of correctness, performance, and energy efficiency can be very different from physical circuits for the same design. Thus, hardware

Introduction

designs have a more urgent need than software development for open-source projects that have been successfully fabricated and thoroughly tested to encourage the variety of IoT and IIoT applications and shorten development cycles. However, currently no matter the amount or the degree of openness of open-source hardware projects is far less than those in software designs. For example, the instruction set architecture (ISA) that serves as an application binary interface (ABI) between software and hardware is a decisive factor in system designs. However, any implementation and modification of the currently prevailing ISA may require a large amount of money that can be only affordable for large enterprises.

Fortunately, both academic researchers and the industry have identified the problems [34], [38] and devoted considerable effort to improving the situation, including the emergence of Chisel [39] and RISC-V [32] in the 2010s. Chisel is a Scala-based hardware description language proposed by the University of California, Berkeley (UC Berkeley) in 2012, embedded in a modern software language (Scala) and used to generate synthesisable Verilog. This mechanism enables Chisel to introduce the power of modern software languages, such as object-oriented and functional programming paradigm, into the existing hardware design procedures. Furthermore, by inserting an intermediate language and a hardware compiler framework (FIRRTL) [40] between Chisel and target Verilog programs, Chisel can facilitate the design reuse for ASIC and FPGA designs. RISC-V is an open instruction set architecture, which allows developers to implement a processor and freely modify the instructions without any charge, even for commercial purposes.

Despite its short time being in public view, RISC-V has attracted broad support from academia and industry and encouraged various hardware open-source projects, including Chipyard [41], an open-source SoC development framework. In this thesis, we leverage Chipyard to build two execution platforms for SystemGALS programs and develop two hardware accelerators in Chisel to improve the performance of our programs.

## **1.5. Thesis Contributions and Outline**

Agile hardware design also depends on manufacturing procedures. The fabless-foundry model, a mainstream model in semiconductor manufacturing, is facing the same challenges existing in current mass production. However, this is out of the scope of our research. In this thesis, we will focus on the controller designs of the Sorter System application and their execution Introduction

platform. The main contribution of our research can be summarised in three folds. The first one is to evaluate the pros and cons of current tools for industrial control system design by implementing a smart Sorter System. Secondly, we demonstrate a software and hardware codesign example in SystemGALS. The last one is to present a new potential execution framework for SystemGALS programs that will allow the design of hardware/software customised controllers, including both software/runtime system and hardware parts of the final design.

The remainder of this thesis is structured as follows. Chapter 2 gives an introduction about relevant background and tools we will use in this thesis, while SystemGALS designs and an image detection algorithm are explained in Chapter 3. Chapter 4 will illustrate the mechanism behind SystemGALS, including the time model, the execution model and the runtime support system. And, we describe the mapping from SystemGALS programs to C programs in Chapter 5. Chipyard is introduced in Chapter 6 to build an execution platform for SystemGALS that employs hardware/software partitioning and co-design. Chapter 7 will describe the Chisel design of two accelerators for the image detection algorithm and how to integrate these two accelerators into a new execution architecture. Chapter 8 demonstrates the program's execution on the simulators of these two execution platforms. Chapter 9 is the discussion and conclusion.

6

## **Chapter 2. Related Work & Background**

In this thesis, we use SystemGALS to design the Sort System controller and leverage Chipyard, an open-source SoC framework, to create execution platforms for controller programs. And, Chipyard mainly uses Chisel to design SoC components and employs the RISC-V cores to create SoC variants. In addition, one of our execution platforms involves a network named TDMA-MIN. In this chapter, we briefly introduce the related work and background of these tools.

## 2.1. SystemJ

SystemJ [27], [28] is a system-level language that introduces formal syntax and leverages the Globally Asynchronous Locally Synchronous (GALS) formal model of computation [30], thus providing an automatic mechanism to validate, verify and debug the system design. Additionally, its incorporation of Java makes it possible to utilize complex data structures and objects to support data-driven operations.

The basic SystemJ design consists of multiple clock domains, with one clock domain corresponding to one physical component in a product manufacturing system. One clock domain can further comprise multiple concurrent reactions to control the component to perform specific behaviour routines or respond to messages from the environment (the external world) and reactions in the same or another clock domain. In addition, each reaction can have child reactions nested in itself up to arbitrary depth, promoting behavioural design hierarchy. Each clock domain is driven by its own logical clock called tick in SystemJ, and all of the reactions in the same clock domain share an identical clock. When executing the SystemJ programs, a clock domain must be waiting for all reactions in it to finish one-tick execution before advancing to the next tick. The execution boundaries are denoted by an explicit pause statement or implicit pause in a derived statement. On the other hand, ticks for different clock domains have no relationship with each other.

SystemJ leverages constructs/objects of channels and signals to enable communication between reactions, clock domains, and environment. The channels are responsible for the data exchange between the clock domains, while the signals are mainly in charge of broadcasting

information within one clock domain or for enabling communication of the clock domain with its environment (physical or artificial). The statuses and values of signals and channels can be changed during the execution in one tick but only updated at the housekeeping stage between two ticks. Thus, it promotes a so-called delayed semantics that guarantees that change of the status of the signal will become visible to potential receivers in the stable state of the clock domain.

In SystemJ, clock domains and reactions are implemented by a mix of SystemJ and JAVA statements. The types of signals and channels can be any type supported in JAVA. The SystemJ compiler will first compile the program into pure JAVA programs that are in turn compiled by the JAVA compiler into Bytecode which can be executed by the JAVA Virtual Machine (JVM).

#### 2.2. SystemGALS

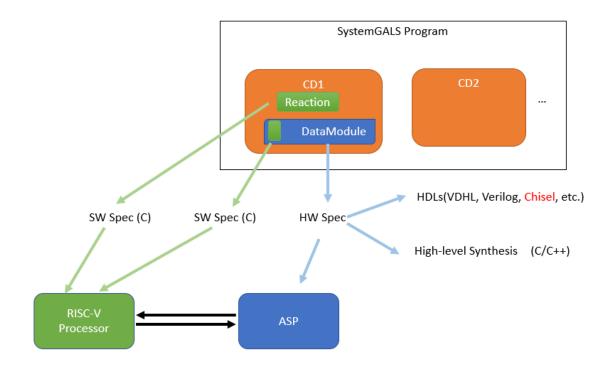

By extending JAVA, SystemJ can support high-level data abstraction and utilize the power of third-party libraries. However, this also limits the execution platform for SystemJ programs due to its demand for JVM, which is too heavy for the resource constraint embedded platforms. SystemGALS [29], a new GLAS system-level language, was proposed in 2019. SystemGALS separates the control flow from data computation in the SystemJ specification by introducing a new construct of data modules to solve this problem. And, the data modules are empowered by other software languages. At the same time, it uses typically one language as the target/host language for control flow of SystemGALS programs. SystemGALS inherits most kernel statements (Table 2-1) and derived constructs from SystemJ. As the control flow statements are designed as plain as possible, they can easily be mapped into any other programming language. A SystemGALS compiler will first compile its statements into the target language programs and let the target language compiler take charge of the rest compilation jobs. In this way, SystemGALS can target a range of host languages (e.g. C, JAVA) and extend the range of options of execution platforms. Furthermore, SystemGALS allows data modules to be implemented in hardware description languages or high-level synthesis (HLS) and thus enables the software and hardware co-design.

| Statement                          | Description                                          |

|------------------------------------|------------------------------------------------------|

| p1;p2                              | p1 and p2 in sequence                                |

| pause                              | Consumes a logical instant of time (a tick boundary) |

| [input] [output] [type] signal S   | Declaring a pure or valued signal                    |

| emit S [(exp)]                     | Emitting a signal with a possible value              |

| while(true) p                      | Temporal loop                                        |

| $present(S){p1}else{p2}$           | If signal S is present do p1 else do p2              |

| [weak] abort ([immediate] S) {p}   | Preempt if S is present                              |

| [weak] suspend ([immediate] S) {p} | Suspend for 1 tick if S is present                   |

| trap (T) {p}                       | Software exception                                   |

| exit T                             | Throw a software execption                           |

| $p1 \parallel p2$                  | Run p1 and p2 in lock-step parallel                  |

| [input] [output] [type] channel C  | Declaring input or output channel                    |

| send C[(exp)]                      | Sending data over the channel                        |

| receive C                          | Receiving data over the channel                      |

| #C                                 | Retrieving data from a valued signal or channel      |

Table 2-1. SystemJ Kernel Constructs. [33]

SystemGALS also introduces a new data type of control flow variable (CFV) and interface functions (Table 2-2) to enable the communication between the reaction control flow and data modules. Data modules reside in the reactions and accept signals, channels, and CFVs as parameters. The output of data modules can be stored in typed signals or influence the control flow via CFVs. SystemGALS provides interface functions for host languages to acquire or change the values and statuses of signals and CFVs. Unlike signals and channels, the value of CFV that is either true or false will be changed immediately during the current tick. The control flow can only use the if-else statement to check the value of CFVs and then choose the program branch.

| DataModule func(arguments ){+ (stmts) +} | Declaration of a data module                                      |

|------------------------------------------|-------------------------------------------------------------------|

| dmcall func(arguments)                   | Call of a data module within a reaction                           |

| sgl_GetSigVal                            | Function that extracts the signal value for the data computation  |

| sgl_SetSigVal                            | Function that assigns the signal value from the data computation  |

| sgl_GetSigStatus                         | Function that returns the signal status                           |

| sgl_GetChanVal                           | Function that extracts the channel value for the data computation |

| sgl_SetChanVal                           | Function that assigns the channel value from the data computation |

| sgl_SetCFV                               | Function that sets the value of CFV to 0, 1 (false, true)         |

| sgl_GetCFV                               | Function that extracts CFV status                                 |

Table 2-2. Data Modules and Interface Functions. [29]

Generally, a typical SystemGALS system can be composed of one or more clock domains, as shown in Figure 2-1. Each CD contains multiple concurrent reactions that can have child reactions nested inside. The reactions employ data modules to perform computation and use CFV as interfaces to branch program execution. Channels and signals are responsible for communication between reactions and clock domains. In addition, signals can enable information exchange between the system and the environment that includes, for example, sensors and devices outside the designed SystemGALS system. Chapter 3 and Chapter 4 will explain the statements and mechanism behind SystemGALS programs in detail.

Figure 2-1. An illustration of an example SystemGALS system. [29]

## 2.3. RISC-V

RISC-V [32] is an open-source and royalty-free instruction set architecture (ISA). It is based on the reduced instruction set computer (RISC) principle developed from the observation that most programs did not use the vast majority of processor instructions. In 1980, David Patterson started the project of Berkeley RISC at the University of California, Berkeley (UC Berkeley). This project with the MIPS project at Stanford University is later hailed as two seminal research projects to develop the RISC concept. RISC-I [42] was the first implementation in the Berkeley RISC project with a technique of register widowing and a smaller set of 32-bit instructions compared with a complex instruction set computer (CISC) architecture. Then RISC-II [43], the second attempt in the project, introduced 16-bit instructions to improve code density. After Berkeley RISC, the SOAR [44] and SPUR [45]projects in 1984 and 1988 were referred to as RISC-III and RISC-IV, respectively. In 2010, motivated by the need for an ISA in parallel computing program and the long negotiation time and high cost to get a license for current successful ISAs, Krste Asanović of the UC Berkeley, together with David Patterson, led a three-month project to develop a new open-source instruction set, currently known as RISC-V. Now, RISC-V already has many contributors outside of UC Berkeley and is under the management of a Swiss non-profit business association, RISC-V International.

RISC-V allows anyone to freely use and customise the ISA [38], thus facilitating the customisation of the execution platform for specific applications. The ISA customisation can be achieved in two aspects. The first one benefits from the modular design of RISC-V. Generally, the integer instruction set (I) serves as the base part. The optional extensions include multiply and divide (M), atomic operation (A), single-precision floating point (F), double-precision floating point (D) and many other extensions. All of these instructions have 32-bit, 64-bit and 128-bit address space variants. This base-plus-extension approach allows designers to choose the proper combination of the base set and extension parts for their design goals. In addition, The RISC-V ISA sticks to the RISC philosophy and puts a significant emphasis on minimising instruction count. The base instruction set contains only 47 instructions. This can save bits in the instruction format and operation codes and give more space to the custom instructions, which may significantly improve the execution performance.

Along with the development of RISC-V architecture, UC Berkeley also implemented a 64-bit in-order scalar processor core (Rocket) [46] and a 64-bit out-of-order core (BOOM) [47]. Furthermore, they introduced the Rocket Chip Generator to serve as a shared code base to generate different SoC variants agilely. And all of these were implemented in the Chisel language proposed by UC Berkeley in 2010 [39].

## 2.4. Chisel/FIRRTL

Chisel [39] is a hardware design language embedded in the JVM language Scala that has both object-oriented and functional programming features. Chisel serves as a library in Scala, thus can leverage all of the advanced software programming features provided by Scala. The most important concept introduced by Chisel is a generator, which is also the most significant advantage compared to the traditional HDLs (e.g. VHDL, Verilog). Generally, the generator in Chisel is a parameterizable class that can produce a collection of digital circuit instances by manipulating the input parameters. And, based on Scala, generators in Chisel can provide much more flexible parameters than Verilog, thus significantly extending the boundary of instances that one generator can represent. For example, when creating a generator of the finite impulse response (FIR) filters, Chisel allows programmers to pass a window function to the generator as an argument. So the programmer can create a new FIR filter by just defining another window

function and retain the same FIR generator. Furthermore, Chisel provides a range of parameterizable components, such as arbiters and the FIFO queues in its standard library.

Chisel utilizes the meta-programming technique, which means Chisel programs are used to generate programs written in other HDLs. Currently, Chisel only supports Verilog as its target language. Instead of directly generating a Verilog program, a Chisel program will be elaborated into the Flexible Intermediate Representation for RTL (FIRRTL) [40]. FIRRTL has its own syntax to describe the circuit and still contains high-level constructs such as vector types, partial connects, and modules, which Verilog does not support. A FIRRTL compiler will run a chain of lowering transformations written in Scala to gradually translate these high-level constructs into the lowered FIRRTL forms that only contains low-level constructs that then are mapped to equivalent Verilog programs. Programmers can also rewrite these transformations to generate expected Verilog programs for different FPGAs or ASIC technologies.

### 2.5. Chipyard

Chipyard [41] is an agile and open-source framework based on RISC-V and Chisel ecosystem, allowing programmers and researchers to develop and test their own systems on a chip (SoC) in a singular location. It contains various open-source generators of hardware design to generate SoC components, a convenient parameter system to connect all components, and open-source and commercial simulators to test digital designs. It also incorporates software toolchains to compile software programs into RISC-V binaries and other tools like FireSim [48] and Hammer [49] to facilitate FPGA prototyping and the VLSI flow.

#### 2.5.1 Components

The Rocket chip generator [46] in Chipyard serves as a foundation for developing a RISC-V SoC. As shown in Figure 2-2, it contains Rocket cores as default, buses implemented in TileLink [50] protocol, TileLink to AXI converters, and other standard peripherals such as the BootROM, the PLIC (Platform-Level Interrupt Controller), the CLINT (the Core Local Interrupts), and the Debug Unit. A Rocket core is a RISC-V in-order core developed in Chisel. It supports floating-point computation by including a floating-point unit and enables branch prediction and virtual memory by containing a memory management unit (MMU). And a Rocket tile wraps up a Rocket core with L1 caches and a page-table walker (PTW) to

communicate with other components in the SoC via the TileBus. Both the Rocket core and the Rocket tile exit in Chipyard in the form of generators rather than instances, which means one can customise a Rocket core or a tile by changing parameters in the generators, such as the cache size, bit width of the core and even the supporting instruction set. Actually, all of the components developed in Chisel in Chipyard are generators, thus significantly facilitating the design space exploration. Chipyard also contains an out-order RISC-V core (BOOM) [47] and another RISC-V in-order core (CVA6, formerly named Ariane) [51] written in SystemVerilog, which can be alternative cores in the SoC generator or coexist with Rocket cores to create a heterogeneous SoC.

Figure 2-2. Rocket chip generator components. [60]

In addition to the processor cores, Chipyard also provides two main methods to incorporate the accelerators into the SoC: RoCC accelerators and MMIO accelerators. The former ones reside in the tile with a processor core (Figure 2-3) and use custom ISA instructions and the Rocket custom coprocessor interface (RoCC) to communicate with the processor core. One processor which supports RoCC accelerators like Rocket cores and BOOM cores can have up to four

RoCC accelerators in one tile, while there is no such limitation for MMIO accelerators. MMIO (Memory-mapped I/O) accelerators are connected to the peripheral bus and controlled by the processor via resisters in the same address space with main memory. Hwacha [52], Gemmini [53], and SHA3 are three RoCC accelerators provided by Chipyard. Hwacha is a vector architecture coprocessor, Gemmini accelerates the matrix-multiply operations, and SHA3 implements the SHA3 hash function. Chipyard also contains a collection of custom software toolchains for Hwacha to demonstrate how to add custom instruction to Spike (the instruction-level simulator) and the GNU bintuils. Besides processor cores and accelerators, Chipyard incorporates many other system components that can be integrated into the SoC, such as a network interface controller, peripheral components (e.g. UART, SPI, JTAG, I2C, PWM), and the utilities used for chip testing.

Figure 2-3. RoCC accelerator connection. [60]

#### 2.5.2 Parameter System

Chipyard provides a parameter system to facilitate the connections between different components to create a custom SoC. There are three most important problems to solve when using generators to compose a whole system agilely. The first one is that how to configure all of the generators in one location. The parameterised generators of digital designs need to be

appropriately configured, and they tend to be stored in different files. It will be tedious and error-prone to tune the parameters by traversing all of these files. Furthermore, one generator may reference the parameters from another generator when instantiated. For example, the bit width of the components needs to be compatible with the operand width of the processor. The third problem involves the validation of the parameters of generators in the SoC interconnection. That is how to check the compatibility from the whole system's perspective after specifying parameters for all generators.

In Chipyard, the configuration of generators can be accomplished in one configure class, which consists of multiple additive configure fragments with the symbol of '++' between each other. Each configure fragment corresponds to one component and is in charge of specifying parameters for this component. Generally, a fragment is a partial function that maps a component key to a case class. The component key is typically the Option Type in Scala, and the value can be a container that contains the case class in the mapping or the None object when the mapping does not exist. On the other hand, a case class is defined alongside the component generator and gives default values for the generator parameters. And the config fragment can modify all or part of the default values of parameters by passing new parameters to the case class.

In addition, a component generator will be instantiated in a corresponding trait, which also defines how this component will be connected to the SoC. Traits in Scala are similar to interfaces in JAVA, and objects and classes can extend multiple traits simultaneously. Chipyard uses the Rocket chip generator as a basis to extend all of the component traits to create a custom SoC. When instantiating a generator, the trait will make a query using the component key to acquire the concrete values for parameters from the configure class. If the configure class does not contain a specific configure fragment for one component, the query result will be a None object, and the component will not be hooked up to the SoC.

Chipyard also leverages a Context-Dependent-Environment (CDE) parameterisation system to enable the key query. When querying a key, the CDE system provides three "Views" of a configure class: site, here, and up, which designate the query scopes. The site view is a global view of the configure class. Generally, a trait will use a p(somekey) function to make a key query, which means the trait will traverse all of configure fragments in a configure class from the first one (the one closest to the configure class declaration) to the last one until it finds a partial function which maps the key to a parameter case class. In this case, the configure class is regarded as the global view (site) of this query. The p is a variable of the parameter type that is a subclass of an abstract view class, and it will be bundled together with this concrete configure class when generating the SoC design. In addition, a configure fragment can also map a key to another key query to reference the parameters of the components. For example, in a configure fragment class, a site (somekey) expression will look up the value of somekey in the whole configure class, a here (somekey, site) will just locally search in this fragment class, while an up (somekey, site) will find the value in the fragments behind this fragment in the configure class. So the final result of a key query can be influenced by the order of the fragments in a configure class.

#### 2.5.3 Diplomacy

Once all generators' parameters are specified, it is crucial to validate the compatibility between different components. Chipyard introduces a Diplomacy library [49] to extend Chisel for facilitating parameters negotiation and validation. There are two most essential features in Diplomacy. The first one is to enable the two-phase hardware elaboration in Chipyard. In Chisel, the phase of running the Chisel programs to generate FIRRTL representation of a circuit is called elaboration. By declaring the concrete circuit designs of the Chisel code as lazy (a keyword in Scala) modules, Chipyard delays the elaboration of the SoC and leverages Diplomacy to create a graph of edges and nodes demonstrating the interconnection of the SoC first. In the TileLink bus protocol, almost every component is wrapped into a tile, and each tile can contain one or more nodes. In contrast, the edges represent the connections between these nodes. Then, Diplomacy will traverse these nodes and edges to check the mutual compatibility of the system. The other significant feature of Diplomacy is that instead of just validating the parameters, Diplomacy allows the negotiation of the parameters between nodes, which means nodes can specify their parameters based on knowledge of other nodes. Then at the elaboration phase, the generators can leverage these parameters to create concrete hardware circuits.

#### 2.6. TDMA-MIN NoC

TDMA-MIN NoC [33] is a Network-on-Chip (NoC) that integrates the Time Division Multiple Access (TMDA) model with Multistage Interconnect Network (MIN) to provide a timepredictable and scalable architecture for commutation of multiple cores in one chip. It was first introduced in 2016 [54], [55] and later expanded in 2017 [33] to create a general execution platform for SystemJ programs. It typically consists of multiple  $2 \times 2$  crossbar switches arranged in k stages and interconnected with each other in a Banyan type. The value of k equals the value of k in the expression of  $N = 2^k$ , where N represents the total ports in a TDMA-MIN NoC and must be greater than or equal to the number of cores in the chip. Each port is generally connected to a Network Interface (NI) with one input and one output, and a NI is, in turn, ported to one core. Concretely, each crossbar switch has two inputs, two outputs and two states inside: parallel and cross, which control the connection between the inputs and outputs. And the states of all of the switches can be driven by the TMDA slot counter, whose value will cyclically change from 0 to  $(2^k - 1)$ . Thus a full TDMA round has  $2^k$  slots with the duration of one slot generally equalling one clock cycle. A straightforward mechanism to drive the switches is to use each bit in the binary code of the slot counter to control the switches in the same stage. The TDMA slot counter also serves as an input for the network interfaces to decide when to send the packets to the NoC.

Figure 2-4. 8-port TDMA-MIN NoC with Network Interfaces. [33]

For example, a typical eight ports TDMA-MIN is shown in Figure 2-4. The NoC has three stages of crossbar switches and is driven by a 3-bit slot counter with each bit corresponding to each stage. If 0 represents the state of parallel and 1stands for the state of cross, when the TDMA slot counter is 000 in binary code, states of three stages of the switches will be parallel, parallel and parallel, respectively. Thus, the packets from NI 0 will be sent to NI 0 in this slot. In the next clock cycle, the counter will be 001, changing the state of switches in the first stage (the rightmost stage) from parallel to cross. Then NI 0 will send the packets to NI 1.

Similarly, each of the other seven input ports in the NoC other network interfaces has a different corresponding output port in one TDMA slot. The mapping from input ports to output ports has a relationship in the binary format that can be expressed as in Equation (1), where I is the input port number, D is the destination port number,  $\bigoplus$  denotes the bitwise XOR operation, and S is the current slot value represented by its binary value. Mirror(I) represents the binary mirrored value of I.

$$D = Mirror(I) \bigoplus S$$

Equation (1) [33]

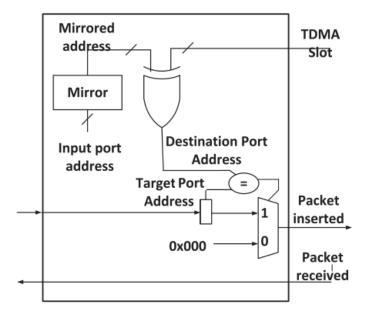

In the 8-port TDMA-MIN NoC, the exact correspondence is shown in Table 2-3. Apparently, each network interface can infer the destination port according to the current slot value. A possible design of the network interface is shown in Figure 2-5.

|            |        |        | Destination port in TDMA slots |        |        |        |                         |        |        |

|------------|--------|--------|--------------------------------|--------|--------|--------|-------------------------|--------|--------|

| Input port | Mirror | slot 0 | $\operatorname{slot} 1$        | slot 2 | slot 3 | slot 4 | $\operatorname{slot} 5$ | slot 6 | slot 7 |

| 0          | 0      | 0      | 1                              | 2      | 3      | 4      | 5                       | 6      | 7      |

| 1          | 4      | 4      | 5                              | 6      | 7      | 0      | 1                       | 2      | 3      |

| 2          | 2      | 2      | 3                              | 0      | 1      | 6      | 7                       | 4      | 5      |

| 3          | 6      | 6      | 7                              | 4      | 5      | 2      | 3                       | 0      | 1      |

| 4          | 1      | 1      | 0                              | 3      | 2      | 5      | 4                       | 7      | 6      |

| 5          | 5      | 5      | 4                              | 7      | 4      | 1      | 0                       | 3      | 2      |

| 6          | 3      | 3      | 2                              | 1      | 0      | 7      | 6                       | 5      | 4      |

| 7          | 7      | 7      | 6                              | 5      | 4      | 3      | 2                       | 1      | 0      |

In this thesis, we implement a 4-port TDMA-NoC in Chisel and use it to connect one Rocket core and two accelerators. Chapter 7 will describe it in detail.

Figure 2-5. Design of Network Interface. [33]

**Motivating Example**

## **Chapter 3. Motivating Example**

In this chapter, we first introduce our motivating example, the Sorter system and describe its functionalities. Then, according to the functionalities, we demonstrate the SystemGALS designs for three controllers within the Sorter System. In addition, one of the controllers also involves an image detection algorithm. Hence, this chapter also illustrates the algorithm and its C implementation. In this thesis, we also implement some functions of this algorithm in hardware, which will be introduced in Chapter 7.

### **3.1. Sorter System**

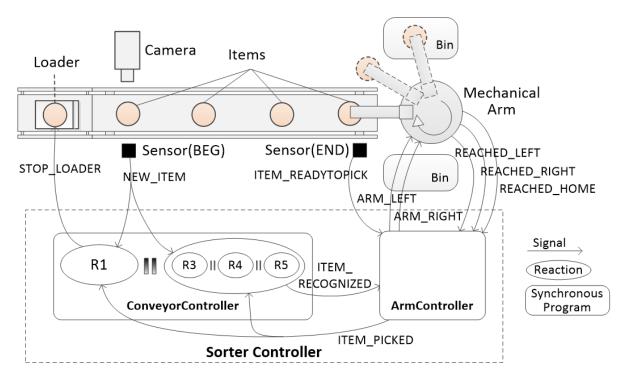

The primary purpose of this Sorter System [56] is to take items at the input, places items on a conveyor, identify the types of the items while they are transferred towards the output and put them into different bins according to their classes at the output. To simplify the application, we only define two types of objects: cylinders and cones. As shown in Figure 3-1, there are mainly three mechatronic devices in this System: Loader, Conveyor, and Mechanical Arm. The Loader is in charge of grabbing the items one by one and putting them on the input side of the Conveyor. Then Conveyor will take the item to the designated area, where it will be picked up by the Mechanical Arm. While the item is moving, a camera will take a picture of the item, which the Conveyor controller will process to detect the type of the item before the item arrives at the end (output side) of the Conveyor and is lifted by the Mechanical Arm.

**Motivating Example**

Figure 3-2. Sorter System. [56]

## 3.2. Model of The System

This Sorter System includes three mechatronic devices and their corresponding controllers. The controllers will issue signals to the devices to perform specific actions and exchange information with each other. And, the devices need to give feedback to the controllers when they accomplish their tasks. For the Loader, it needs to perform four actions: move to a bin that contains the items, grab one item, move its loading arm to the Conveyor, and release the item on the Conveyor. So, we design four pairs of signals between the Loader controller and Loader device, as shown in Figure 3-2. The Mechanical Arm also needs to finish four behaviours: move to Conveyor, grab the item on the Conveyor, move to the right bin if the item is a cylinder or the left bin if it is a cone, and release the item into the bin. So, there are also four pairs of signals between the Arm controller and the Mechanical Arm. As to Conveyor, the Conveyor controller only needs to start the device at the beginning of System operation.

Besides these three devices, the Sorter System also contains two sensors and one camera, as shown in Figure 3-1. The sensor at the beginning position is to generate a NEW\_ITEM signal so that the camera can realise when to take a picture of the item. The other sensor at the end

position is to issue an ITEM\_READYTOPICK signal to inform the Mechanical Arm to grab the item. In this thesis, we leverage a simulation way to emulate the work process of the Sorter System, which means to define three more SystemGALS programs for devices to generate the corresponding signals. In addition, to simplify the simulation, we integrate the functions of sensors and cameras into the controllers. Specifically, once the Loader puts the item on the Conveyor, the Loader controller is responsible for sending a NEW\_ITEM signal to the Conveyor controller, which will get a BMP image from a file to emulate the function of the camera. Then, the Conveyor controller is in charge of sending an ITEM\_READYTOPICK signal to the Arm controller after recognising the class of the item. The model discussed above is shown in Figure 3-2.

Figure 3-2. Sorter System controller model.

Controllers not only need to take the responsibility of synchronisation and communication but also undertake the computation part. In our case, the Conveyor controller should perform an image recognition algorithm to detect the type of item, which is discussed in detail in section 3.4. Another task for the Conveyor controller is to monitor the load on the Conveyor. For example, if the load reaches Conveyor capacity, the Conveyor controller will inform the Loader controller to stop loading. Once the amount of items (load) on the Conveyor is less than Conveyor capacity, loading will resume. The load will decrease when the Mechanical Arm

picks up one item, so the Arm controller should also notify the Conveyor that an item has been picked up via an ITEM\_PICKED signal.

For this model, we made three assumptions in our case: The first one is that the Conveyor controller can successfully detect the type of every item. The second one is that the Conveyor controller can finish the item recognition before the item reaches the picking area. The last one is that the arm has enough time to complete the pick and release procedures. In reality, the program can add an error handler if the type detection fails, for example, by putting the unrecognised item into a particular bin. Also, the system can fulfil the last two assumptions by adjusting the Conveyor moving speed or the loading frequency. These are out of the scope of this thesis.

## 3.3. SystemGALS Program Design

As discussed above, the Sorter System consists of three global level components or three subsystems: Loader, Conveyor, and Mechanical Arm. Each component can be viewed as a Locally Synchronous system due to the fact that all the operations within the subsystem are driven by the common clock. In SystemGALS, a Locally Synchronous system can be declared as a clock domain (CD). So we design three clock domains for the Loader controller, Conveyor controller and Arm controller.

#### 3.3.1 Loader Controller

Generally, a clock domain begins with the name of the clock domain followed by the definition of input and output signals and channels enclosed by a pair of parentheses, as shown between lines 1 to 6 in Figure 3-3. All of the signals and channels that the Loader controller use to communicate with other controllers should be defined in this pair of parentheses. Lines 4 and 5 define four pairs of input and output signals between the Loader controller and the Loader device corresponding to the four actions that the Loader device should perform: move to the bin, grab an item, move to the Conveyor and release the item. Lines 2 and 3 define the signals and channels between the Loader controller. The channel definition must designate the type of value that the channel will carry. The type can be any C type, including the struct type. The main body of the clock domain comes after the signal and channel definition with a connection symbol " ->" and is enclosed in a pair of curly braces. Within the main body is the definition of the reactions, which is also encompassed by a pair of curly braces.

will be demonstrated in the Conveyor controller. In the clock domain of the Loader controller, there is only one reaction (R1) with an infinite loop inside enclosing all of the behaviours of this reaction. It is a typical pattern in SystemGALS to define a reaction using a loop statement because a component in an industrial system tends to perform specific actions repeatedly.

| 1  | LoaderController(                                                                   |  |  |  |  |  |

|----|-------------------------------------------------------------------------------------|--|--|--|--|--|

| 2  | input signal START_LOADER, STOP_LOADER;                                             |  |  |  |  |  |

| 3  | output int channel NEW_ITEM;                                                        |  |  |  |  |  |

| 4  | input signal REACHED_BIN, ITEM_GRABBED, REACHED_CONVEYOR, ITEM_RELEASED, RESETTING; |  |  |  |  |  |

| 5  | output signal MOVE_TOBIN, GRAB_ITEM, MOVE_TOCONVEYOR, RELEASE_ITEM, RESET;          |  |  |  |  |  |

| 6  | )->{                                                                                |  |  |  |  |  |

| 7  | {// R1                                                                              |  |  |  |  |  |

| 8  | loop{                                                                               |  |  |  |  |  |

| 9  | await(START_LOADER);                                                                |  |  |  |  |  |

| 10 | abort(immediate STOP_LOADER){                                                       |  |  |  |  |  |

| 11 | abort(immediate ITEM_RELEASED){                                                     |  |  |  |  |  |

| 12 | sustain MOVE_TOBIN;                                                                 |  |  |  |  |  |

| 13 | }                                                                                   |  |  |  |  |  |

| 14 | abort(immediate REACHED_BIN){                                                       |  |  |  |  |  |

| 15 | sustain GRAB_ITEM;                                                                  |  |  |  |  |  |

| 16 | }                                                                                   |  |  |  |  |  |

| 17 | abort(immediate ITEM_GRABBED){                                                      |  |  |  |  |  |

| 18 | sustain MOVE_TOCONVEYOR;                                                            |  |  |  |  |  |

| 19 | }                                                                                   |  |  |  |  |  |

| 20 | abort(immediate REACHED_CONVEYOR){                                                  |  |  |  |  |  |

| 21 | sustain RELEASE ITEM;                                                               |  |  |  |  |  |

| 22 | }                                                                                   |  |  |  |  |  |

| 23 | send NEW ITEM(1);                                                                   |  |  |  |  |  |

| 24 | } do {                                                                              |  |  |  |  |  |

| 25 | abort(immediateITEM_RELEASED){                                                      |  |  |  |  |  |

| 26 | sustain RESET;                                                                      |  |  |  |  |  |

| 27 | }                                                                                   |  |  |  |  |  |

| 28 | abort(immediate RESETTING){                                                         |  |  |  |  |  |

| 29 | sustain MOVE_TOBIN;                                                                 |  |  |  |  |  |

| 30 | }                                                                                   |  |  |  |  |  |

| 31 | abort(immediate REACHED_BIN){                                                       |  |  |  |  |  |

| 32 | sustain RELEASE_ITEM;                                                               |  |  |  |  |  |

| 33 | }                                                                                   |  |  |  |  |  |

| 34 | }                                                                                   |  |  |  |  |  |

| 35 | pause;                                                                              |  |  |  |  |  |

| 36 | }                                                                                   |  |  |  |  |  |

| 37 | }                                                                                   |  |  |  |  |  |

| 38 | }                                                                                   |  |  |  |  |  |

| L  |                                                                                     |  |  |  |  |  |

Figure 3-3. Loader controller SystemGALS implementation.

Between lines 9 and 36 are the statements that represent the control flow of the Loader controller. The Loader needs to wait for a START\_LOADER signal (line 9) to start the loading procedure and stop the processes when the STOP\_LOADER signal is present, which means the number of the items on the Conveyor has reached the capacity. The abort statement (line 10) provides a mechanism to pre-empt the control flow (lines 11 to 23) if the STOP\_LOADER

**Motivating Example**

signal is present and performs a routine(lines 25 to 33) to reset the Loader device, preparing for the following loading action.

The main functionality is achieved by the statements between line 10 and line 23. The Loader controller sequentially emits the signals of MOVE TOBIN, GRAB\_ITEM, MOVE\_TOCONVEYOR, and RELEASE\_ITEM to control the device to finish the loading of one item. As the emitted signal only lasts for one tick, the loader device may fail to capture the signal. So the Loader controller needs to continuously emit the signal in a sequence of ticks until it receives the corresponding signal indicating that the device has finished the specific task. The sustain statement (line 12) is a derived statement, syntactic sugar, for programmers to achieve the continuous emission of a signal. For example, the abort statement (line 11) enclosing the sustain statement can guarantee the escaping from the infinite loop once the feedback signal reaches.

After the Loader device puts an item on the Conveyor, the Loader controller will use the send statement (line 23) to inform the Conveyor controller through the NEW\_ITEM channel. Once the sending procedure is finished, the control flow will return to the beginning of the loop, waiting for the START\_LOADER signal to load another item.

It is worth noting that channels in SystemGALS already have the mechanism to guarantee the information transmission. So it is more common to use channels between clock domains. In this thesis, the way of sustained signals is only used to demonstrate the interaction between controllers and device simulations.

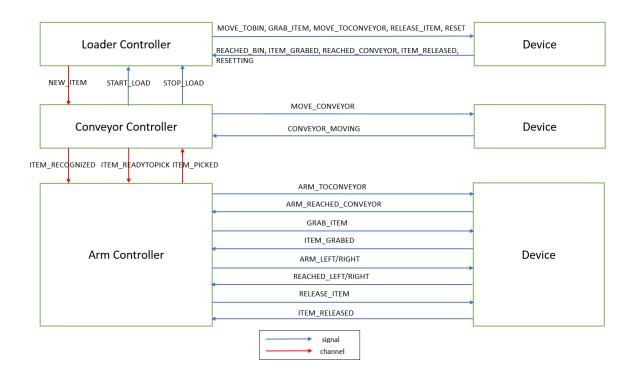

#### 3.3.2 Conveyor Controller

The Conveyor controller is the most complicated part of the system. It has three main functions: control the number of items on the Conveyor, detect the type of an item and send the type of items to the Arm controller successively. For the first functionality of limiting the load on the Conveyor, the change of the quantity of the items on the Conveyor derives from two actions: the Loader puts one item on the Conveyor, and the Mechanical Arm lifts one item. And these two actions can be abstracted as two signals: NEW\_ITEM and ITEM\_PICKED, respectively. As shown in Figure 3-4, the Conveyor controller defines two integer input channels (line 4) to capture these two activities. The NEW\_ITEM input channel has the same name as the output channel in the Loader Controller. These two channel definitions with an identical name but opposite directions build up a complete channel between two different clock domains.

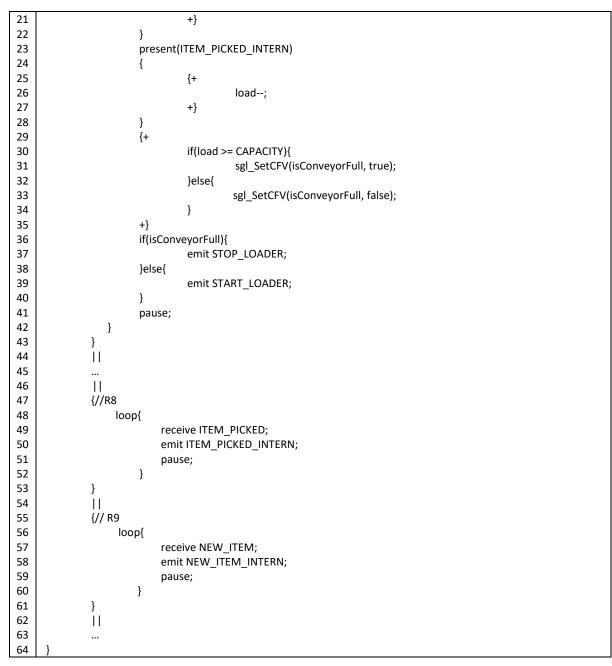

Moreover, the Conveyor controller uses two separate reactions to receive the message via the channel concurrently: R8 (lines 47 to 52) for the ITEM\_PICKED channel and R9 (lines 55 to 61) for the NEW\_ITEM channel. R9 also leverages an internal signal, NEW\_ITEM\_INTERN (line 58), to notice R1 that there is a new item on the Conveyor. In SystemGALS, signals defined in any position within a clock domain are visible to all Reactions in this clock domain. Similarly, R8 uses an internal signal, ITEM\_PICKED\_INTERN (line 50), to inform R1 that an item has been picked up.

Once R1 captures these two internal signals, it will change the value of the load variable accordingly, representing the current number of items on the Conveyor. The present statement (line 17) can check the status of a signal and execute the statements in the following block if the signal is present. The operation of load++ (line 20) and load-- (line 26) are C operations and are surrounded by a pair of {+ +}, which SystemGALS uses to introduce host languages in an anonymous data module. In a data module, SystemGALS can leverage any type, statement, and feature of the host language to perform computation operations. In this thesis, we use C as our host language to implement the software parts of data modules. Another data module (lines 29 to 35) in R1 checks if the load reaches the capacity. In our example, we assume that the capacity of the Conveyor is ten items (line 10). If the capacity is reached, the Data Module will access a CFV, isConveyorFull, defined in line 10 and change its value to true via the API of sgl\_SetCFV() (line 31). Then the Conveyor controller will emit a STOP\_LOADER signal (line 37) to inform the Loader controller to stop loading until the Mechanical Arm lifts one item from the Conveyor. Otherwise, it will emit a START\_LOADER signal.

| 1  | ConveyorController(                                     |

|----|---------------------------------------------------------|

| 2  | output signal START_LOADER, STOP_LOADER, MOVE_CONVRYOR; |

| 3  | input signal CONVEYOR_MOVING;                           |

| 4  | input int channel NEW_ITEM, ITEM_PICKED;                |

| 5  | output int channel ITEM_RECOGNIZED;                     |

| 6  | )->{                                                    |

| 7  | {// R1                                                  |

| 8  | cfv isConveyorFull = false;                             |

| 9  | int load = 0;                                           |

| 10 | int CAPACITY = 10;                                      |

| 11 | signal NEW_ITEM_INTERN;                                 |

| 12 | Signal ITEM_PICKED_INTERN;                              |

| 13 | abort(CONVEYOR_MOVING){                                 |

| 14 | sustain MOVE_CONVEYOR;                                  |

| 15 | }                                                       |

| 16 | loop{                                                   |

| 17 | present(NEW_ITEM_INTERN)                                |

| 18 | {                                                       |

| 19 | {+                                                      |

| 20 | load++;                                                 |

|    |                                                         |

**Motivating Example**

Figure 3-4. Conveyor controller SystemGALS implementation (1).

In the Conveyor controller, the reaction of R2 takes responsibility for detecting the type of an item by processing its picture. As shown in Figure 3-5, R2 contains four children reactions: R3, R4, R5, and R6. Each of these children reactions invokes a data module to achieve a subfunction of an image recognition algorithm sequentially. The output of the previous reaction is the input of the next reaction, and the previous reaction will also emit a signal to inform that the result is ready. Concretely, R3 will control the camera to take a picture of an item once the NEW\_ITEM\_INTERN signal is present. In our case, we call a function (line 11) to get a pointer pointing to an unsigned char array that stores the data of a BMP image to simulate the camera's

action. Then R4 will invoke a Binarization data module (line 17) to convert the colour image to a binary image. Next, the extractCharac data module (line 23) in R5 will extract a character vector from the binary image, which contains five float point numbers to describe features of the image. Finally, R6 will call the itemRecognize data module (line 29) to determine which type the item is and emit an integer signal with a value representing the type.

The statement of "dmcall Binarization (binary pixels, image)" (line 17) is an explicit method to call a named data module. Unlike the anonymous data module, a named data module (lines 35 to 37) can be defined outside the clock domains and with a specific name. The DataModule is a definition keyword, followed by the function name and the parameter list. In addition, R2 uses the types of Image (line 2), PixelArray (line 3), and CharacArray (line 4) defined in C struct to describe the data structure of a BMP image, a binary image, and a characteristic vector, respectively. Section 3.4 will illustrate the algorithm and the data module in detail.

| 1        | {// R2      |                                                           |

|----------|-------------|-----------------------------------------------------------|

| 2        |             | Image signal image;                                       |

| 3        |             | PixelArray signal binaryPixels;                           |

| 4        |             | CharacArray signal characArray;                           |

| 5        |             | int type;                                                 |

| 6        |             | Signal int ITEM_RECOGNIZED_INTERN;                        |

| 7        |             | loop{                                                     |

| 8        |             |                                                           |

| 9        |             | await (NEW_ITEM_INTERN);                                  |

| 10       |             | {//R3                                                     |

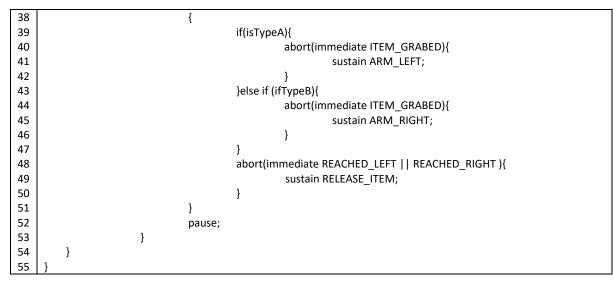

| 11       |             | dmcall getImage(image);                                   |