#### http://researchspace.auckland.ac.nz

#### ResearchSpace@Auckland

#### **Copyright Statement**

The digital copy of this thesis is protected by the Copyright Act 1994 (New Zealand).

This thesis may be consulted by you, provided you comply with the provisions of the Act and the following conditions of use:

- Any use you make of these documents or images must be for research or private study purposes only, and you may not make them available to any other person.

- Authors control the copyright of their thesis. You will recognise the author's right to be identified as the author of this thesis, and due acknowledgement will be made to the author where appropriate.

- You will obtain the author's permission before publishing any material from their thesis.

To request permissions please use the Feedback form on our webpage. <u>http://researchspace.auckland.ac.nz/feedback</u>

#### General copyright and disclaimer

In addition to the above conditions, authors give their consent for the digital copy of their work to be used subject to the conditions specified on the <u>Library Thesis Consent Form</u> and <u>Deposit Licence</u>.

#### **Note : Masters Theses**

The digital copy of a masters thesis is as submitted for examination and contains no corrections. The print copy, usually available in the University Library, may contain corrections made by hand, which have been requested by the supervisor.

## A STUDY OF HYBRID TRANSACTIONAL MEMORY

Fu'ad W. F. Al Tabba'

A thesis submitted in partial fulfillment of the requirements of Doctor of Philosophy in Computer Science, The University of Auckland, 2011.

## Abstract

The rise of multicore processors is driving programmers towards parallel programming. Traditional lock-based parallel programming, however, breaks abstraction, hinders composition, and is further complicated by issues such as deadlock, priority inversion, and lack of scalability. Transactional memory, a promising programming model inspired by database transactions, is gaining popularity as a way to overcome the drawbacks of lock-based programming and make it easier to write parallel programs.

Different methods have been proposed for supporting transactional memory. Hardware proposals, which modify a processor's existing hardware to support transactions, are either too complex, or cannot handle all types of workload. Software proposals, which do not require any hardware support beyond what is already present for parallel programming, are too slow. This thesis argues that transactional memory should be supported by a hybrid combination of hardware and software. By combining the two, transactional memory can offer the best of both hardware and software. To support this argument, this thesis presents my work on transactional memory, which spans the areas of hardware, software, and hybrid support.

This thesis presents NZSTM, the first nonblocking, object-based, software transactional memory that does not require indirection to access data in the common case. It also presents NZTM, a hybrid transactional memory that uses NZSTM as its software component. The evaluation presented shows that nonblocking support introduces little overhead compared with blocking algorithms, and that NZTM is competitive with pure hardware transactional memory.

Furthermore, this thesis investigates how to improve the performance of hardware transactional memory by using data speculation in transactions, and how to reduce transactional conflicts by decoupling them from cache coherence conflicts. Most hardware proposals do not distinguish between transactional conflicts and coherence conflicts, leading to false transactional conflicts. This thesis explains how to mitigate the effects of coherence conflicts by using value prediction in transactions. It also shows that coherence decoupling and value prediction in transactions complement each other, because they both speculate on data in ways that are infeasible in the absence of hardware transactional memory support.

# Dedication

To my parents, Samar and Wael, and to my partner in life, Anna, I couldn't have done it without you!

# Acknowledgements

They say that no man is an island, and good things come to those who wait. — Jon Bon Jovi

The wait is almost over; to that I am indebted to many people, whom without this thesis would not have been possible. I was very lucky to have three great advisors, formidable collaborators, and a patient wife, all of whom have contributed directly to this thesis.

First and foremost, I thank my advisor, Jim Goodman, for all his guidance and support throughout the years. Jim contributed to all levels of the work presented in this thesis, whether it is the high level discussion sessions where we would develop an idea (*or shoot it down*), debugging a model (*Jim's ability to identify a bug in my code based only on my description of it is uncanny*), and helping me write this thesis (*I will never forget what the subjunctive mood is*).

I am also very grateful to Mark Moir, my unofficial co-advisor. Mark's contributions were instrumental to the ideas presented in this thesis, particularly to NZSTM and NZTM. Without Mark, NZTM would not have had its snazzy name! I learned a lot from Mark on how to write and publish a research paper. I am also grateful for Mark's comments on this thesis.

I thank Gill Dobbie, my co-advisor, for her help and advice, for the thought-provoking discussions we have had, and for her comments on this thesis.

James Wang, my first friend in the trenches, I thank him for showing me the ropes when I started out. James set up the original simulation environment, which I continued using throughout my work. The (*often heated*) discussions James and I have had were very helpful in developing many of the topics presented in this thesis.

To Andrew Hay, I am grateful for our collaboration, which resulted in the work on value prediction in transactions. I am not sure if either of us will miss those long hours of working on (*banging our heads against*) the simulator, or the waiting for and graphing all the results — only to discover that we need to redo the whole thing! I am also grateful to Andrew for his comments on this thesis.

I am very grateful to the awesome team at Sun Labs at Oracle for their valuable comments and for their help on the ATMTP simulator and the Rock machine: Kevin Moore, Dave Dice, Marek Olszewski, and especially to Dan Nussbaum for his help and patience in answering every one of my missives. I thank Doug Burger, Guri Sohi, and Kevin Moore for their feedback on the work on value prediction. I especially thank Doug for his suggestions on how to extend that work to enable eager conflict detection.

I am grateful to Virtutech for the Simics simulator license, and to Sun Labs at Oracle for access to the Rock machine and for the Niagara machine donated to the University of Auckland. I am also very grateful to Education New Zealand and the University of Auckland for funding my research.

Last but not least, I thank my lovely wife, Anna Ogenblad, for actually reading and commenting on my whole thesis. Anna does not have a computer science background, so I can only imagine how boring it must have been — she would always read it right before sleeping... Jag älskar dig Anna!

# Contents

| Ał | Abstract            |                                                         |      |  |  |  |  |  |  |

|----|---------------------|---------------------------------------------------------|------|--|--|--|--|--|--|

| De | edicat              | ion                                                     | v    |  |  |  |  |  |  |

| Ac | Acknowledgements vi |                                                         |      |  |  |  |  |  |  |

| Li | st of I             | Figures                                                 | xi   |  |  |  |  |  |  |

| Li | st of ]             | Fables                                                  | xiii |  |  |  |  |  |  |

| Gl | ossar               | y                                                       | XV   |  |  |  |  |  |  |

| 1  | Intr                | oduction                                                | 1    |  |  |  |  |  |  |

|    | 1.1                 | Motivation: Transactions in the Multicore Age           | 2    |  |  |  |  |  |  |

|    | 1.2                 | Thesis Organization and Summary of Contributions        | 4    |  |  |  |  |  |  |

| 2  | The                 | Challenges of Parallelism and the Transactional Promise | 7    |  |  |  |  |  |  |

|    | 2.1                 | The Rise of Multicores                                  | 7    |  |  |  |  |  |  |

|    | 2.2                 | The Cache Coherence Problem                             | 9    |  |  |  |  |  |  |

|    | 2.3                 | Synchronization, Mutual Exclusion, and Locks            | 11   |  |  |  |  |  |  |

|    | 2.4                 | What is Transactional Memory?                           | 14   |  |  |  |  |  |  |

|    | 2.5                 | Transactional Memory Design Space                       | 16   |  |  |  |  |  |  |

|    | 2.6                 | Evaluating Transactional Memory                         | 21   |  |  |  |  |  |  |

|    | 2.7                 | The Current State of Transactional Memory               | 22   |  |  |  |  |  |  |

|    | 2.8                 | The Rock Processor and the ATMTP Simulator              | 23   |  |  |  |  |  |  |

|    | 2.9                 | Other Challenges in Parallel Programming                | 28   |  |  |  |  |  |  |

| 3  | A C                 | ase for Hybrid Transactional Memory                     | 33   |  |  |  |  |  |  |

|    | 3.1                 | A Case for Transactional Memory                         | 34   |  |  |  |  |  |  |

|    | 3.2                 | Making a Case for Hybrid Transactional Memory           | 39   |  |  |  |  |  |  |

|    | 3.3                 | Concluding Remarks                                      | 50   |  |  |  |  |  |  |

| 4  | Non              | blocking Zero-indirection Software Transactional Memory   | 53  |  |  |  |  |  |

|----|------------------|-----------------------------------------------------------|-----|--|--|--|--|--|

|    | 4.1              | The NZSTM Algorithm                                       | 57  |  |  |  |  |  |

|    | 4.2              | Correctness Evaluation                                    | 72  |  |  |  |  |  |

|    | 4.3              | Performance Evaluation                                    | 75  |  |  |  |  |  |

|    | 4.4              | Concluding Remarks                                        | 79  |  |  |  |  |  |

| 5  | Hyb              | rid Nonblocking Zero-indirection Transactional Memory     | 81  |  |  |  |  |  |

|    | 5.1              | The Design of NZTM                                        | 82  |  |  |  |  |  |

|    | 5.2              | Performance Evaluation                                    | 88  |  |  |  |  |  |

|    | 5.3              | Concluding Remarks                                        | 99  |  |  |  |  |  |

| 6  | Para             | allel Python                                              | 101 |  |  |  |  |  |

|    | 6.1              | Concurrent CPython                                        | 103 |  |  |  |  |  |

|    | 6.2              | Evaluation                                                | 106 |  |  |  |  |  |

|    | 6.3              | Design Alternatives                                       | 109 |  |  |  |  |  |

|    | 6.4              | Related Work                                              | 110 |  |  |  |  |  |

|    | 6.5              | Concluding Remarks                                        | 111 |  |  |  |  |  |

| 7  | Trar             | nsactional Conflict Decoupling and Value Prediction       | 113 |  |  |  |  |  |

|    | 7.1              | The False Sharing Problem                                 | 114 |  |  |  |  |  |

|    | 7.2              | Coherence Decoupling and Value Prediction in Transactions | 116 |  |  |  |  |  |

|    | 7.3              | DPTM Description                                          | 118 |  |  |  |  |  |

|    | 7.4              | Evaluation                                                | 125 |  |  |  |  |  |

|    | 7.5              | Related Work                                              | 136 |  |  |  |  |  |

|    | 7.6              | Concluding Remarks                                        | 137 |  |  |  |  |  |

| 8  | Con              | clusion                                                   | 139 |  |  |  |  |  |

| A  | Dyna             | amic Software Transactional Memory                        | 143 |  |  |  |  |  |

|    |                  | DSTM Data Structures                                      |     |  |  |  |  |  |

|    | A.2              | DSTM Algorithm                                            | 145 |  |  |  |  |  |

| B  | NZS              | TM Promela Model                                          | 147 |  |  |  |  |  |

| Bi | Bibliography 181 |                                                           |     |  |  |  |  |  |

# **List of Figures**

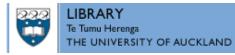

| 1.1 | Intel processor trends                                                       |

|-----|------------------------------------------------------------------------------|

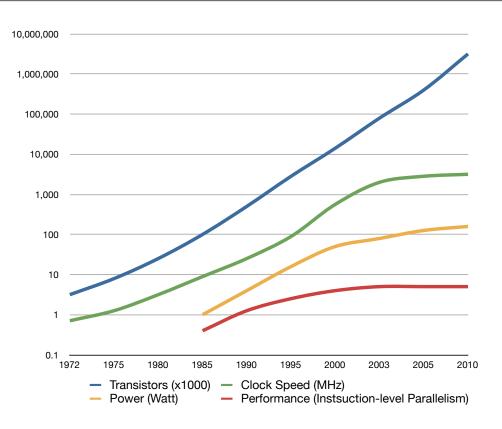

| 2.1 | An example of cache coherence at work                                        |

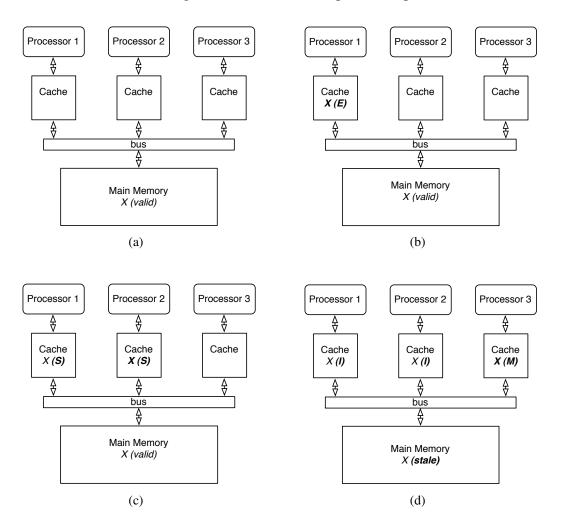

| 2.2 | Rock processor organization                                                  |

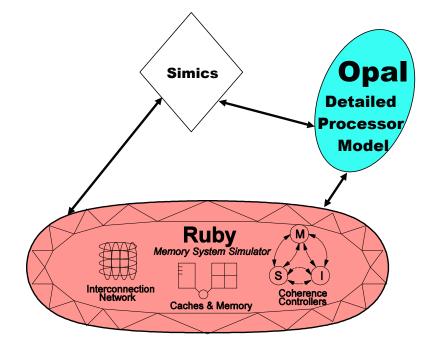

| 2.3 | Wisconsin GEMS Architecture                                                  |

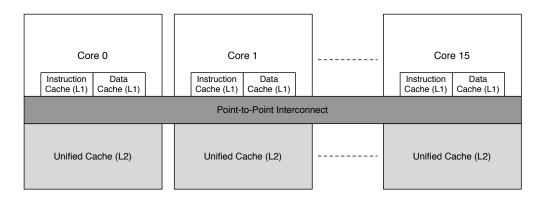

| 2.4 | ATMTP processor organization model                                           |

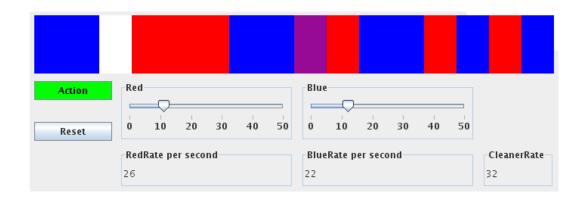

| 3.1 | University of Texas Study Screenshot                                         |

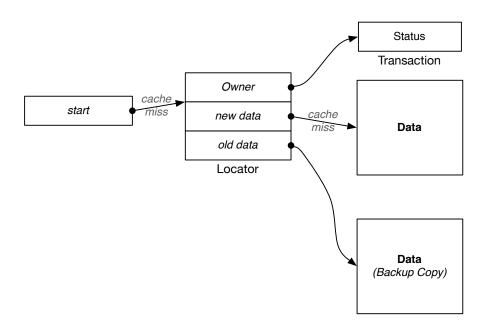

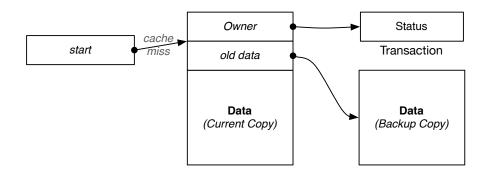

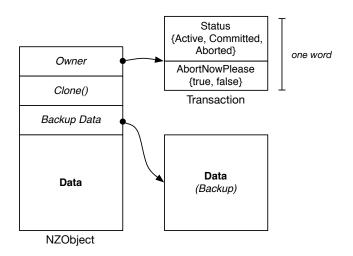

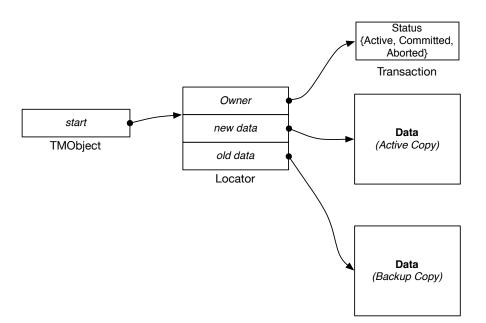

| 4.1 | The structure of DSTM's main transactional object                            |

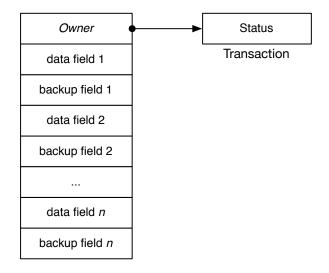

| 4.2 | The structure of RSTM's main transactional object                            |

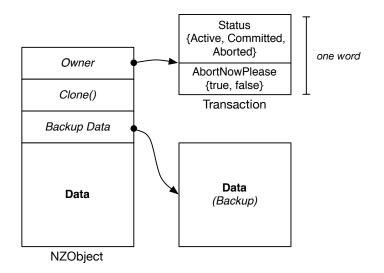

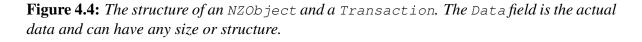

| 4.3 | The structure of the DSTM2 Shadow Factory main transactional object 55       |

| 4.4 | The structure of NZSTM's main transactional object                           |

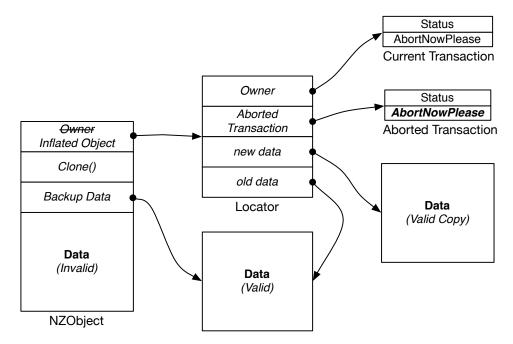

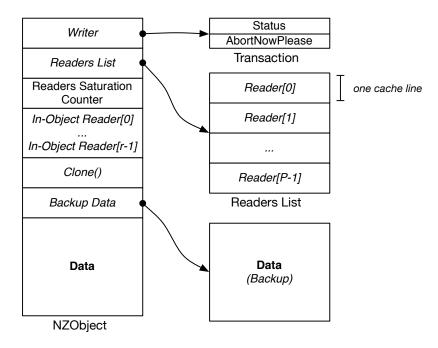

| 4.5 | The structure of an inflated NZSTM object                                    |

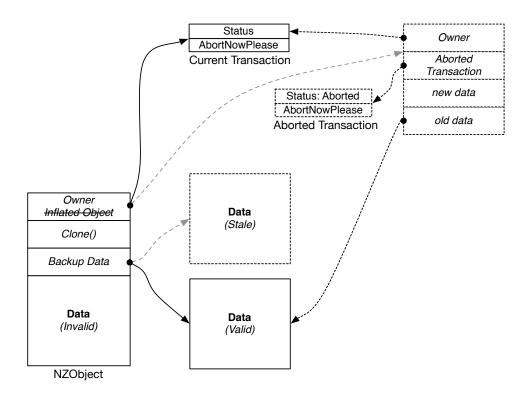

| 4.6 | A successfully deflated NZObject immediately after deflation 65              |

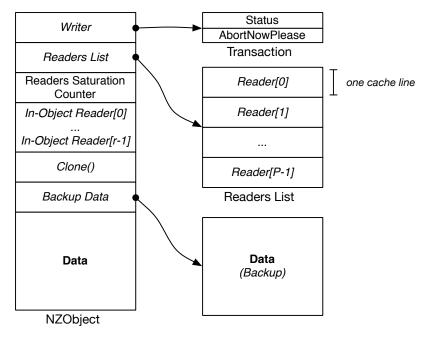

| 4.7 | An NZObject using the proposed visible readers scheme                        |

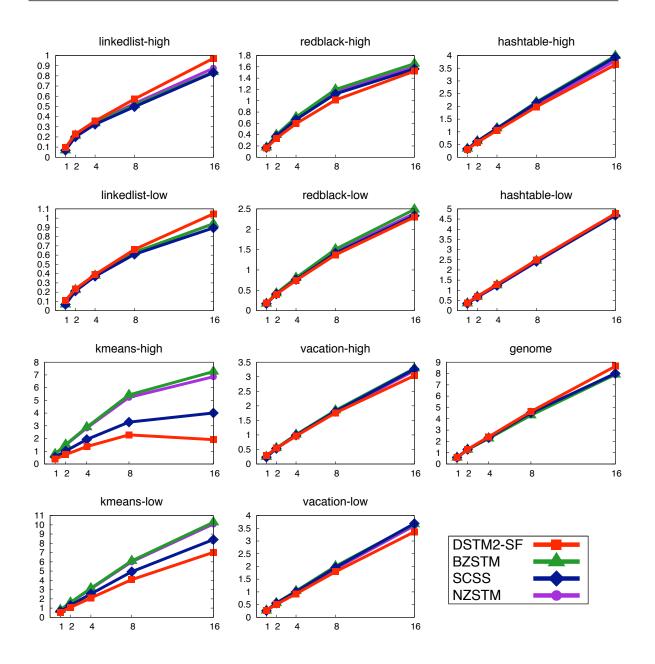

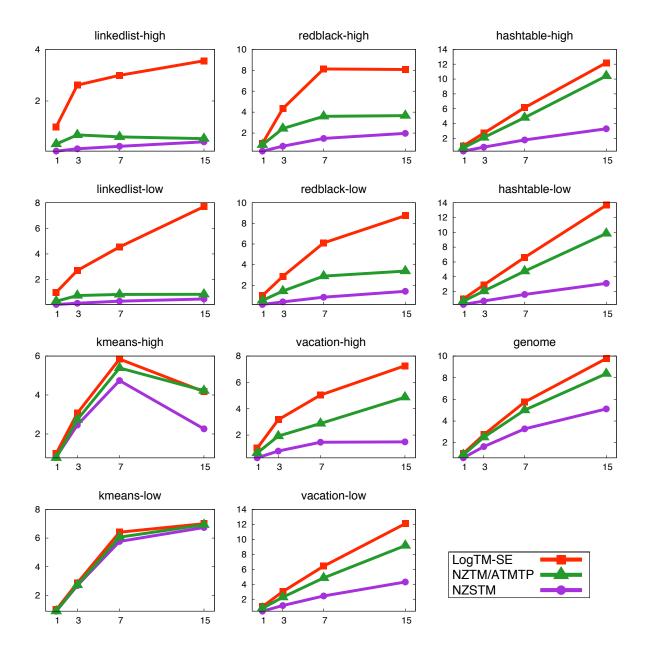

| 4.8 | The results of running the NZSTM benchmarks on Rock                          |

| 5.1 | The structure of NZTM's main transactional object                            |

| 5.2 | An NZObject using the proposed visible readers scheme                        |

| 5.3 | Results of running the NZTM benchmarks on the simulator                      |

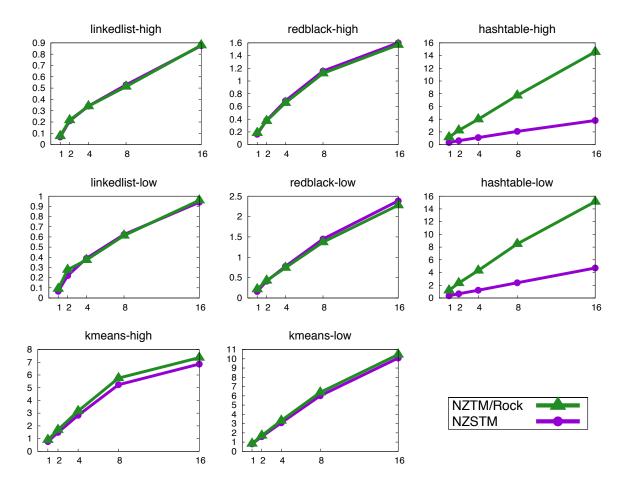

| 5.4 | Results of running the NZTM benchmarks on the Rock machine 96                |

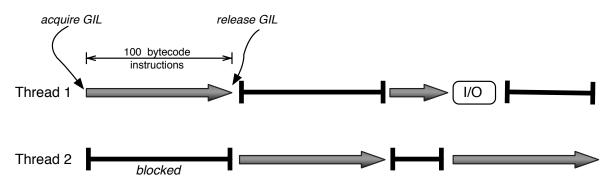

| 6.1 | An example of running two concurrent threads in CPython                      |

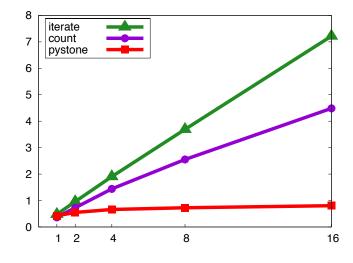

| 6.2 | Results of running the CPython benchmarks on the Rock machine 108            |

| 7.1 | The effect of a single instance of false sharing in transactional memory 115 |

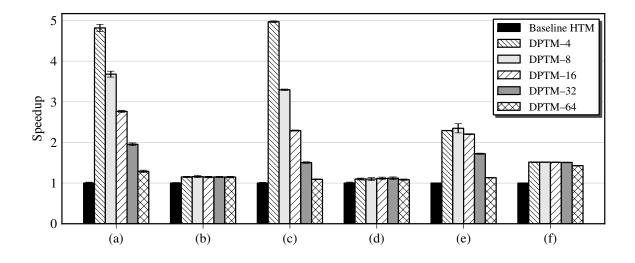

| 7.2 | Results of running the <i>SharingPatterns</i> benchmarks                     |

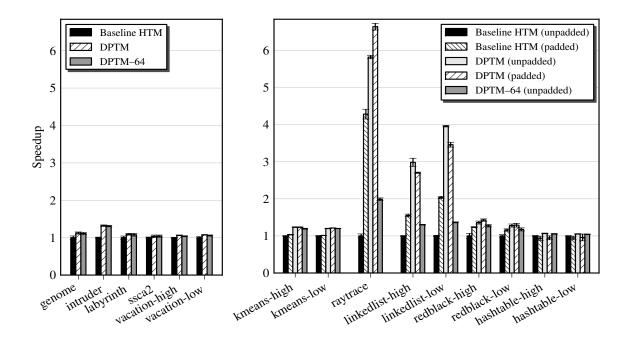

| 7.3 | Results of running the DPTM benchmarks, padded and unpadded 130              |

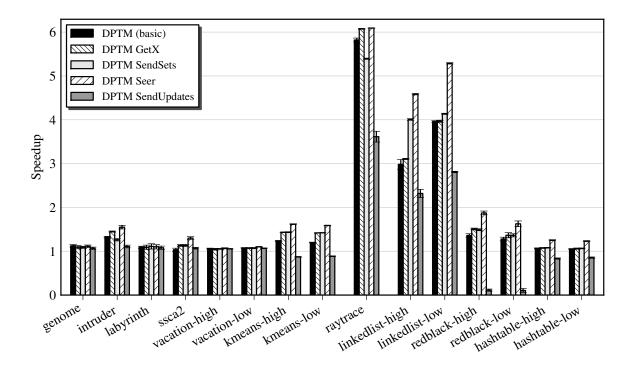

| 7.4 | The speedup of the DPTM design alternatives                                  |

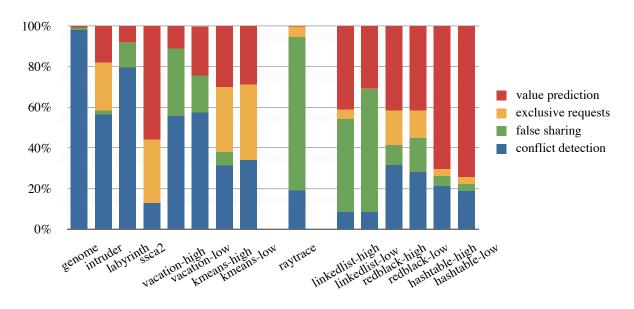

| 7.5 | DPTM performance breakdown                                                   |

| A.1 | The structure of DSTM's main transactional object                            |

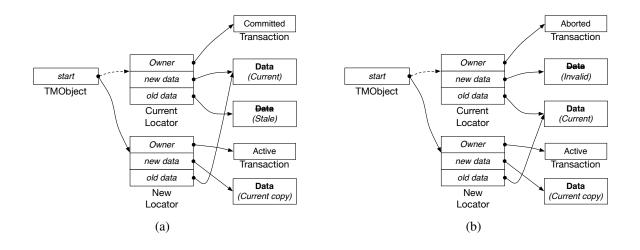

| A.2 | A DSTM transaction acquiring an object . |  | • | • |  |  |  | • |  |  |  | 14. | 5 |

|-----|------------------------------------------|--|---|---|--|--|--|---|--|--|--|-----|---|

|     |                                          |  |   |   |  |  |  |   |  |  |  |     |   |

# **List of Tables**

| 3.1 | Sources of overhead in NZSTM                                                   |

|-----|--------------------------------------------------------------------------------|

| 4.1 | STAMP parameters used in the NZSTM evaluation                                  |

| 4.2 | Qualitative summary of the NZSTM benchmarks' characteristics                   |

| 5.1 | Course of action when a hardware NZTM transaction aborts                       |

| 5.2 | Simulated machine configuration for NZTM                                       |

| 5.3 | STAMP parameters used in the NZTM evaluation                                   |

| 5.4 | Qualitative summary of the NZTM benchmarks' characteristics                    |

| 5.5 | Hardware transaction commit rate on Rock in the absence of contention 95       |

| 6.1 | Concurrent CPython slowdown relative to a single unmodified CPython thread 107 |

| 7.1 | DPTM Simulated machine configuration                                           |

| 7.2 | STAMP parameters used in the DPTM evaluation                                   |

| 7.3 | Qualitative summary of the DPTM benchmarks' characteristics                    |

| 7.4 | Breakdown of DPTM abort causes                                                 |

# Glossary

- **ATMTP:** Adaptive Transactional Memory Test Platform, a simulator that models Rock-like hardware transactional memory (page 23)

- **Compare&Swap:** An atomic processor instruction that reads a memory location, and if the value at that location matches the value the instruction expects to find, it replaces it with a new value, indicating whether the operation was successful (page 13)

- **CPS:** Checkpoint Status register, a register in Rock that provides feedback on what caused a hardware transaction to abort (page 23)

- **DPTM:** Decoupling and Prediction Transactional Memory, a best-effort hardware transactional memory proposal that mitigates the effects of false conflicts in transactions (page 118)

- **DSTM:** Dynamic Software Transactional Memory, an early software transactional memory proposal (page 143)

- **GEMS:** General Execution-driven Multiprocessor Simulator, an extension to the Simics simulator that allows detailed architectural timing simulation, as well as the modeling of different hardware transactional memory proposals (page 26)

- **GIL:** Global Interpreter Lock, a mutual exclusion lock used in the de-facto standard Python interpreter implementation (page 101)

- HTM: Hardware Transactional Memory (page 17)

- NZSTM: Nonblocking Zero-indirection Software Transactional Memory (page 53)

- NZTM: A hybrid Nonblocking Zero-indirection Transactional Memory (page 81)

- Promela: A C-like language that describes models to check using Spin (page 73)

- **Rock:** A multithreaded, multicore, SPARC processor developed at Sun Microsystems, and the first commercial processor designed with hardware transactional memory support (page 23)

- **SCSS:** Single-Compare Single-Store, an atomic operation that modifies a location with a new given value only if another location's value matches an expected value (page 67)

- **Simics:** A full-system functional simulator that allows for detailed timing simulation using extensions (page 26)

- **Spin:** A mechanical verification system designed for the formal verification of high-level models for systems of concurrently executing processes (page 73)

- **STM:** Software Transactional Memory (page 19)

- **TLB:** Translation Lookaside Buffer, a cache for page table entries that speeds up virtual address translation (page 45)

# **Chapter 1**

## Introduction

The distant threat has come to pass. For 30 years or more, pundits have claimed that parallel computers are the inexorable next step in the evolution of computers and have warned us to learn to program these machines.

- Larus and Rajwar [2007]

The age of parallel computing is finally here. Although Moore's law is still driving the number of transistors higher, the actual improvement in processor design is slowing down. Processor manufacturers find themselves with the easier option of using these additional transistors to add more cores to a microprocessor, rather than build a bigger, more powerful, processor. This trend is pushing programmers towards an unfamiliar, parallel, programming paradigm.

Parallel programming is more complex than sequential programming. Parallel programming requires programmers to be able to manage all the available computing resources, and reason carefully about possible interactions of their programs when running concurrently. If programmers do not carefully consider these interactions, their programs' performance and even correctness — could suffer.

Transactional memory [Herlihy and Moss, 1993] is one proposal that promises to make it easier to reason about parallel programs. Transactional memory is a programming model that provides a level of abstraction on top of critical sections by using transactions, a concept borrowed from the database community. Transactions promise to make it easier to reason about each critical section individually, without having to worry about the possible interactions between critical sections.

Support for transactional memory has been proposed in software, hardware, and as a hybrid combination of the two. Software support is more flexible than hardware support, but is significantly slower so far. Hardware support is fast; however, implementing a flexible hardware solution that can support the same workloads as software is expensive, or altogether infeasible.

This thesis argues that the hybrid approach is the most appropriate for the transactional model to succeed as a programming model. By combining both software and hardware support, the hybrid approach can overcome their individual weaknesses.

This chapter introduces the problems that led to the development of transactional memory as a programming model, and presents my contributions and the outline of this thesis.

### **1.1** Motivation: Transactions in the Multicore Age

To pull a bigger wagon, it is easier to add more oxen than to grow a gigantic ox. — Gropp, Lusk, and Skjellum [1999]

In 1965, Gordon Moore published his article introducing what is now known as *Moore's law*. Moore's law predicted that the amount of complexity, or number of transistors, that can be used inexpensively in a chip will double every two years. Because this would double the number of transistors processor designers have at their disposal, Moore's law implies that processor performance would also improve at an exponential rate [Joy, 1995].

For the forty years following Moore's initial prediction, performance has indeed kept up with the increase in the number of transistors on a chip [Hennessy and Patterson, 2006]. More recently, however, improvements in performance seem to be slowing down [Sutter, 2005].

Figure 1.1 presents a history of the trends in Intel processors. It shows the trends in the number of transistors, the clock speed, power consumption, and performance as measured by the number of instruction running per clock cycle. The figure shows that, since 2003, the exponential growth in single-core performance has all but stopped; the same is true for the increase in clock speed — despite the number of transistor still growing exponentially.

Power consumption is one factor that accounts for the change in the performance trend: as the clock speed increases, power consumption also increases, making processors that operate at high frequencies difficult to cool down and more expensive to operate [Hennessy and Patterson, 2006]. Another problem is that as the field of processor design matures, processor designers find it increasingly difficult to use the additional transistors to improve the performance of a single processor. The economics of replication make it more appealing to use these additional transistors to create multiple processors, e.g., by adding more cores to the same chip. Assuming programmers use these additional cores efficiently, adding cores would be an easy solution that improves performance without increasing the processor clock speed.

Processor manufacturers have embraced the concept of adding multiple cores [Geer, 2005; Koch, 2005]. Today, virtually all desktop and laptop computers have at least two cores, gaming consoles have up to eight cores on each processor [Chen, Raghavan, Dale, and Iwata, 2007], and Intel is warning us that future processors would have thousands of cores on a single chip [Ghuloum, 2008]!

Figure 1.1: Intel processor trends [adapted from Sutter, 2005]

Using multiple cores, however, does not automatically improve a program's performance. Fred Brooks [1995], who managed the development of IBM's OS/360, noted that "the bearing of a child takes nine months, no matter how many women are assigned", similarly, certain programs are inherently incapable of running in parallel. Even for programs that can run in parallel, exploiting the underlying parallelism is not easy: there are issues with scheduling the program's tasks, removing the bottlenecks that slow down a parallel program, and protecting a program's critical sections and shared data.

*Transactional memory* [Herlihy and Moss, 1993] is a programming model that promises to make it easier to reason about accesses to shared memory by creating an abstraction similar to database transactions. A *transaction* is defined as a "sequence of actions that appears indivisible and instantaneous to an outside observer" [Larus and Rajwar, 2007]. With transactional memory, programmers do not need to worry about how to synchronize accesses to shared data, they only need to protect their shared data and critical sections using transactions, leaving the details to the underlying implementation.

There are many different proposals for supporting transactional memory. These proposals can be broadly classified into three categories: hardware transactional memory [Herlihy and Moss, 1993], software transactional memory [Shavit and Touitou, 1995], and hybrid transactional memory, which combines both hardware and software support [Lie, 2004; Moir, 2005].

Hardware transactional memory has the advantage of speed, because hardware is particularly suited for performing tasks in parallel, as well as hiding the latency of operations using speculation. On the other hand, hardware support is expensive and more risky to implement: this new hardware must be designed with consideration to how it might interact with existing processor components, and transistors that could have been used for a different purpose, such as adding more cores, must now be dedicated to transactional memory. Moreover, if the transactional model is supported only by hardware, it means that transactional memory cannot be used on existing systems today, and all its benefits would be limited to those using the new hardware.

Software transactional memory resolves most of these issues, because software can be designed to work on existing systems without requiring special hardware support — and is therefore less expensive. However, software proposals, so far, are significantly slower than their hardware counterpart, slower by at least an integer factor or even by an order of magnitude.

Hybrid transactional memory aims to be the best of both: hybrid proposals use simple hardware support for speed, when available, while relying on software for cases that would complicate hardware design, or when hardware support is not available altogether. With the hybrid approach, transactional memory implementations can run on existing systems today, and improve incrementally as their underlying hardware or software components improve.

### **1.2 Thesis Organization and Summary of Contributions**

This thesis argues for hybrid transactional memory by drawing on work by various researchers as well as my own experiences. These experiences span three different levels of support for transactional memory: hardware, software, and putting the two together in a hybrid system. In the course of working on this thesis, I have developed novel software and hybrid transactional memory proposals. I have experimented with using a prototype of Sun's Rock processor, one of the few existing hardware transactional memory implementations. I have also investigated possible enhancements to Rock's hardware support by modeling them on a simulator. This thesis reports on these experiences.

Chapter 2 presents some of the history and background of transactional memory. It also introduces most of the terms and concepts used throughout this thesis.

Chapter 3 makes a case for hybrid transactional memory by discussing some of the related work in this area. It starts by making the case for the transactional model in general, then it discusses the benefits and drawbacks of hardware and software support, and explains how hybrid support can leverage both hardware and software to make transactional memory feasible today. Chapters 4 to 7 present a topdown discussion of my work in the area of transactional memory, starting with software, moving to hybrid, then the use of an actual hardware implementation, and finally, by suggesting modifications to improve the hardware implementation.

Chapter 4 introduces NZSTM, the first non-blocking, zero-indirection, object-based software transactional memory. It explains the design philosophy of NZSTM, discusses the algorithm, and shows how to exploit hardware support, if present, to greatly simplify the NZSTM algorithm. This chapter presents a correctness and performance evaluation of NZSTM, and shows that NZSTM's performance is competitive with algorithms designed to be blocking.

Chapter 5 introduces NZTM, a nonblocking hybrid transactional memory that can exploit hardware support, when available, and fall back gracefully on NZSTM when hardware support is not available or sufficient. This chapter presents a performance evaluation of NZTM using a simulator and using Sun's Rock processor, which offers limited hardware transactional memory support. The evaluation shows that NZTM performs significantly better than pure software proposals, and that it is competitive with pure hardware proposals.

Chapter 6 reports on my experiences of using Sun's Rock processor to parallelize Python using hardware transactional memory. This chapter explains how to make some workloads in Python, which by default is not concurrent, scale with additional cores. It also discusses the problems encountered in the process.

Chapter 7 investigates how to mitigate the effects of false conflicts in hardware transactional memory by using data speculation, focusing on false conflicts caused by false sharing at the cache line level. It explains why false conflicts are particularly detrimental in a transactional memory environment, and presents a solution that mitigates most of their effects.

Finally, Chapter 8 concludes the thesis.

## Chapter 2

# The Challenges of Parallelism and the Transactional Promise

This chapter presents some of the background relevant to this thesis. It discusses some of the challenges in the move towards concurrency, both at the hardware and software level. It also introduces the concept of transactional memory, and discusses some of the problems transactional memory addresses and the promises transactional memory makes.

### 2.1 The Rise of Multicores

*Multiprocessing*, and specifically *shared memory multiprocessing*, where two or more processors are connected to a single shared memory, has existed at least since the early 1960s, with the introduction of the Burroughs mainframe computers [McCullough, Speierman, and Zurcher, 1965]. The main motivator then was the economics of replication: to boost performance, it costs less to create multiple copies of the same processor and connect them than it costs to design a single fast processor. Multiprocessing works well for applications that lend themselves to being divided into subsections and having their workload distributed over multiple processors [Hennessy and Patterson, 2006], such as many scientific applications. For other types of applications, it is not obvious how their workloads can be divided to run in parallel on multiple processors.

For general purpose computing, particularly for desktop computers, there has not been a pressing need to exploit parallelism. Because of Moore's law and the ingenuity of processor designers, processor manufacturers had the designs and the transistors they needed to produce processors that are exponentially faster every year. Therefore, the advancements in single processor computers have, until recently, inhibited research and investment in multiprocessing.

Moore's law still drives processor manufacturing today; however, processor designers are having difficulties exploiting Moore's law to make a single processor faster. This is mainly because of issues such as the increase in power consumption, and the lack of new ideas that could use additional transistors to speed up a single processor [Sutter, 2005; Hennessy and Patterson, 2006]. Therefore, processor manufacturers use these transistors to create multiple processors on a single chip, which are known as *multicores*. IBM started this trend with the release of the dual-core POWER4 processor in 2001 [Hennessy and Patterson, 2006]. In 2005, AMD and Intel both released their first dual core processor, an important milestone, because it is these companies' processors that dominate the ubiquitous personal computing market.

Today, Intel's Core i7, a processor meant for desktop and laptop computers, can have up to six cores [Smith, 2009]. The Sony Playstation 3, a gaming console, has an eight core STI Cell processor [Chen et al., 2007]. According to Intel, this trend will continue and programmers should start considering programming for many more cores in the near future [Ghuloum, 2008].

Even though parallel programming has been studied for over 40 years, writing parallel programs is still difficult. There are many factors that complicate writing parallel programs, such as finding algorithms that can be separated into parallel tasks, and balancing the work-load among the available processors. The focus of my research, however, is on the difficulties involved in communicating and managing shared data between different processors.

When a program runs in parallel on different processors, the different threads running the same program need to communicate — even if it is just to inform each other that a certain job is completed. Threads can communicate by sending messages, this is known as the *message passing* model; or they can communicate by accessing and modifying the same shared memory, this is known as the *shared memory* model [Hennessy and Patterson, 2006]. The shared memory model has the advantage of using the same interface that programs running on single processors already use; therefore, programs require fewer modifications to use this model. The alternative, message passing, requires a different programming paradigm; programs need to be rewritten, and programmers must learn this new programming paradigm.

To complicate things further, shared memory is often supported, at the hardware level, by a cache coherence protocol that operates by sending messages, whereas the message passing model is sometimes implemented using shared memory. I do not make any judgements on which model is better; but because the shared memory model is the prevalent model today [Hennessy and Patterson, 2006], it is the focus of this thesis.

Maintaining the shared memory model poses certain challenges. At the hardware level, one such challenge is cache coherence, which is responsible for ensuring that each processor's local cache memory contains a faithful representation of what is in memory across all processors. At the software level, the challenge is that accesses to shared resources, and shared memory in particular, must be protected and synchronized. This is necessary to prevent concurrent accesses to these shared resources from interfering with each other, slowing each other down, or corrupting data altogether.

The next two sections discuss some of the challenges, at the hardware and the software levels, that are particularly relevant to this thesis.

### 2.2 The Cache Coherence Problem

Cache memory is a small, fast, memory that reduces the average memory access time and bandwidth requirements by taking advantage of locality in memory accesses. Cache memory works by storing a local copy of locations that the processor is likely to access soon — thereby saving the processor from having to access main memory directly. Accessing main memory can be a few orders of magnitude slower than accessing the local cache, and having to go to main memory for every access increases the bandwidth requirements on the interconnect between processors and memory [Goodman, 1983].

When there are multiple processors, each with its own local cache and sharing the same main memory, the problem is how does the system guarantee that each processor's local copy is consistent with copies in other processors as well as with main memory?

The solution to this problem is the domain of *cache coherence protocols*. Coherence protocols are responsible for ensuring that all processors see a consistent view of memory in a manner transparent to the higher levels of the system. For processors' local cache data to be consistent, coherence protocols must detect and resolve potentially conflicting accesses to the same *cache line*. A cache line is a block of memory, typically ranging in size from 64 to 256 bytes.

A conflict occurs when one processor tries to modify a cache line that is being read by one or more other processors. Coherence protocols typically allow more than one processor to read the same cache line, but only one processor can access a cache line at a time if it intends to modify it.

To illustrate how cache coherence works, the following describes a cache coherence protocol by example of a typical MESI coherence protocol [Goodman, 1983; Papamarcos and Patel, 1984; Sweazey and Smith, 1986] — named after the states that a cache line can be in. This type of protocol assigns a state to each cache line, which can be one of the following.

- Modified (M): The cache line data has been modified and memory must (eventually) be updated with the new value. No other processor has the current data value of this line or more accurately, no other processor has *permission* to access the data.

- **Exclusive (E):** The cache line data is valid and has not been modified. The processor has permission to either modify it at any time, or to share it with any other processor. No other processor has permission to access the data value of this line.

- **Shared** (S): The cache line data is valid and has not been modified. Other processors may also have a valid (*Shared*) copy of the same cache line, but no processor has permission to modify the line.

- **Invalid** (I): The cache line data is no longer valid, i.e., it is *stale*. The processor must request the data (and implicitly, permission) before it can read or modify it.

- **Not Present (NP):** This is not an explicit state, but is implied by the absence of the cache line address in any state. In practice, most cache coherence protocols treat this state the same way as an invalid state.

In such a protocol, processors, at least conceptually, share a common bus to access main memory, and issue their requests by broadcasting them on the bus. The protocol maintains the correct state by snooping the bus to intercept any requests made by other processors, hence why this is known as a *snooping* protocol [Goodman, 1983; Frank and Inselberg, 1984; Thacker and Stewart, 1987]. Figure 2.1 shows an example of this protocol in action.

Figure 2.1: An example of cache coherence at work

In the example in Figure 2.1, initially (a), none of the processors have the line associated with cache line *X* in their cache; therefore, it is in the implicit *Not Present* state. Processor 1 requests to read cache line *X*, and acquires the cache line in an *Exclusive* state, because no other processor has a copy of the line (b). Next, processor 2 requests a copy for reading, and

obtains it in a *Shared* state; processor 1, seeing processor 2's request for reading, downgrades the state of its cache line to *Shared* (c). Processor 3 decides to write to X; it requests to modify the line. Processors 1 and 2 detect the conflict with processor 3, and invalidate their own copies of cache line X upon seeing processor 3's request. When processor 3 receives its exclusive copy, it applies its modifications, and therefore has the cache line in a *Modified* state (d).

Cache coherence protocols do not necessarily require a shared common bus, as in the example above. Coherence protocols can also be implemented as *directory-based* protocols [Tang, 1976; Censier and Feautrier, 1978], where the sharing state of a cache line is maintained at a common location, the *directory*. Processors request permission to access cache lines from the directory; in turn, the directory is responsible for informing processors about potential conflicts [Hennessy and Patterson, 2006].

Although cache coherence is not the only challenge at the hardware level in designing multiprocessors, it is particularly important because cache coherence is directly responsible for maintaining the shared memory abstraction. Any compromises in cache coherence would lead to leaks in the shared memory model abstraction, and could corrupt the data in memory.

Cache coherence is essentially about managing a shared resource at the hardware level, the resource being memory. With the shared memory abstraction in place, it is the operating system's and programmers' responsibility to manage the sharing of objects at the software level.

### 2.3 Synchronization, Mutual Exclusion, and Locks

When using the shared memory model, programmers are responsible for ensuring that, when their programs share data, concurrent accesses to the shared data are correct. Correctness depends on the program, but typically means that a shared data structure, or a group of related shared structures, must not be accessed in a *conflicting* manner by more than one thread at a time: multiple threads can simultaneously read the same data, but only one thread at a time can access the data to modify it.

The part of the program that accesses shared resources where conflicts might occur is known as a *critical section*. To ensure that the shared resources in critical sections are protected from conflicts, programmers often rely on *mutual exclusion* mechanisms [Dijkstra, 1965; Hoare, 1974; Lamport, 1974; Peterson, 1981]. Mutual exclusion mechanisms protect against conflicts by ensuring that no more than one thread can simultaneously enter the same critical section and access the same shared data.

One common method of ensuring mutual exclusion is by using *locks*. A lock is a data structure typically associated with a certain critical section or a specific shared data structure. A thread must acquire a lock before it can execute the critical section, or before it can access the shared data the lock protects. Each lock may not be owned by more than one thread at

a time; if a thread wants to acquire a lock owned by another thread, it must *block*, i.e., wait, until the lock is released.

Locks, and methods of protecting critical sections by mutual exclusion in general, have existed for over four decades. In a sense, they are tried-and-true methods. However, there are many problems associated with using locks that could compromise correctness, performance, and reliability.

One of the problems with locks, in terms of correctness, is the possibility of *deadlock*. Deadlock occurs when different threads try to acquire the same locks (or resources in general) in a different order, so each thread is waiting for another thread to release its lock before any one can proceed [Coffman, Elphick, and Shoshani, 1971]. This results in none of the threads making any progress, and often leads to the whole program — or even the whole system if the operating system is involved — coming to a halt.

Programmers can avoid deadlock by ensuring that different threads always acquire locks in the same order. This, however, adds complexity to a program, and requires programmers to be aware of instances of where locks might be used and the correct order of acquiring them — all of which makes parallel programming even more difficult. Alternatively, programmers can try to detect a deadlock, and try to recover from a deadlock once detected, which also adds complexity.

Programmers can reduce the likelihood of deadlock by using fewer locks with *coarser* granularity, where each lock is responsible for protecting bigger or more critical sections. At one extreme, programmers could use a *single global lock* that protects *all* critical sections; this would ensure that deadlock cannot occur and simplifies reasoning about the program. However, because locks are mutually exclusive, critical sections protected by the same lock cannot run in parallel, which could negate the benefits of multiprocessing.

Another problem with locks is that they are *blocking*: once a thread acquires a lock, it cannot be forced to release the lock, and there is no guarantee that the thread will release the lock within a bounded period of time. This leads to two more problems: *priority inversion* and lack of *fault tolerance*.

Priority inversion is when a low priority thread acquires a lock, and then a higher priority thread needs to acquire the same lock, but is unable to do so. If the low priority thread releases the lock as soon as it is aware of the higher priority thread, the problem is not severe. If the low priority thread is oblivious to the higher priority thread, and delays the release of the lock, the problem could manifest in the form of the system becoming unresponsive.

A blocking system is also less fault-tolerant. If a thread acquires a lock, modifies data, and crashes before it completes its modifications, then there is no reliable way of releasing the lock and ensuring that the modifications are consistent, unless the system tracks the modifications every thread makes in a critical section. In practice, what often happens is that the faulty thread corrupts critical data and causes the whole program to crash, instead of just crashing silently and dying alone.

Moreover, locks are typically implemented as *advisory* locks, where threads must cooperate to obey the locking protocol. A buggy thread can ignore locks altogether and corrupt the lock-protected data. This makes systems that use locks less tolerant to such bugs.

Because of these problems, programming with locks goes against some of the principles of software engineering. Two of the principles that software engineers rely on are *abstrac-tion* and *composition* [Larus and Rajwar, 2007], principles that help reason about large and complex programs.

Abstraction enables software engineers to manage the complexity of their designs by reducing them to modular components; whereas composition enables them to combine these components into a bigger, more complex, application. These principles allow software engineers to reason about each component separately, without worrying about any adverse interactions these components might have when composed together. Engineers in other fields handle complexity in a similar way. For example, automobile designers do not need to know every single detail about car design, such as how tires are made or the inner workings of a particular engine model. Automobile engineers handle different components individually, abstracting away the details of every component, and then put them together, or compose them, into a car.

Programming with locks breaks abstraction because software engineers need to be aware whether a particular module they are using acquires any locks. If it does acquire a lock, they must ensure that by using it, their program still observes the locking order that prevents deadlock. Otherwise the engineer, by composing two individually correct modules together, could inadvertently cause deadlock, thus breaking composition.

In addition to the software engineering concerns, blocking makes locks unacceptable for use in certain tasks, such as interrupt handlers in an operating system [Ramadan, Rossbach, Porter, Hofmann, Bhandari, and Witchel, 2007]. Interrupt handlers *must* not be blocked by the thread they have interrupted, otherwise the whole system would deadlock. This requirement significantly complicates the design of interrupt handlers in an operating system.

#### **Lock-free Programming**

It is possible, in theory at least, to write correct parallel code without using locks or any other method of mutual exclusion — this is the area of nonblocking synchronization [Herlihy and Shavit, 2008]. Nonblocking synchronization promises that, with a minimum amount of hardware support, it is possible to write parallel algorithms that are guaranteed to complete within a bounded period of time.

The minimum hardware support for nonblocking synchronization is satisfied by a *Compare&Swap* instruction [Herlihy, 1991]. *Compare&Swap* is an atomic instruction that reads a memory location, and if the value at that location matches the value the instruction expects to find, it replaces it with a new value, indicating whether the operation was

successful. *Compare&Swap*, or similar instructions, are available on most modern parallel processors, such as x86 [int, 2010b] and SPARC [Weaver and Germond, 2000]. The code listing below demonstrates the effects of a typical implementation of a *Compare&Swap* instruction.

```

bool CompareAndSwap(int *location, int expected, int update)

{

atomic {

/* appears to the programmer as a single instruction */

if (*location == expected) {

*location = update;

return true;

} else {

return false;

}

}

```

Nonblocking algorithms resolve most of the problems inherent in locks: nonblocking algorithms do not deadlock and are always guaranteed, by definition, to make forward progress. Nonblocking algorithms are fault-tolerant: if a thread executing a non-blocking algorithm crashes or hangs, only that thread is affected, and the rest of the system can continue running. Nonblocking algorithms do not break abstraction or composition; programmers can call any nonblocking algorithms within their critical sections, without having to reason about possible interactions with other parts of their programs. Moreover, nonblocking algorithms are suitable for use in interrupt handlers, because interrupt handlers in a nonblocking system will not be blocked by other threads, including threads they have interrupted.

Unfortunately, nonblocking algorithms that perform well are very difficult to write — more so than writing parallel algorithms with locks [Herlihy and Shavit, 2008]. Writing a nonblocking version of even simple blocking algorithms is often considered to be a publishable result [Larus and Rajwar, 2007].

It is this research into nonblocking algorithms that was the prime motivator for transactional memory. Herlihy and Moss [1993], who coined the term "transactional memory", originally proposed the transactional model specifically to make it easier to write efficient nonblocking algorithms.

### 2.4 What is Transactional Memory?

*Transactional memory* is a programming model that provides an abstraction on top of critical sections for managing accesses to shared data, making it easier to reason about critical sections and allowing them to be composable. Transactional memory uses the concept of a *transaction* [Eswaran, Gray, Lorie, and Traiger, 1976; Gray, 1981], borrowed from the database community [Codd, 1970]. A transaction is defined as "a sequence of actions that appears indivisible and instantaneous to an outside observer" [Larus and Rajwar, 2007]. Using transactional memory, the programmer designates certain critical section code as being *transactional*, and it is the underlying transactional memory implementation's responsibility to ensure that the code runs correctly and efficiently. The programmer, ideally, does not need to consider the ordering of transactions, the size of the transactions, or how different transactions might interact with each other. Instead, programmers merely need to ensure that their code is correct, assuming the transactional component truly appears indivisible and instantaneous.

Towards that end, transactional memory provides *atomicity*, *consistency*, and *isolation* for its component transactions — concepts also borrowed from the database community [Haerder and Reuter, 1983].

Atomicity means that a transaction is indivisible — it is all or nothing. If a transaction succeeds in running to completion, it makes its changes visible only once it *commits*. If for some reason the transaction cannot commit, it *aborts*, and it appears as if nothing has happened, i.e., as if the transaction was never executed in the first place.

Consistency ensures that a transaction must leave the system in a consistent state; it must obey all legal protocols, invariants, and constraints set by the system.

Isolation ensures that the changes made by a transaction are observable only once a transaction commits. It is isolation that is responsible for transactions appearing to be instantaneous; intermediate changes performed by the transaction cannot be observed by any thread outside of the transaction, regardless of whether the other threads are transactional or not. If other threads could view partial modifications, then they might observe an inconsistent state of the system.

Below is a simple example of how the transactional model can be used. To protect a critical section that increments a variable  $\times$  using locks, a programmer would write the following code.

```

lock_acquire(x_lock);

x = x + 1;

lock_release(x_lock);

```

Using the transactional model, a programmer would write the following code.

```

transaction {

x = x + 1;

}

```

In other words, with transactional memory, programmers specify *what* should be protected when running in parallel, and the underlying system deals with the *how*.

A transactional memory system should, for performance reasons, allow multiple transactions to run concurrently as long as they do not *conflict*. A conflict occurs when concurrent transactions access shared data and at least one of them modifies the data [Larus and Rajwar, 2007]. When transactions conflict, the transactional memory system arbitrates and serializes access to the conflicting location, either by stalling or aborting one or more of the conflicting transactions. Aborting a transaction reverts any changes the transaction has made, and it appears as if the transaction never happened. Once a transaction aborts, then depending on the implementation, the system would either try it again — which is the more common approach, or inform the program that the transaction aborted, e.g., by throwing an exception.

### 2.5 Transactional Memory Design Space

The design space of transactional memory covers various areas such as the type of language support necessary for its programming interface, to the different ways of supporting transactions through hardware or software. This section presents some of the points in the design space that are relevant to this thesis.

At the highest level, there is the issue of how to expose the transactional memory abstraction to the programmer. Some researchers have proposed additions and extensions to existing languages to support transactional memory, such as adding the transaction keyword to the C++ programming language [Adl-Tabatabai, Lewis, Menon, Murphy, Saha, and Shpeisman, 2006a]. Others argue that, because programmers are familiar with the locking model, systems should retain that model at the high level and elide those locks using transactional support; a technique known as *speculative lock elision* [Rajwar and Goodman, 2001]. The work presented in this thesis is mainly concerned with the underlying implementation of a transactional system, and is independent of its programming interface.

Another aspect of transactional design is related to conflict detection between transactions. First, there is the issue of the level of *granularity* of conflict detection. This can range from being a single word, a cache line, or a whole (high-level) object. Granularity is typically governed by the type of support the system is using. Hardware proposals typically have a granularity level of a cache line, because, as will be explained later, hardware proposals often leverage the underlying cache coherence protocol for conflict detection. Software transactional memory proposals typically detect conflicts at a granularity level of a word or an object. Bigger granularity makes it easier to amortize some of a transaction's overhead, but increases the chance of *false conflicts* due to different transactions accessing disjoint parts of the same granularity unit.

Another issue with conflict detection is when to *detect* and when to try to *resolve* a conflict between transactions. Some systems *eagerly* detect conflicts as soon as two or more transactions appear to access the same data in a conflicting manner, whereas other systems *lazily* delay conflict detection until one of the transactions is ready to commit.<sup>1</sup> As with many design alternatives, the better design choice is not obvious. For example, a transaction using eager conflict detection could abort a conflicting transaction, only to discover later that it is itself *doomed* and cannot commit because of conflicts with other transactions. On the other

<sup>&</sup>lt;sup>1</sup>Eager conflict detection is analogous to pessimistic concurrency control in database management systems, whereas lazy conflict detection is analogous to optimistic concurrency control [Larus and Rajwar, 2007].

hand, lazy conflict detection could allow a doomed transaction, which is going to eventually have to abort because of other conflicts, to continue running wasting work and resources, when eager conflict detection would already have aborted it.

Once a transactional system detects a conflict, there is the issue of conflict management and resolution. When transactions conflict with each other, there is a winner, who gains access to the data. There is also a loser, who must wait for the winner to either commit or abort. The loser waits either by stalling or aborting. Conflict management deals with the heuristics that determine a transaction's priority to decide which transaction wins when there is a conflict.

Versioning is another issue in transactional memory system design, and is concerned with maintaining information so the system can undo any modifications an aborted transaction has made. One option is for a transaction to update objects in-place, and keep a backup copy of the old data. An alternative is for a transaction to buffer its updates, applying them only when it knows that it will commit successfully.

One of the most important design issues, an issue that could directly affect other design decisions, is the type of underlying support for a transactional system. Following is a discussion of the different proposed methods to support transactional memory: hardware, software, and a hybrid combination of the two.

### Hardware Transactional Memory

Hardware transactional memory proposals are classified as *best-effort* [Moir, 2005], *bounded*, and *unbounded* [Larus and Rajwar, 2007].

Best-effort hardware transactional memory [e.g., Herlihy and Moss, 1993; Rajwar and Goodman, 2001; Chaudhry, Cypher, Ekman, Karlsson, Landin, Yip, Zeffer, and Tremblay, 2009a] does not guarantee that all transactions will eventually commit successfully using hardware support alone. One of the main limitations of best-effort proposals is the size and associativity of a processor's local cache memory.

Best-effort hardware proposals rely on the underlying cache memory and cache coherence protocol. Cache memory can, with little or no adjustment, perform automatic versioning of data modified in a transaction. Write-back cache memory keeps the modified copy of a cache line in a processor's local cache, until the processor writes it back to memory or shares it with other processors; therefore, the original copy is still intact either in main memory, or in another processor's cache [Larus and Rajwar, 2007]. This simplifies aborting a transaction: to undo a transaction's modifications, a processor discards all cache lines modified during the transaction.

Cache coherence also facilitates conflict detection between transactions. Coherence protocols, by design, notify a processor of conflicting accesses to memory locations in its cache by other processors. To support conflict detection in transactional memory, each processor tracks which cache lines it has accessed as part of a transaction, and infers transactional conflicts from coherence conflicts for cache lines accessed as part of the transaction.

Best-effort proposals typically add a bit to each cache line in a processor's local cache to track the lines accessed as part of a transaction. Best-effort proposals maintain atomicity and isolation by ensuring that modifications to those cache lines are not exposed, through the coherence protocol, until the transaction commits. If a transaction aborts, the processor discards all lines modified inside the transaction — implicitly rolling back these modifications. If a transaction commits, the processor ensures that all modified lines are instantly visible to others by immediately exposing those lines through the cache coherence protocol.

Because best-effort hardware transactional memory relies on the processor's local cache to maintain its transactional state, any event that invalidates or evicts a cache line that has been accessed as part of the current transaction also results in aborting the transaction. Without additional hardware support, a transaction cannot track the state of an evicted cache line, and therefore cannot observe if other transactions access the evicted line in a conflicting manner.

Bounded hardware transactional memory proposals [e.g., Hammond, Wong, Chen, Carlstrom, Davis, Hertzberg, Prabhu, Wijaya, Kozyrakis, and Olukotun, 2004; Ananian, Asanovic, Kuszmaul, Leiserson, and Lie, 2005; Moore, Bobba, Moravan, Hill, and Wood, 2006] guarantee that certain transactions will eventually commit successfully using hardware support alone. Bounded proposals typically behave in the same way as best-effort ones, as long as cache memory resources are sufficient. When the resources are not sufficient, e.g., a transaction encounters an event that invalidates or evicts a transactional cache line, bounded proposals rely on additional hardware mechanisms and data structures that reside in main memory to continue tracking the transactional state.

Bounded proposals are not restricted by the size and associativity of cache memory; however, they cannot commit transactions that encounter events that are too complicated to handle in hardware — events that best-effort proposals cannot handle either. Whether an event is too complicated to handle in hardware depends on the particular proposal. Examples of such events include context switches, thread migration, virtual memory paging, I/O, exceptions, and interrupts [Hofmann, Porter, Rossbach, Ramadan, and Witchel, 2007]. When a transaction encounters such an event, it aborts.

Unbounded hardware transactional memory proposals [e.g., Ananian et al., 2005; Rajwar, Herlihy, and Lai, 2005] guarantee that all transactions would eventually commit, regardless of their size or the events they may encounter. Therefore, unbounded proposals must be able to handle any event without indefinitely aborting the same transaction. Having to handle all types of events adds more complexity to the hardware than in bounded proposals.

#### Software Transactional Memory

Software transactional memory does not use any hardware support beyond what is already available for concurrent programming. Software transactional memory proposals, therefore, must rely on software structures for versioning and conflict management.

A simple software transactional memory could be implemented using a single global lock that serializes all transactions. Such an implementation requires no additional data structures for versioning, because every transaction, once it has acquired the single lock, is guaranteed to succeed. Without additional hardware support, using a single global lock does not scale; however, such a system has low overhead, which might be acceptable if there are not many transactions.

Practical software proposals usually allow concurrency between transactions. Such proposals use more elaborate methods for conflict detection and resolution than a single global lock, and rely on a variety of versioning schemes to rollback aborted transactions.

For versioning, a software system could maintain a write set, where it stores all tentative writes of a particular transaction, committing those writes to memory once it knows the transaction is guaranteed to commit. Another option would be to maintain an undo log, or a backup copy, of the modified locations. If a transaction aborts, then the aborted transaction, or other transactions, can access the undo logs to restore the original data.

For conflict detection, software proposals often create and associate *ownership records* with each location, or group of locations, that could be accessed inside a transaction. An ownership record can refer to a single word in memory and reside in a hash table, or it can refer to a whole object and reside in its header. Therefore, before a transaction can commit, it must check the ownership record of every location it has accessed and resolve any conflicts. Moreover, a transaction must acquire a location's ownership record before it can commit its modifications of that location's data to ensure that only one transaction can modify the data at the same time.

If a transaction discovers that a location is acquired by another transaction, there is a conflict. A transaction can wait until the competing transaction has either committed or aborted, and has thereby relinquished ownership of the location. Otherwise, the transaction can abort the competing transaction and forcibly acquire ownership of the location.

The decision on whether to wait for or to abort the competing transaction is typically not hardwired into the software transactional memory algorithm, but determined by consulting a *contention manager* module [Herlihy, Luchangco, Moir, and Scherer, 2003b], which may apply different conflict resolution policies. The contention manager is often implemented as an *out-of-band* module [Herlihy et al., 2003b], where its policy and logic are independent from the underlying algorithm. Therefore, an out-of-band contention manager can implement various policies and conflict resolution schemes without affecting the correctness of the software transactional memory.

Transactions that only read a location do not necessarily need to acquire ownership of that location. Using *invisible reads*, a transaction can detect conflicts by *validating*, before a transaction commits, that a location has not been modified since the transaction has read it.

A transaction can validate by checking that the location's ownership record has not changed since it last read it, because for another transaction to modify the data it must also have modified the location's ownership record. A transaction can also validate by comparing the current data value of the location with the value it has used previously. If the value has not changed, then as far as the transaction is concerned, no other transactions have modified this location in the interim, and no conflicts have occurred. This is known as *value-based* conflict detection [Ding, Shen, Kelsey, Tice, Huang, and Zhang, 2007; Olszewski, Cutler, and Steffan, 2007].

As an alternative to invisible reads, transactions could use read ownership records, or *visible reads*, for conflict detection. A transaction that reads a location adds itself to a readers list associated with that location. Any transaction that wants to modify the location must check this readers list and resolve all conflicts before it can commit.

Software transactional memory algorithms can be either blocking or nonblocking. Nonblocking software transactional memory, like nonblocking algorithms in general, are more complex and challenging to write. Some have even argued that nonblocking software transactional memory algorithms are inherently slow and should not even be considered [Ennals, 2006]. Chapter 4 presents my response to this argument.

Because software transactional memory proposals must perform these additional tasks in software, compared with hardware transactional memory, the overhead of software transactional memory is quite high, as explained in the next chapter. Software proposals can be an order of magnitude slower than hardware for some workloads. Software transactional memory can be designed with low overhead; the simple system based on a single global lock described earlier is an example of that. However, such systems do not scale without additional hardware support.

#### **Hybrid Transactional Memory**

Hybrid transactional memory uses both hardware and software for its underlying implementation. The goal of hybrid transactional memory is the flexibility of software and the performance of hardware, while requiring hardware support that is considered to be realistic and feasible to implement.

Hybrid transactional memory design can begin with a software transactional memory, and use hardware support to optimize its bottlenecks. Hybrid design could also begin with a hardware transactional memory, and use software to handle the corner cases and complicated aspects that hardware cannot feasibly handle. A special case of this approach, highlighted because of its relevance to this thesis, is when a hybrid system attempts a transaction using best-effort hardware transactional memory, and falls back on a software transaction when the hardware transaction (repeatedly) aborts [Lie, 2004; Moir, 2005].

For performance, it is important that a hybrid system run as many transactions as possible using the fast hardware path, and avoid using the slower software path. For correctness, a hybrid system must detect and correctly handle conflicts between transactions that could be running using hardware or software support.

In a hybrid system that uses best-effort hardware and falls back on software, hardware transactions automatically detect conflicts with any software accesses that follow hardware accesses. This is a direct result of hardware transactions relying on the cache coherence protocol for conflict detection. However, software transactions do not automatically detect conflicts with hardware transactions when a hardware transaction accesses an object *after* the software transaction does, because hardware transactions, by design, are a low level system abstraction whose effects are isolated from software until the hardware transaction commits. Therefore, the burden is on hardware transactions to ensure that the data they access is not being accessed by a concurrent software transaction in a conflicting way. This checking could be instrumented as part of the hardware transaction's code, but adds overhead to hardware transactions in this type of hybrid system.

# 2.6 Evaluating Transactional Memory

One of the challenges in transactional memory pertains not to the design of a transactional system, but to evaluating how well it performs. The problem with evaluating transactional systems is that the transactional model is new, so there are few existing applications that use this model.

Many of the first transactional systems evaluated their proposals using a set of synthetic and microbenchmarks created specifically for the purpose of testing transactional memory proposals [Herlihy et al., 2003b; Marathe, Spear, Heriot, Acharya, Eisenstat, Scherer, and Scott, 2006]. These benchmarks, as with any synthetic benchmark, do not represent realistic workloads.

Later transactional proposals used some of the older and well-established benchmarks, such as the SPLASH-2 benchmark suit [Woo, Ohara, Torrie, Singh, and Gupta, 1995], for their evaluation, by converting the benchmarks' critical sections to use transactions instead of locks [Moore et al., 2006]. The problem with this approach is that critical sections written for the mutually-exclusive locking model are optimized by experts to be small and have as little shared data as possible. This type of workload is not necessarily representative of how transactions might be used by the average programmer.

A few research groups proposed new benchmarks to fill the gap. One of the most comprehensive benchmark suite designed for evaluating transactional memory is the STAMP benchmark suite [Minh, Chung, Kozyrakis, and Olukotun, 2008]. The STAMP benchmarks use different types of algorithms and exhibit different transactional characteristics in terms of transaction length, conflict rates, and size of the read and write sets. Because of STAMP's broad coverage, it is the most widely used benchmark suit for evaluating transactional systems. STAMP, however, is written by experts on parallel programming. Although some of its workloads represent realistic applications, the programming style is not necessarily representative of how the average programmer might use the transactional model.

To cover a wider variety of workloads, the evaluations presented in this thesis use a combination of synthetic benchmarks I have developed, microbenchmarks, SPLASH-2 benchmarks, and STAMP benchmarks. Benchmarks are seldom comprehensive or conclusive, but using a variety of benchmarks helps develop better intuition of the performance of the evaluated systems.

### 2.7 The Current State of Transactional Memory

This section explores the current state of transactional memory and the progress it has made towards becoming a mainstream model. It looks at transactional memory in production systems and in systems that are being tested for production use.

For hardware transactional memory, as far as I am aware, the only two attempts of supporting hardware transactional memory in a commercial processor are by Sun Microsystems and Azul Systems.

In 2007, Sun Microsystems announced a new processor, codenamed *Rock*, which as of yet has not been released to the public [Chaudhry et al., 2009a].<sup>2</sup> Rock's design was a departure from Sun's Niagara family of processor. The Niagara family of processors comprises a group of simple cores designed for high throughput applications such as web servers. Rock was designed as a high-performing floating-point intensive processor. Each Rock processor has 16 cores, each core capable of running two threads. One of the new features in Rock is that it performs aggressive speculation, which Sun leveraged to support best-effort hardware transactional memory. I used a Rock prototype for part of the evaluation presented in this thesis. Rock's best-effort hardware, and the particulars of the prototype used, are discussed in the next section.

Azul Systems is a privately-held company that manufactures specialized *computer appliances* that run Java-based applications [Click, 2009c]. Their Vega 3 series computer has 864 cores, and is designed for high throughput and scalability. Azul's processor implements a best-effort hardware transactional memory, which they use to elide locks in the Java Virtual Machine [Click, 2009a,b]. Because Azul's hardware is best-effort, when a hardware transaction aborts a certain number of times, the system falls back on acquiring the Java lock it had attempted to elide.

<sup>&</sup>lt;sup>2</sup>It is likely that Rock has been cancelled [Vance, 2009], although Sun has neither confirmed nor denied this yet.

Azul's hardware transactional memory uses the first level (L1) cache as its transactional cache, adding two bits per cache line to track the lines that have been read or modified as part of a transaction. Therefore, hardware transactions are limited by the size and associativity of the L1 cache. A transaction aborts if a cache line it has accessed speculatively is invalidated or evicted from the cache, either because of a conflict with another processor, or if the L1 cache is not large enough to hold all the transactional data.

Even though hardware transactional memory was first proposed in 1993 [Herlihy and Moss, 1993], only two actual implementations exist today, Sun's and Azul's. Neither are on a commercially-available general purpose computer, and both are best-effort. This shows that implementing hardware support for transaction — and unbounded support in particular — is difficult, at least in the sense that processor manufacturers believe that the cost/benefit tradeoff does not yet justify any hardware implementation that goes beyond best-effort.

When it comes to software transactional memory, the only production-quality compiler that supports it is the Glasgow Haskell Compiler, the main compiler for the Haskell programming language [Perfumo, Sönmez, Stipic, Unsal, Cristal, Harris, and Valero, 2008; ghc, 2010]. Haskell is a pure functional programming language, which by default does not allow mutable variables. Therefore, it can more easily accommodate transactional memory: the language is defined so mutable variables can be accessed only inside transactions [Harris, Marlow, Peyton-Jones, and Herlihy, 2005].